#### Rev B1, Page 1/72

#### FEATURES

- Separate and independent 2-channel scanning

- Control/Safety Channel scan different positions of the code disc

- Fixed code disc diameters of 26.5 mm or 42.5 mm

- ♦ Control Channel (CC) features:

- ♦ 10-bit Pseudo-random Code (PRC)

- ◆ 5-bit real-time interpolator (1024 CPR sine/cosine)

- Auxiliary sine/cosine scanning with differential analog outputs

- ♦ BiSS interface

- ♦ MT interface (SSI)

- Pin-selectable modes of operation

- Diagnostics (e.g Sin/Cos DC monitor)

- ♦ Safety Channel (SC) features:

- ♦ 10-bit Pseudo-random Code (PRC)

- ♦ 5-bit real-time interpolator (1024 CPR sine/cosine)

- BiSS/SPI interface

- ♦ MT interface (SSI)

- ♦ Configuration via BiSS, SPI and I<sup>2</sup>C from ext. EEPROM

- Diagnostics (e.g Sin/Cos AC monitor)

- On-chip temperature sensor

#### APPLICATIONS

- High-resolution optical encoder for external interpolation (up to 24 bits using iC-MR3)

- Functional Safety Encoder

#### PACKAGES

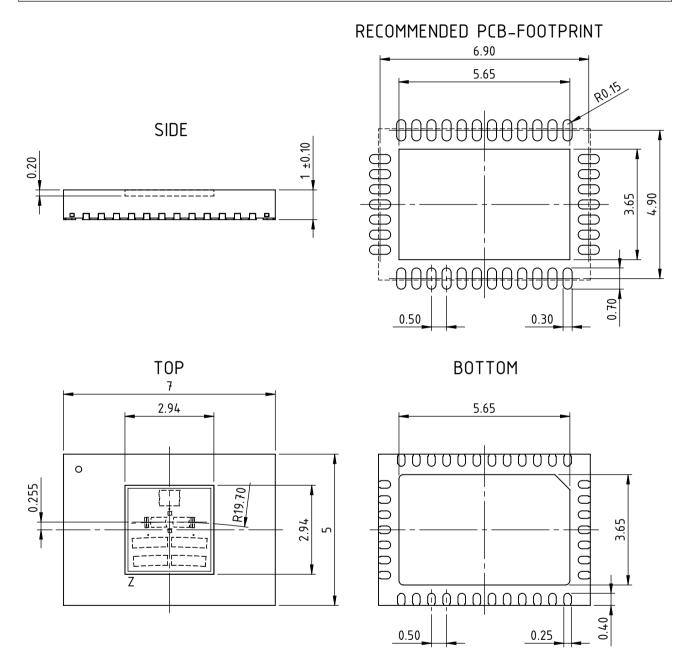

38-pin optoQFN 7.0 mm x 5.0 mm x 1.0 mm RoHS compliant

Rev B1, Page 2/72

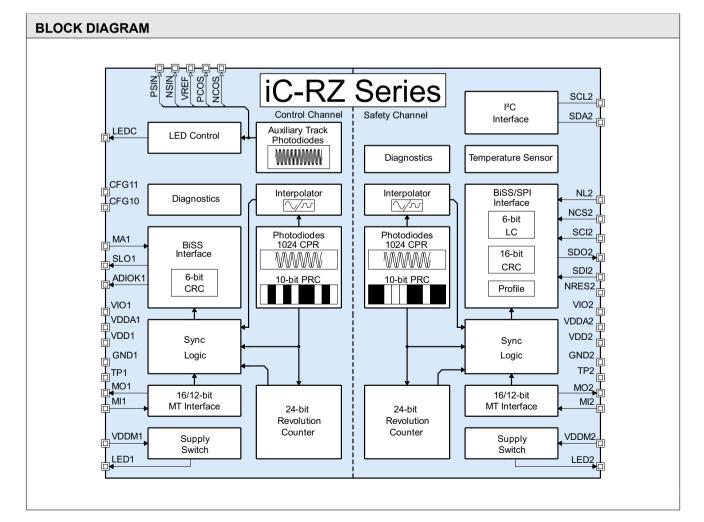

#### DESCRIPTION

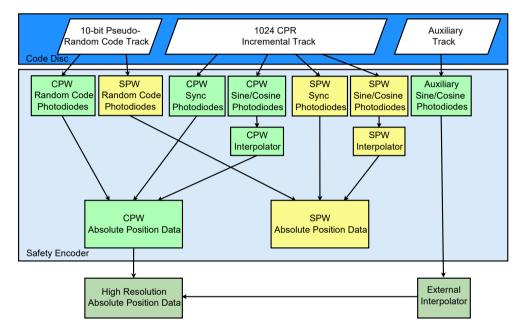

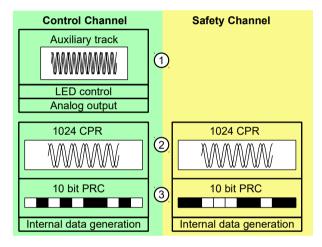

iC-RZ is an advanced optical sensor IC for transmissive encoders, with integrated photodiodes for reliable and redundant scanning of a code disc with 3 different tracks:

- 1. Incremental track (1024 CPR sine/cosine)

- 2. Pseudo-random Code track (10-bit PRC)

- 3. Auxiliary track (AT) (sine/cosine CPR is determined by the device version)

To do this, the iC-RZ is divided into two autonomous channels called Control Channel (CC) and Safety Channel (SC).

The Control Channel generates a 15-bit absolute position value by scanning the absolute 10-bit PRC track and the incremental track (1024 CPR sine/cosine). In doing so, the scanning of the PRC is synchronized with the 1024 CPR sine/cosine signals, which are further resolved by a 5-bit real-time interpolator.

The Safety Channel operates in exactly the same way, meaning that position data generation is fully redundant: the Control Channel generates the Control Position Word (CPW), and the Safety Channel the Safety Position Word (SPW).

The absolute position value of the CPW is output via a serial BiSS Interface using a 6-bit CRC. This data matches in phase with the sine/cosine signals generated from the auxiliary track, which are output as voltage signals over low-impedance buffers. It is therefore possible to increase the resolution of the CPW by connecting an external interpolator, preferably iC-MR3, featuring signal-conditioning to increase the position accuracy.

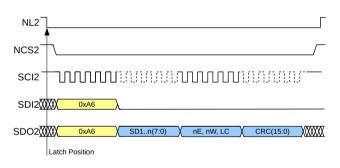

The absolute position value of the SPW is output via a serial BiSS/SPI Interface using a 16-bit CRC and 6-bit sign-of-life counter (LC). A standard SSI output is also possible, but without nE, nW, CRC and LC.

Each channel uses its absolute 10-bit PRC track photodiodes to capture and count revolutions (embedded 24-bit revolution counter). These revolution counters can be supplied from an independent external energy source (e.g. a battery).

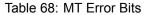

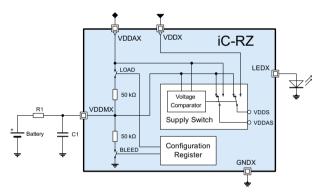

An optional multiturn value (12 bit or 16 bit) can be read by the Control Channel and the Safety Channel through the MT interface of each channel, using the SSI protocol. This multiturn data is synchronized to the internally generated singleturn absolute value.

All integrated photodiodes used for the incremental scanning of sine/cosine signals are arranged as an *HD Phased Array*, providing excellent signal fidelity at relaxed alignment tolerances.

For safety-related applications the appropriate Safety Implementation Manual has to be considered.

**General notice on materials under excessive conditions** Epoxy resins (such as solder resists, IC package and injection molding materials, as well as adhesives) may show discoloration, yellowing, and general surface changes when exposed long-term to high temperatures, humidity, irradiation, or due to thermal treatments for soldering and other manufacturing processes.

Equally, standard molding materials used for IC packages can show visible changes induced by irradiation, among others when exposed to light of shorter wavelengths, for instance, blue light. Such surface effects caused by visible or IR LED light are rated to be of cosmetic nature, without influence on the chip's function, its specifications or reliability.

Note that any other materials used in the system (e.g. varnish, glue, code disc) should also be verified for irradiation effects.

#### General notice on application-specific programming

Parameters defined in the datasheet represent supplier's attentive tests and validations, but - by principle - do not imply any warranty or guarantee as to their accuracy, completeness or correctness under all application conditions. In particular, setup conditions, register settings and power-up have to be thoroughly validated by the user within his specific application environment and requirements (system responsibility).

The chip's performance in application is impacted by system conditions like the quality of the optical target, the illumination, temperature and mechanical stress, sensor alignment and initial calibration.

Rev B1, Page 3/72

#### CONTENTS

| PACKAGING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| PIN CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| oQFN38-7x5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  |

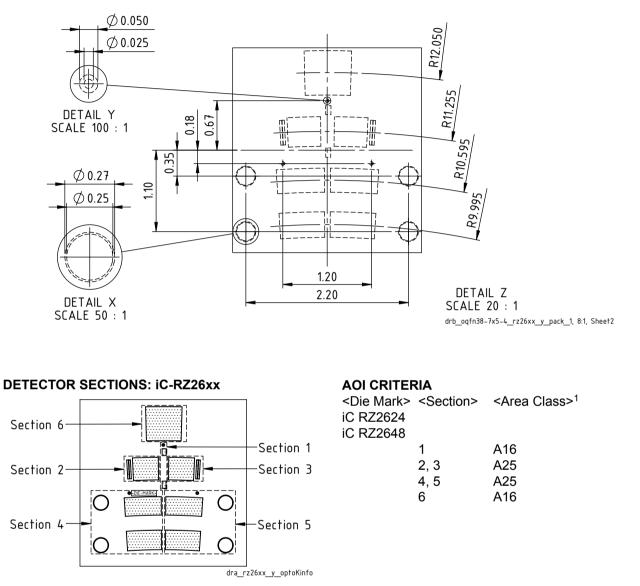

| PACKAGE DIMENSIONS :iC-RZ26xx<br>oQFN38-7x5                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

| LAYOUT DETAILS: iC-RZ26xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

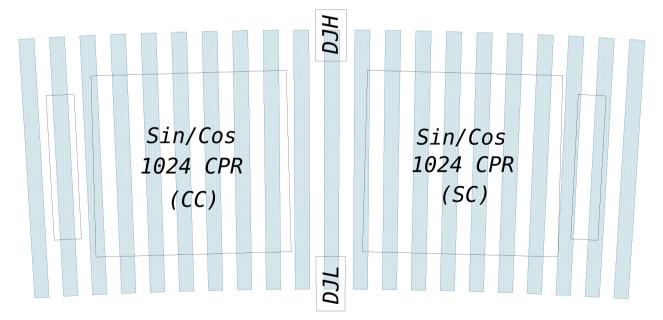

| DETECTOR SECTIONS: iC-RZ26xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7  |

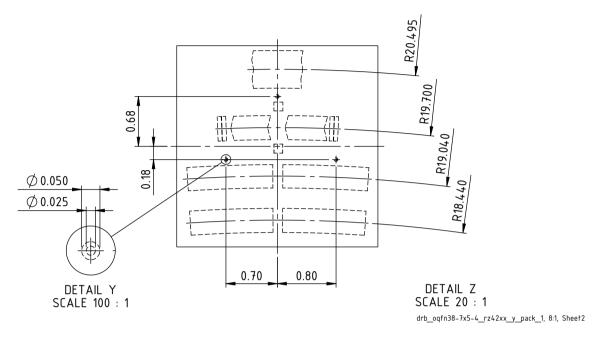

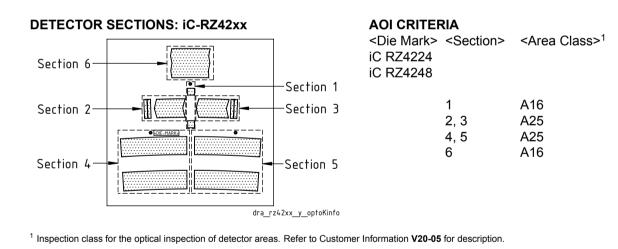

| PACKAGE DIMENSIONS :iC-RZ42xx<br>oQFN38-7x5                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9  |

| DETECTOR SECTIONS: iC-RZ42xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10 |

| PACKAGE DIMENSIONS ::C-RZ42xx<br>oQFN38-7x5<br>LAYOUT DETAILS: iC-RZ42xx<br>DETECTOR SECTIONS: iC-RZ42xx<br>DETECTOR SECTIONS: iC-RZ42xx<br>ABSOLUTE MAXIMUM RATINGS<br>THERMAL DATA<br>ELECTRICAL CHARACTERISTICS<br>OPERATING REQUIREMENTS<br>BISS, SSI Interface<br>SPI Interface<br>SPI Interface<br>I <sup>2</sup> C Interface<br>I <sup>2</sup> C Interface<br>Control Channel (CC)<br>Safety Channel (SC)<br>Control Channel<br>Safety Channel<br>Safety Channel<br>Safety Channel<br>Safety Channel | 10 |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 |

| OPERATING REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

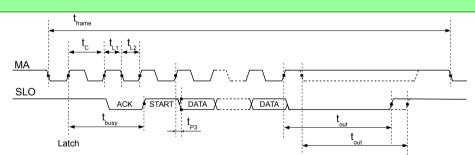

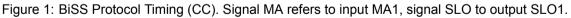

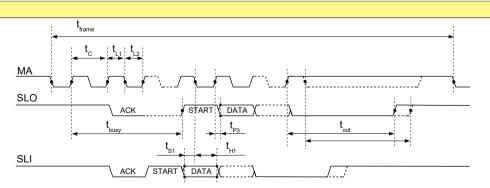

| BiSS, SSI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 |

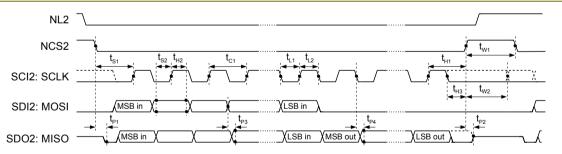

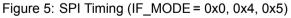

| SPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 |

| MT Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

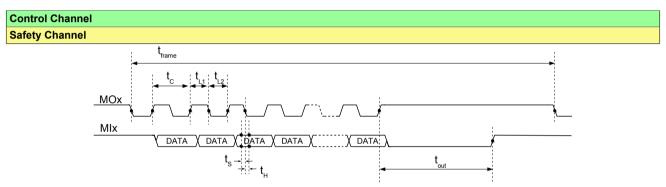

| I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19 |

| SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20 |

| Control Channel (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 |

| Safety Channel (SC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21 |

| I/O PIN OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

| Control Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21 |

| Safety Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

| CONFIGURATION PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22 |

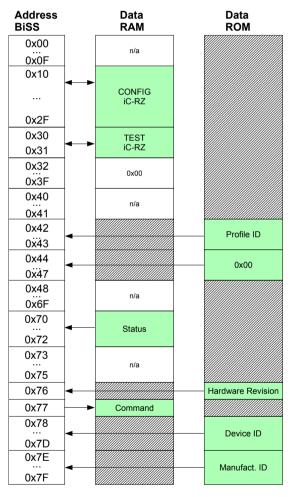

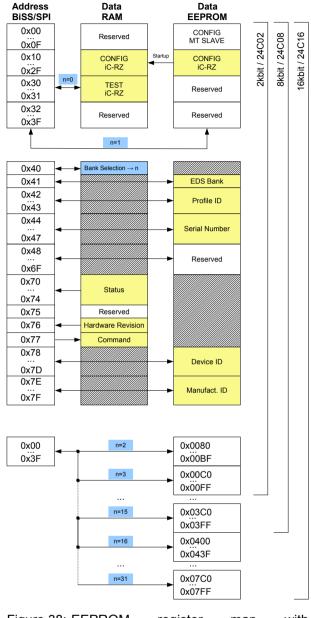

| REGISTER MAP (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |

| REGISTER MAP (SC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |

| PHOTODIODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27 |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |

| Auxiliary track photodiodes with differential analog outputs (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |

| Incremental track photodiodes for the internal                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 5-bit interpolator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

| PRC track photodiodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 |

| LED CONTROL (CC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

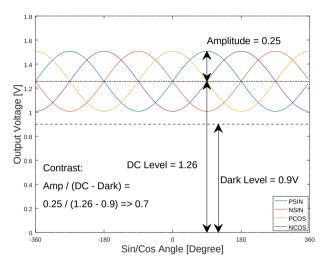

| STARTUP PROCESS 29                              |

|-------------------------------------------------|

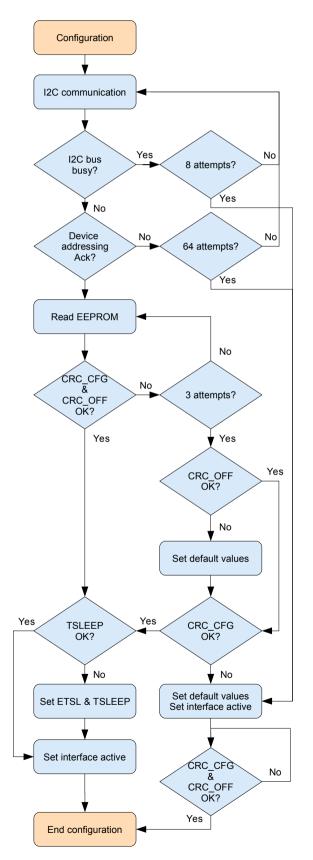

| Configuration of Control Channel 29             |

| Configuration of Safety Channel 31              |

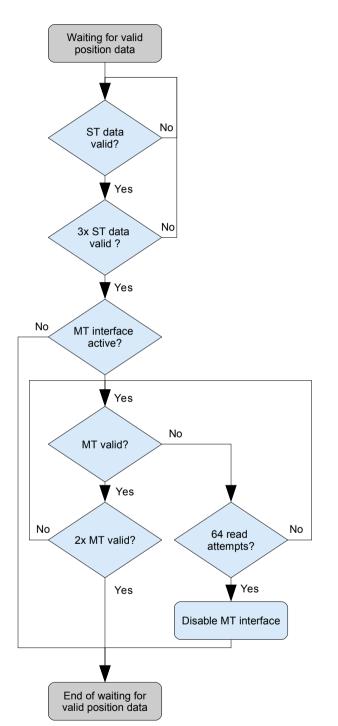

| Position data initialization                    |

|                                                 |

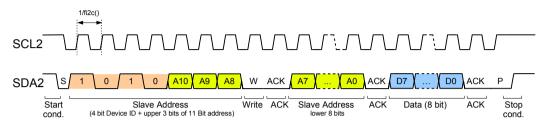

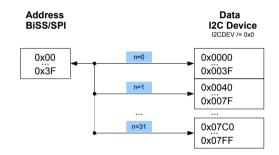

| I2C INTERFACE (SC) 33                           |

| General                                         |

| CRC: General and Output Format Configuration 33 |

| SERIAL I/O INTERFACES 35                        |

| Control Channel                                 |

|                                                 |

| Safety Channel                                  |

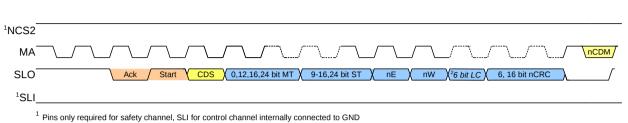

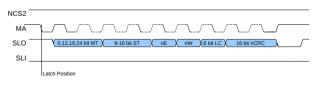

| BISS INTERFACE 36                               |

| Overview                                        |

| BiSS protocol commands                          |

| Control Channel                                 |

|                                                 |

| Safety Channel                                  |

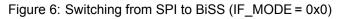

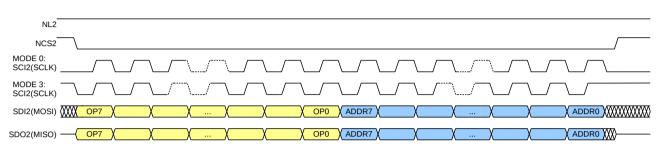

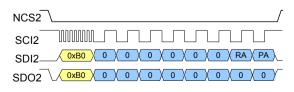

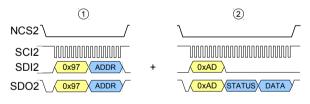

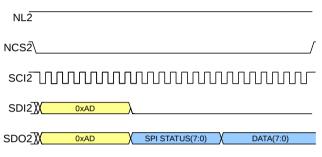

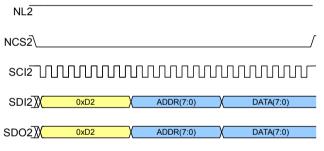

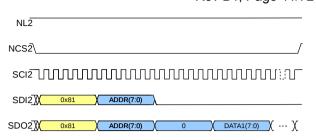

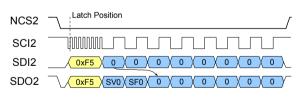

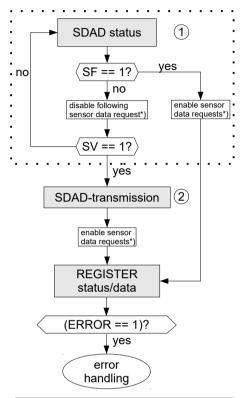

| SPI INTERFACE (SC) 39                           |

| SPI Protocol                                    |

| Opcode ACTIVATE                                 |

| Opcode Read REGISTER (single)                   |

| Opcode REGISTER status/data                     |

|                                                 |

|                                                 |

| Opcode Read REGISTER (cont.) delayed 41         |

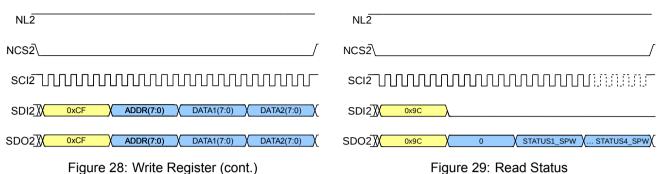

| Opcode Write REGISTER (cont.) 41                |

| Opcode Read STATUS 42                           |

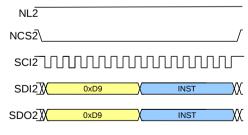

| Opcode Write INSTRUCTION 42                     |

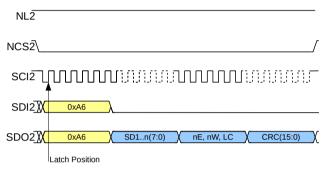

| Opcode SDAD-transmission 42                     |

| Opcode SDAD status                              |

|                                                 |

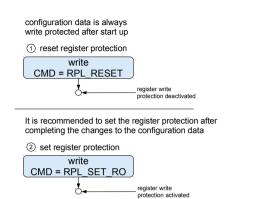

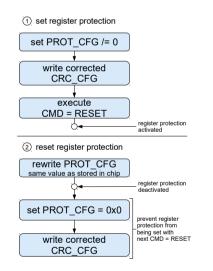

| REGISTER ACCESS 45                              |

| Control Channel: BiSS 45                        |

| Safety Channel: Overview and register           |

| protection                                      |

| Safety Channel: SPI and BiSS 46                 |

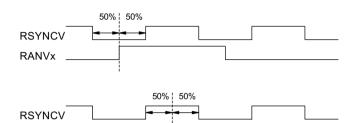

| SYNCHRONIZATION LOGIC 48                        |

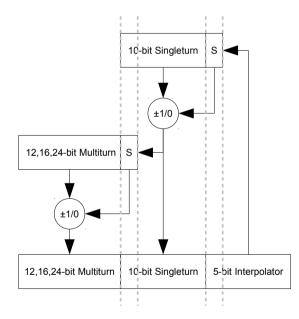

| Position Data Generation                        |

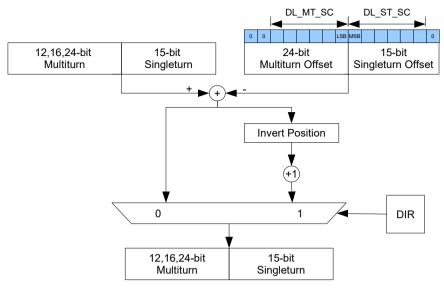

| Safety Channel: Offset                          |

|                                                 |

| MULTITURN FUNCTIONS 50                          |

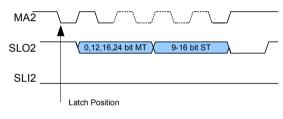

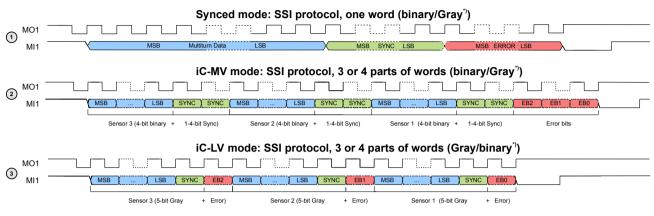

| MT Interface: SSI Overview 50                   |

| Multiturn Configuration: Control Channel 51     |

| Multiturn Configuration: Safety Channel 53      |

| •                                                  |    |

|----------------------------------------------------|----|

| DIAGNOSTICS SC                                     | 62 |

| Amplifier Limit Monitor                            | 62 |

| Sin/Cos AC Monitor                                 | 62 |

| Interpolator Plausibility Check                    | 62 |

| PRC Plausibility Check                             | 62 |

| Multiturn Interface Protocol                       | 62 |

| Multiturn Plausibility Check                       | 62 |

| 24-bit Revolution Counter                          | 62 |

| Temperature Monitor                                | 62 |

| Configuration                                      | 63 |

| Internal Test Modes                                | 63 |

| Status Registers                                   | 63 |

| BiSS, EXTSSI, SPI: Error and Warning bits<br>nE/nW | 64 |

| Pin NRES2                                          | 65 |

| COMMANDS                                           | 66 |

| Control Channel                                    | 66 |

| Safety Channel                                     | 67 |

| ALIGNMENT                                          | 68 |

| Control Channel                                    | 68 |

| Safety Channel                                     | 69 |

| DESIGN REVIEW: Notes On Chip Functions             | 70 |

| REVISION HISTORY                                   | 71 |

Rev B1, Page 4/72

Rev B1, Page 5/72

#### PACKAGING INFORMATION

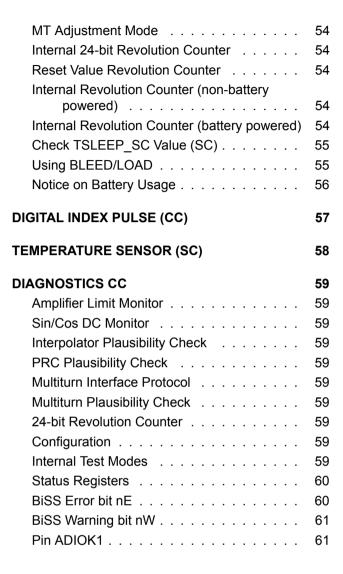

#### **PIN CONFIGURATION** oQFN38-7x5

#### **PIN FUNCTIONS**

#### Function No. Name

- Cosine Output, negative (CC<sup>3</sup>) 1 NCOS

- 2 PCOS Cosine Output, positive (CC)

- Reference Voltage Output (CC) VREF 3

- **PSIN** Sine Output, positive (CC) 4

- 5 NSIN Sine Output, negative (CC)

- TP1 Test Input 1 (CC) 6

- Status Output<sup>6</sup> (CC) 7 ADIOK1

- MT Interface, clock output (CC) 8 MO1

- MT Interface, data input (CC) 9 MI1

#### Configuration Input 1 (CC) 10 CFG11

## 11 CFG10 Configuration Input 0 (CC)

Function

**PIN FUNCTIONS**

No. Name

| 12 | MA1               | BiSS Interface, clock input (CC)                          |

|----|-------------------|-----------------------------------------------------------|

| 13 | SLO1              | BiSS Interface, data output (CC)                          |

| 14 | SCL2              | I <sup>2</sup> C Interface, clock line (SC <sup>4</sup> ) |

| 15 | SDA2              | I <sup>2</sup> C Interface, data line (SC)                |

| 16 | SDO2              | BiSS/SPI Interface, data output (SC)                      |

| 17 | SCI2              | BiSS/SPI Interface, clock input (SC)                      |

| 18 | SDI2              | BiSS/SPI Interface, data input (SC)                       |

| 19 | n.c. <sup>1</sup> |                                                           |

| 20 | NCS2              | SPI Interface, chip select input <sup>2</sup> (SC)        |

| 21 | NL2               | SPI Interface, latch input <sup>2</sup> (SC)              |

| 22 | MI2               | MT Interface, data input (SC)                             |

| 23 | MO2               | MT Interface, clock output (SC)                           |

| 24 | NRES2             | REBOOT input/indication output (SC)                       |

| 25 | TP2               | Test Input 2 (SC)                                         |

| 26 | VIO2              | +2.5 V+5 V I/O Supply Voltage <sup>7</sup> (SC)           |

| 27 | VDDM2             | +3V+5V MT Supply Voltage <sup>8</sup> (SC)                |

| 28 | VDDA2             | +5 V Analog (Supply Voltage <sup>7</sup> SC)              |

| 29 |                   | +5 V Digital Supply Voltage <sup>7</sup> (SC)             |

| 30 | GND2              | Ground (SC)                                               |

| 31 | LED2              | LED Flashing Output <sup>5</sup> (MT) (SC)                |

|    | LED1              | LED Flashing Output <sup>5</sup> (MT) (CC)                |

| 33 | GND1              | Ground (CC)                                               |

| 34 | VDD1              | +5 V Digital Supply Voltage <sup>7</sup> (CC)             |

| 35 | VDDA1             | +5 V Analog Supply Voltage <sup>7</sup> (CC)              |

| 36 | LEDC              | LED Control Output <sup>5</sup> (CC)                      |

| 37 | VDDM1             | +3V+5V MT Supply Voltage <sup>8</sup> (CC)                |

| 38 | VIO1              | +2.5 V+5 V I/O Supply Voltage <sup>7</sup> (CC)           |

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes);

<sup>1</sup> Pin numbers marked n.c. are not connected.

<sup>2</sup> Pin is low active.

<sup>3</sup> CC: Control Channel Grounding all channel pins should be considered if not in use.

<sup>4</sup> SC: Safety Channel Grounding all channel pins should be considered if not in use.

<sup>5</sup> High-side current source output. If the battery-buffered MT function is not in use, connect LED1 to GND1, respectively LED2 to GND2.

<sup>6</sup> Open-drain output

Supply voltage input must be blocked with a capacitor of at least 100 nF close to the chip's supply terminals.

<sup>8</sup> Supply voltage input must be blocked with a capacitor of at least 1 µF close to the chip's supply terminals. If the battery-buffered MT function is not in use, connect VDDM1 to VDDA1, respectively VDDM2 to VDDA2. Refer to footnote 5 for LED1, and LED2.

To better EMI immunity, unused pins should be wired externally according to the built-in pull-up/pull-down.

TP1/2 must be connected to GND1/2. GND1 and GND2 must be connected to each other

The thermal pad of the oQFN package (bottom side) must be connected by a single link to GND1 or GND2. A current flow across the paddle is not permissible.

Rev B1, Page 6/72

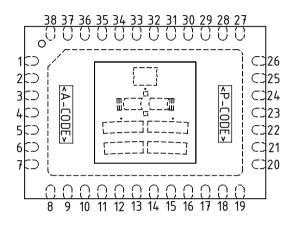

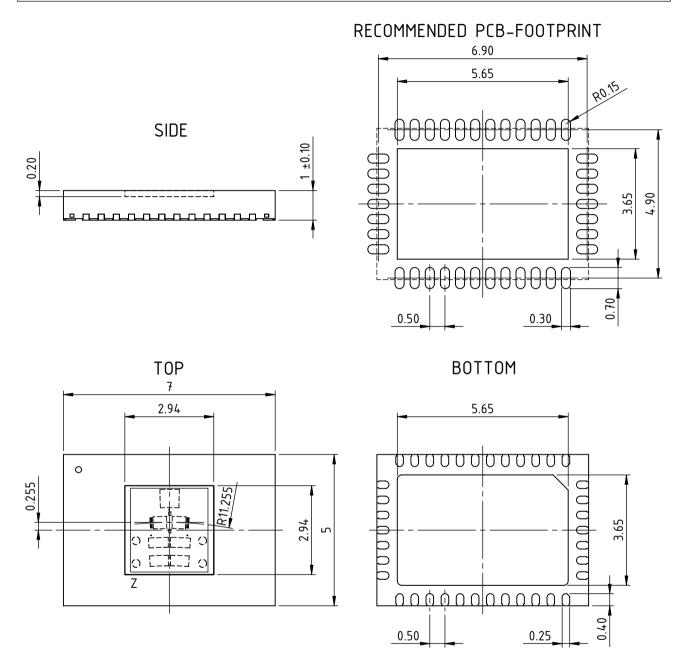

#### PACKAGE DIMENSIONS : iC-RZ26xx oQFN38-7x5

All dimensions given in mm. General tolerances of form and position according to JEDEC MO-220. Positional tolerance of sensor pattern:  $\pm 70\mu$ m /  $\pm 0.6^{\circ}$  (with respect to center of backside pad). Maximum molding excess  $\pm 10\mu$ m /  $-75\mu$ m versus surface of glass. Small pits in the mold surface, which may occasionally appear due to the manufacturing process, are cosmetic in nature and do not affect reliability.  $drb_oqfn38-7x5-4_rz26xx\_pack\_1, 8.1, Sheet1$

Rev B1, Page 7/72

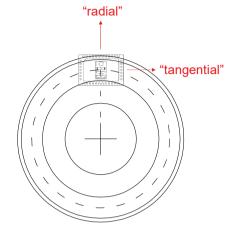

#### LAYOUT DETAILS: iC-RZ26xx

<sup>1</sup> Inspection class for the optical inspection of detector areas. Refer to Customer Information **V20-05** for description.

Rev B1, Page 8/72

#### PACKAGE DIMENSIONS : iC-RZ42xx oQFN38-7x5

All dimensions given in mm. General tolerances of form and position according to JEDEC MO-220. Positional tolerance of sensor pattern:  $\pm 70\mu$ m /  $\pm 0.6^{\circ}$  (with respect to center of backside pad). Maximum molding excess  $\pm 10\mu$ m /  $-75\mu$ m versus surface of glass. Small pits in the mold surface, which may occasionally appear due to the manufacturing process, are cosmetic in nature and do not affect reliability.  $drb_oqfn38-7x5-4_rz42xx\_pack\_1, 81, Sheet1$

Rev B1, Page 9/72

#### LAYOUT DETAILS: iC-RZ42xx

Rev B1, Page 10/72

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol  | Parameter                              | Conditions                                    |      |               | Unit |

|------|---------|----------------------------------------|-----------------------------------------------|------|---------------|------|

| No.  |         |                                        |                                               | Min. | Max.          |      |

| G001 | V(VDD)  | Voltage at VDD1, VDD2, VDDA1,<br>VDDA2 | GND1, GND2 connected                          | -0.3 | 6             | V    |

| G002 | V(VIO)  | Voltage at VIO1, VIO2                  | GND1, GND2 connected                          | -0.3 | 6             | V    |

| G003 | V(VDDM) | Voltage at VDDM1, VDDM2                | GND1, GND2 connected                          | -0.3 | 6             | V    |

| G004 | I(VDDx) | Current in VDD1, VDD2, VDDA1,<br>VDDA2 | GND1, GND2 connected                          | -20  | 50            | mA   |

| G005 | I(VIOx) | Current in VIO1, VIO2                  | GND1, GND2 connected                          | -20  | 50            | mA   |

| G006 | V()a    | Pin Voltage, all signal analog outputs | GND1, GND2 connected                          | -0.3 | VDDA<br>+ 0.3 | V    |

| G007 | V()io   | Pin Voltage, all signal digital output | GND1, GND2 connected                          | -0.3 | VIO + 0.3     | V    |

| G008 | I()     | Pin Current, all signal outputs        | GND1, GND2 connected                          | -10  | 10            | mA   |

| G009 | Vd()    | ESD Susceptibility at all Pins         | HBM, 100 pF discharged through $1.5  k\Omega$ |      | 2             | kV   |

| G010 | Tj      | Junction Temperature                   |                                               | -40  | 150           | °C   |

#### THERMAL DATA

Operating Conditions (x = 1,2): VDDx = VDDAx = 4.5...5.5 V, GNDx = 0V, VDDMx = 2.9V...VDDAx, VIOx = 2.375V...VDDx

| Item | Symbol | Parameter Conditions                     |                                                     |      |      | Unit |     |

|------|--------|------------------------------------------|-----------------------------------------------------|------|------|------|-----|

| No.  |        |                                          |                                                     | Min. | Тур. | Max. |     |

| T01  | Та     | Operating Ambient Temperature Range      | oQFN38 7x5                                          | -40  |      | 125  | °C  |

| T02  | Ts     | Permissible Storage Temperature<br>Range | oQFN38 7x5                                          | -40  |      | 125  | °C  |

| T03  | Rthja  |                                          | oQFN38 7x5<br>soldered to PCB according to JEDEC 51 |      | 35   |      | K/W |

Rev B1, Page 11/72

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No.                                   | Symbol                                                                        | Parameter                                                                                                                                                                                                                                                                      | Conditions                                                                                                                                                                                                                                                                                                                                                                                            | Min.                             | Тур.                             | Max.                  | Unit                                                                                                                                                                                                                                                                             |

|-----------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total                                         | Device (x = 1                                                                 | , 2)                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |                                  |                       |                                                                                                                                                                                                                                                                                  |

| 001                                           | VDDx                                                                          | Permissible Supply Voltage                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                       | 4.5                              |                                  | 5.5                   | V                                                                                                                                                                                                                                                                                |

| 002                                           | VDDAx                                                                         | Permissible Supply Voltage                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                       | 4.5                              |                                  | 5.5                   | V                                                                                                                                                                                                                                                                                |

| 003                                           | VIOx                                                                          | Permissible Supply Voltage                                                                                                                                                                                                                                                     | $VIOx \le VDDx$<br>VIOx must be up before tdr1() ends                                                                                                                                                                                                                                                                                                                                                 | 2.375                            |                                  | 5.5                   | V                                                                                                                                                                                                                                                                                |

| 004                                           | VDDMx                                                                         | Permissible Supply Voltage                                                                                                                                                                                                                                                     | if VDDx > VDDxon:<br>VDDMx $\leq$ VDDx, VDDMx $\leq$ VDDAx                                                                                                                                                                                                                                                                                                                                            | 2.9                              |                                  | 5.5                   | V                                                                                                                                                                                                                                                                                |

| 005                                           | I(VDD1)                                                                       | Supply Current VDD1                                                                                                                                                                                                                                                            | no load                                                                                                                                                                                                                                                                                                                                                                                               |                                  | 2.5                              | 5                     | mA                                                                                                                                                                                                                                                                               |

| 006                                           | I(VDD2)                                                                       | Supply Current VDD2                                                                                                                                                                                                                                                            | no load                                                                                                                                                                                                                                                                                                                                                                                               |                                  | 4.0                              | 8                     | mA                                                                                                                                                                                                                                                                               |

| 007                                           | I(VDDA1)                                                                      | Supply Current VDDA1                                                                                                                                                                                                                                                           | photocurrent amplifiers within op. range, no load                                                                                                                                                                                                                                                                                                                                                     |                                  | 12.0                             | 20                    | mA                                                                                                                                                                                                                                                                               |

| 008                                           | I(VDDA2)                                                                      | Supply Current VDDA2                                                                                                                                                                                                                                                           | photocurrent amplifiers within op. range, no load                                                                                                                                                                                                                                                                                                                                                     |                                  | 6.0                              | 10                    | mA                                                                                                                                                                                                                                                                               |

| 009                                           | I(VIO1)                                                                       | Supply Current VIO1                                                                                                                                                                                                                                                            | V(VIO1) = 5V, no load<br>V(VIO1) = 3.3V, no load                                                                                                                                                                                                                                                                                                                                                      |                                  | 0.5<br>0.3                       |                       | mA<br>mA                                                                                                                                                                                                                                                                         |

| 010                                           | I(VIO2)                                                                       | Supply Current VIO2                                                                                                                                                                                                                                                            | V(VIO2) = 5V, no load<br>V(VIO2) = 3.3V, no load                                                                                                                                                                                                                                                                                                                                                      |                                  | 1.2<br>0.7                       |                       | mA<br>mA                                                                                                                                                                                                                                                                         |

| 011                                           | $\lambda$ ar                                                                  | Spectral Application Range                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                       | 400                              |                                  | 500                   | nm                                                                                                                                                                                                                                                                               |

| 012                                           | $S(\lambda r)$                                                                | Spectral Sensitivity                                                                                                                                                                                                                                                           | $\lambda_{\text{LED}}$ = 460 nm                                                                                                                                                                                                                                                                                                                                                                       |                                  | 0.11                             |                       | A/W                                                                                                                                                                                                                                                                              |

| 013                                           | E()typ                                                                        | Typical Irradiance                                                                                                                                                                                                                                                             | $\lambda_{\text{LED}}$ = 460 nm , Vout() < Vout()mx                                                                                                                                                                                                                                                                                                                                                   |                                  | 12                               |                       | mW/cm <sup>2</sup>                                                                                                                                                                                                                                                               |

| 014                                           | C()                                                                           | Required Backup Capacitor<br>at Pin VDD1, VDD2, VDDA1,<br>VDDA2, VIO1, VIO2                                                                                                                                                                                                    | placed near by pin, recommended low ESR                                                                                                                                                                                                                                                                                                                                                               |                                  | 100                              |                       | nF                                                                                                                                                                                                                                                                               |

| 015                                           | C(VDDMx)                                                                      | Required Backup Capacitor at<br>Pin VDDM1, VDDM2                                                                                                                                                                                                                               | C1 in Figure 43, MODE_MT_CC/SC = 0x0E<br>(Battery-buffered revolution counter activated)<br>placed near by pin, recommended low ESR                                                                                                                                                                                                                                                                   |                                  | 1                                |                       | μF                                                                                                                                                                                                                                                                               |

|                                               |                                                                               | notodiodes and Amplifiers: PSIN                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |                                  |                       |                                                                                                                                                                                                                                                                                  |

| 101                                           | Aph()                                                                         | Radiant Sensitive Area                                                                                                                                                                                                                                                         | DPSIN, DNSIN, DPCOS, DNCOS<br>(sum of segments per signal)<br>RZ2648<br>RZ4248<br>RZ2624<br>RZ4224                                                                                                                                                                                                                                                                                                    |                                  | 0.058<br>0.064<br>0.042<br>0.053 |                       | mm <sup>2</sup><br>mm <sup>2</sup><br>mm <sup>2</sup><br>mm <sup>2</sup>                                                                                                                                                                                                         |

| 102                                           | Z()                                                                           | Equivalent Transimpedance Gain                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |                                  | <u> </u>              |                                                                                                                                                                                                                                                                                  |

|                                               |                                                                               |                                                                                                                                                                                                                                                                                | RZ26xx<br>RZ42xx                                                                                                                                                                                                                                                                                                                                                                                      |                                  | 0.971<br>0.780                   |                       | ΜΩ<br>ΜΩ                                                                                                                                                                                                                                                                         |

| 103                                           | TCz                                                                           | Temperature Coefficient of Z()                                                                                                                                                                                                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |                                  |                       |                                                                                                                                                                                                                                                                                  |

| 103<br>104                                    | TCz<br>fc()hi                                                                 | Temperature Coefficient of Z()<br>Cut-off Frequency (-3 dB)                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                     | 250                              | 0.780                            |                       | MΩ                                                                                                                                                                                                                                                                               |

|                                               |                                                                               |                                                                                                                                                                                                                                                                                | RZ42xx                                                                                                                                                                                                                                                                                                                                                                                                | 250                              | 0.780<br>-0.25                   | 100                   | ΜΩ<br>%/°C                                                                                                                                                                                                                                                                       |

| 104                                           | fc()hi                                                                        | Cut-off Frequency (-3 dB)                                                                                                                                                                                                                                                      | RZ42xx<br>Signals PSIN, NSIN, PCOS, NCOS                                                                                                                                                                                                                                                                                                                                                              | 250<br>2.2<br>3.0                | 0.780<br>-0.25                   | 100                   | MΩ<br>%/°C<br>kHz                                                                                                                                                                                                                                                                |

| 104<br>105                                    | fc()hi<br>ton()                                                               | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at                                                                                                                                                                                               | RZ42xxSignals PSIN, NSIN, PCOS, NCOSVDD1 = $0 V \rightarrow 5 V$ increasing illumination, EAMPA = $0$ VDD1 = $4.5 V$                                                                                                                                                                                                                                                                                  | 2.2                              | 0.780<br>-0.25                   | 100                   | MΩ<br>%/°C<br>kHz<br>μs<br>V                                                                                                                                                                                                                                                     |

| 104<br>105<br>106                             | fc()hi<br>ton()<br>Vout()mx                                                   | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Output Offset Voltage at                                                                                                                                         | RZ42xx<br>Signals PSIN, NSIN, PCOS, NCOS<br>VDD1 = $0 \vee \rightarrow 5 \vee$<br>increasing illumination, EAMPA = $0 \vee DD1 = 4.5 \vee \vee DD1 = 5.5 \vee$<br>amplitude controlled to 250 mV by LED control;                                                                                                                                                                                      | 2.2                              | 0.780<br>-0.25<br>550            | 100                   | MΩ<br>%/°C<br>kHz<br>μs<br>V<br>V                                                                                                                                                                                                                                                |

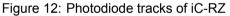

| 104<br>105<br>106<br>107                      | fc()hi<br>ton()<br>Vout()mx<br>Vout()dc                                       | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Output Offset Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Dark Signal Level at VREF and                                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                 | 2.2<br>3.0                       | 0.780 -0.25 550 1.26             |                       | MΩ           %/°C           kHz           μs           V           V           V                                                                                                                                                                                                 |

| 104<br>105<br>106<br>107<br>108               | fc()hi<br>ton()<br>Vout()mx<br>Vout()dc<br>Vout()d                            | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Output Offset Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Dark Signal Level at VREF and<br>PSIN, NSIN, PCOS, NCOS                                                    | RZ42xx<br>Signals PSIN, NSIN, PCOS, NCOS<br>VDD1 = $0 \vee \rightarrow 5 \vee$<br>increasing illumination, EAMPA = $0$<br>VDD1 = $4.5 \vee$<br>VDD1 = $5.5 \vee$<br>amplitude controlled to 250 mV by LED control;<br>signal contrast of 70 % (see 13 for details)<br>no illumination                                                                                                                 | 2.2<br>3.0<br>0.60               | 0.780 -0.25 550 1.26             | 1.15                  | MΩ           %/°C           kHz           µs           V           V           V           V           V                                                                                                                                                                         |

| 104<br>105<br>106<br>107<br>108<br>109        | fc()hiton()Vout()mxVout()dcVout()d $\Delta Z$ ()pn $\Delta Vout()pn$ VNoise() | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Output Offset Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Dark Signal Level at VREF and<br>PSIN, NSIN, PCOS, NCOS<br>Transimpedance Gain Matching                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                 | 2.2<br>3.0<br>0.60<br>-0.2<br>-5 | 0.780 -0.25 550 1.26             | 1.15<br>0.2<br>5      | MΩ           %/°C           kHz           µs           V           V           V           N           N           N           N           N           N           N           N           N           N           N           N           N           N           N           N |

| 104<br>105<br>106<br>107<br>108<br>109<br>110 | fc()hi<br>ton()<br>Vout()mx<br>Vout()dc<br>Vout()d<br>∠Z()pn<br>∠Vout()pn     | Cut-off Frequency (-3 dB)<br>Power-On Settling Time<br>Maximum Output Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Output Offset Voltage at<br>PSIN, NSIN, PCOS, NCOS<br>Dark Signal Level at VREF and<br>PSIN, NSIN, PCOS, NCOS<br>Transimpedance Gain Matching<br>Signal Matching | RZ42xxSignals PSIN, NSIN, PCOS, NCOSVDD1 = $0 V \rightarrow 5 V$ increasing illumination, EAMPA = $0$ VDD1 = $4.5 V$ VDD1 = $5.5 V$ amplitude controlled to 250 mV by LED control;signal contrast of 70% (see 13 for details)no illuminationany output vs. any outputany output vs. any outputany output vs. VREFno illuminationilluminated to 500 mV signal level above darklevel, 500 kHz bandwidth | 2.2<br>3.0<br>0.60<br>-0.2<br>-5 | 0.780 -0.25 550 1.26             | 1.15<br>0.2<br>5<br>6 | MΩ           %/°C           kHz           µs           V           V           V           N           N           MΩ                                                                                                                                                            |

Rev B1, Page 12/72

#### **ELECTRICAL CHARACTERISTICS**

Operating Conditions (x = 1, 2): VDDx = VDDAx = VDDMx = 4.5...5.5 V, GNDx = 0 V, VIOx = 2.375 V... VDDx, T<sub>j</sub> = -40...135 °C, unless otherwise noted.

| ltem<br>No. | Symbol        | Parameter                                       | Conditions                                                                                                           | Min.       | Тур.       | Max.       | Unit            |

|-------------|---------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|------------|------------|-----------------|

| 114         | lsc(VREF)hi   | Short-Circuit Current hi from pin<br>VREF       | load current to ground                                                                                               | -1500      | -1000      | -500       | μA              |

| 115         | lsc()lo       | Short-Circuit Current lo in pins                | load current to IC                                                                                                   | 200        | 650        | 1000       | μA              |

| 116         | Isc(VREF)lo   | Short-Circuit Current lo in pin<br>VREF         | load current to IC                                                                                                   | 2000       | 4500       | 6000       | μA              |

| 117         | TCf           | Temperature Coefficent VREF                     |                                                                                                                      |            | -1.2       |            | mV/°C           |

| 118         | V(VREF)       | Output Voltage                                  | Tj = 27°C                                                                                                            |            | 890        |            | mV              |

| Power       | Down Rese     | et: VDDx (x = 1, 2)                             |                                                                                                                      |            |            |            |                 |

| 401         | VDDxon        | Turn-on Threshold VDDx                          | increasing voltage at VDDx                                                                                           | 3.8        | 4.2        | 4.45       | V               |

| 402         | VDDxoff       | Turn-off Threshold VDDx<br>(undervoltage reset) | decreasing voltage at VDDx                                                                                           | 3.6        | 4.0        | 4.3        | V               |

| 403         | VDDxhys       | Threshold Hysteresis VDDx                       | VDDxhys = VDDxon - VDDxoff                                                                                           | 100        |            |            | mV              |

| Incren      | nental Track  | (1024 CPR): Photodiodes and A                   | mplifiers                                                                                                            |            |            |            |                 |

| 701         | Aph()         | Radiant Sensitive Area                          | sum of segments                                                                                                      |            | 0.033      |            | mm <sup>2</sup> |

| 702         | Z()           | Equivalent Transimpedance Gain                  | Z = Vout() / Iph(), Tj = 27 °C                                                                                       |            | 1.3        |            | MΩ              |

| 703         | TCz           | Temperature Coefficient of Z()                  |                                                                                                                      |            | -0.25      |            | %/°C            |

| 704         | fc()hi        | Cut-off Frequency (-3 dB)                       |                                                                                                                      | 200        | 450        |            | kHz             |

| 705         | Vout()mx      | Maximum Output Voltage                          | increasing illumination, EAMP24 = 0<br>VDDx = 4.5 V<br>VDDx = 5.5 V                                                  | 2.2<br>3.0 |            |            | V<br>V          |

| 706         | Vout()d       | Dark Signal Level                               | no illumination                                                                                                      | 0.6        | 0.9        | 1.15       | V               |

|             | eal-time Inte | •                                               |                                                                                                                      |            |            | _          |                 |

|             | 1             | Resolution Interpolator                         | reference one period of the 1024 track                                                                               |            | 5          |            | bit             |

| 802         |               | Absolute Angular Accuracy                       | ideal input signals with an amplitude of 250 mV, guasi-static                                                        | -5.6       |            | 5.6        | DEG             |

| 803         | AArel         | Relative Angle Accuracy                         | ideal input signals with an amplitude of 250 mV, guasi-static                                                        | -4.2       |            | 4.2        | DEG             |