Rev E2, Page 1/28

#### **FEATURES**

Programmable angle resolution from 1 to 256 steps per period Interpolation factors from x0.25 to x64

Input frequency to 115 kHz with x64, to 230 kHz with x32, to  $460\,\mathrm{kHz}$  with x16

Latency of less than 1 µs

Selectable gain permits single-ended and differential input signals from 10 mV to 1.5 V peak-peak

Index gating input with fine adjustable offset

Programmable index pulse output position and width

Four incremental output modes: quadrature encoder with index, up/down clock, incr./direction, 3 phase commutation

Programmable filter and hysteresis

Direct sensor connection, minimized count of external components

Non-volatile setup due to internal EEPROM

Fully re-programmable via serial 1- and 2-wire interfaces

Power-on reset circuit and on-chip oscillator

ESD protection and TTL-/CMOS-compatible outputs

Operation at 3.0 V to 5.5 V, from -40 °C to +125 °C

#### **APPLICATIONS**

Interpolation IC for position data acquisition from analog sine/cosine sensors

Optical linear and rotary encoders

Magneto resistive sensors and encoders

#### **PACKAGES**

QFN24 (4 mm x 4 mm)

Rev E2, Page 2/28

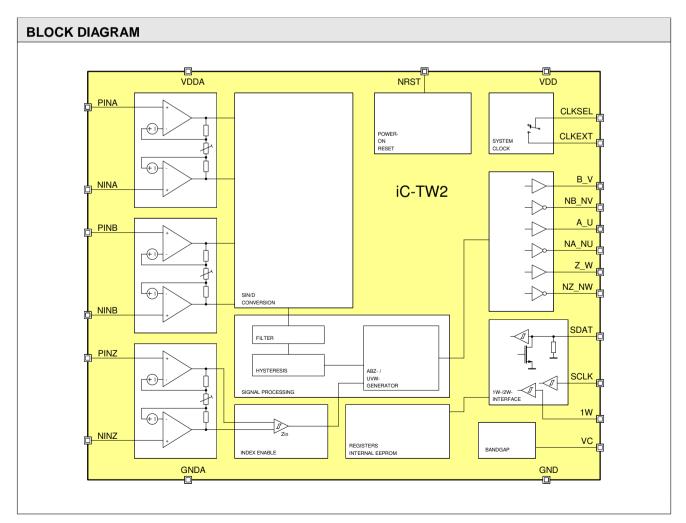

#### DESCRIPTION

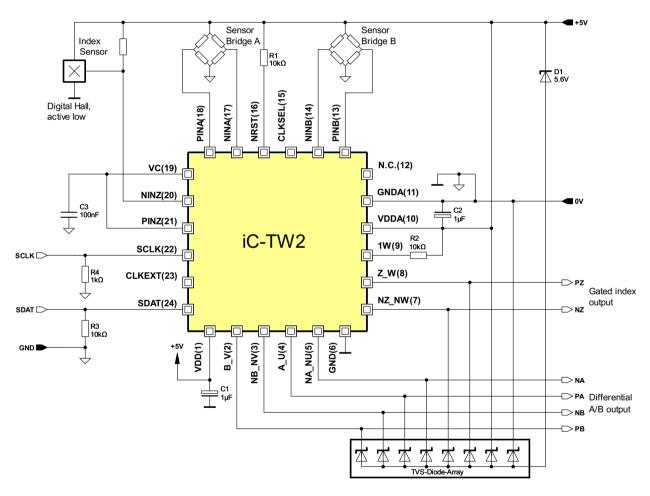

iC-TW2's interpolation engine accepts two fully differential sensor bridges delivering sine and cosine input signals to produce a highly interpolated output signal. No further external components are required. Single-ended sensor signals are supported by tying the negative input terminals to the signal reference, usually VDD/2.

iC-TW2 generates one index pulse for every input period. The position in respect to the start of the period as well as the width of the pulse is fully programmable.

There are four different output modes provided, including 3-phase commutation output for brushless DC motors. To meet requirements for a wide range of applications, iC-TW2 is highly programmable.

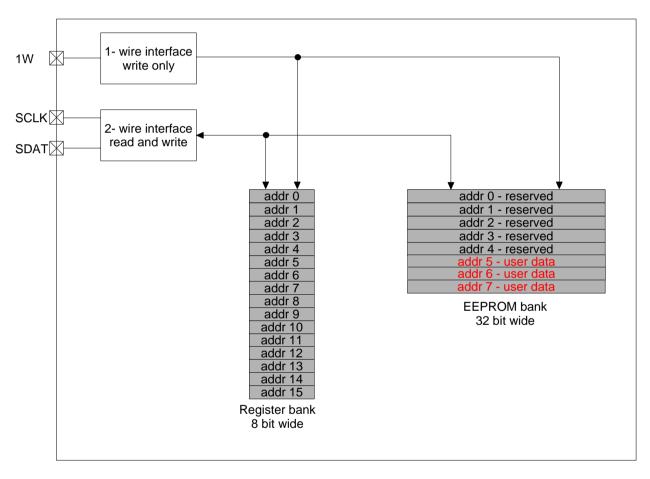

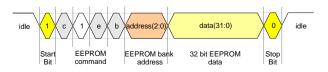

Two serial interfaces have been included to permit configuration of the device, also accessing the internal EEPROM. Both interfaces allow complete configuration of the device including transfer of setup data to internal registers and the on-chip EEPROM for non-volatile storage.

#### **CONTENTS**

| PACKAGING INFORMATION                  | 3  | Oscillator and index window calibration | 16           |

|----------------------------------------|----|-----------------------------------------|--------------|

| PIN CONFIGURATION QFN24 4 mm x 4 mm    | 3  | CONFIGURATION DEPENDENCIES              | 17           |

| A DOOL LITE MANUALINA DATINGO          |    |                                         | 17           |

| ABSOLUTE MAXIMUM RATINGS               | 4  | Selecting configuration parameters      |              |

| THERMAL DATA                           | 4  | Clock tuning                            | 17<br>17     |

| ELECTRICAL CHARACTERISTICS             | 5  | DEVICE IDENTIFICATION                   | 18           |

| REGISTER MAP                           | 8  | START UP                                | 19           |

| DDOOD A MANINO                         | 9  | Power-On-Reset                          | 19           |

| PROGRAMMING                            | 9  | Reset                                   | 19           |

| DESCRIPTION OF INTERPOLATION           | 10 | 1W-/2W-INTERFACE AND EEPROM ACCESS      | 20           |

| Interpolation vs. Resolution           | 10 |                                         | <b>20</b> 20 |

|                                        |    | Memory map                              |              |

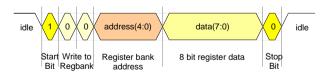

| INPUT STAGE                            | 11 | 2W-Interface                            | 20           |

| Programmable Gain Amplifier            | 11 | 2W-Interface timing                     | 23           |

| Offset Adjustment                      | 11 | Trouble Shooting                        | 23           |

|                                        |    | 1W-Interface                            | 24           |

| OUTPUT MODES                           | 12 | 1W-Interface write sequence             | 24           |

| AB Quadrature And Up/Down and Incr/Dir |    | Writing the register bank to the EEPROM | 24           |

| Modes                                  | 13 | 3 3                                     |              |

| 3 Phase Commutation Mode               | 14 | TEST MODES                              | 25           |

| INDEX GATING                           | 15 | Production test control bits            | 25           |

|                                        |    | TYPICAL APPLICATIONS                    | 26           |

| CALIBRATION                            | 16 |                                         |              |

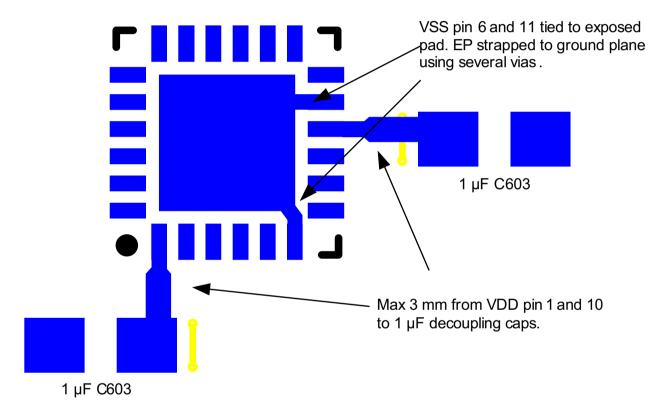

| A/B gain and offset calibration        | 16 | PCB LAYOUT GUIDELINES                   | 27           |

Rev E2, Page 3/28

#### **PACKAGING INFORMATION**

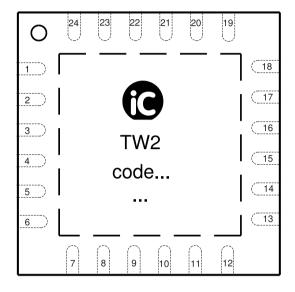

#### PIN CONFIGURATION QFN24 4 mm x 4 mm

#### **PIN FUNCTIONS**

| No. | Name    | Function                              |

|-----|---------|---------------------------------------|

| 1   | VDD     | +3 V to +5.5 V Digital Supply Voltage |

| 2   | B_V     | B Signal / V Signal Output            |

| 3   | NB_NV   | Inverted B / Inverted V Signal Output |

| 4   | A_U     | A Signal/U Signal Output              |

| 5   | NA_NU   | Inverted A / Inverted U Signal Output |

| 6   | GND     | Digital Ground                        |

| 7   | $NZ_NW$ | Inverted Z/Inverted W Signal Output   |

| 8   | $Z_W$   | Z Signal / W Signal Output            |

| 9   | 1W      | 1W-Interface, signal input            |

| 10  | VDDA    | +3 V to +5.5 V Analog Supply Voltage  |

| 11  | GNDA    | Analog Ground                         |

| 12  | n.c.    | Pin not connected                     |

| 13  | PINB    | Signal Input B+                       |

| 14  | NINB    | Signal Input B-                       |

| 15  | CLKSEL  | System Clock Selection Input          |

|     | NRST    | External Reset Input (active low)     |

| 17  | NINA    | Signal Input A-                       |

| _   | PINA    | Signal Input A+                       |

|     | VC      | 1.2 V Reference Voltage Output        |

|     | NINZ    | Signal Input Z- (Index)               |

|     | PINZ    | Signal Input Z+ (Index)               |

|     | SCLK    | 2-Wire Interface, clock input         |

| 23  | CLKEXT  | External Clock Input                  |

|     | SDAT    | 2-Wire Interface, serial data in/out  |

| ΤP  |         | Thermal Pad (bottom side)             |

The *Thermal Pad* of the QFN package (bottom side) is to be connected to a ground plane on the PCB which must have GND potential. GNDA must be wired to GND.

Only pin 1 marking on top or bottom defines the package orientation; label and lot codes can be subject to changes.

Rev E2, Page 4/28

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol       | Parameter                                                                                                               | Conditions                                                                  |      |                | Unit |

|------|--------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|----------------|------|

| No.  | -            |                                                                                                                         |                                                                             | Min. | Max.           |      |

| G001 | VDD,<br>VDDA | Voltage at VDD, VDDA                                                                                                    | referenced to GND                                                           | -0.3 | 6.0            | V    |

| G002 | ∆VDDA        | Voltage Difference VDD vs. VDDA                                                                                         | △VDDA = VDD - VDDA                                                          | 0    | 0.5            | V    |

| G003 | V()          | Voltage at<br>PINA, NINA, PINB, NINB, PINZ, NINZ,<br>B_V, NB_V, A_U, NA_U, Z_W, NZ_W,<br>1W, SDAT, SCLK, CLKSEL, CLKEXT | referenced to GND                                                           | -0.3 | VDD +<br>0.5 V | V    |

| G004 | I()          | Current in PINA, NINA, PINB, NINB, PINZ, NINZ, B_V, NB_V, A_U, NA_U, Z_W, NZ_W, 1W, SDAT, SCLK, CLKSEL, CLKEXT, VC      |                                                                             | -20  | 20             | mA   |

| G005 | Vd           | ESD Susceptibility Of Signal Outputs                                                                                    | HBM, 100 pF discharged through 1.5 kΩ; pins A_U, NA_U, B_V, NB_V, Z_W, NZ_W |      | 1.5            | kV   |

| G006 | Vd           | ESD Susceptibility (remaining pins)                                                                                     | HBM, 100 pF discharged through 1.5 kΩ                                       |      | 1              | kV   |

| G007 | Tj           | Junction Temperature                                                                                                    |                                                                             | -40  | 125            | °C   |

| G008 | Ts           | Storage Temperature                                                                                                     |                                                                             | -40  | 125            | °C   |

#### THERMAL DATA

| Item | Symbol | Parameter                          | Conditions                                       |      |      |      | Unit |

|------|--------|------------------------------------|--------------------------------------------------|------|------|------|------|

| No.  |        |                                    |                                                  | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature      |                                                  | -40  |      | 125  | °C   |

| T02  | Rthja  | Thermal Resistance Chip To Ambient | QFN24 surface mounted to PCB, following JEDEC 51 |      | 32   |      | K/W  |

Rev E2, Page 5/28

#### **ELECTRICAL CHARACTERISTICS**

| No.    | Symbol            | Parameter                                                                               | Conditions                                                                                                                                             | Min.                                         | Тур.  | Max.               | Unit                     |

|--------|-------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|--------------------|--------------------------|

| Total  | Device            |                                                                                         | 1                                                                                                                                                      |                                              |       |                    | ,                        |

| 001    | VDD,<br>VDDA      | Permissible Supply Voltage VDD, VDDA                                                    |                                                                                                                                                        | 3.0                                          |       | 5.5                | V                        |

| 002    | I(VDD,<br>VDDA)   | Total Supply Current                                                                    | VDD = 3.3 V at 0 Hz<br>VDD = 3.3 V at 100 kHz<br>VDD = 5.5 V at 0 Hz<br>VDD = 5.5 V at 100 kHz                                                         |                                              |       | 5<br>20<br>8<br>40 | mA<br>mA<br>mA           |

| 003    | Vc()hi            | Clamp-Voltage hi at all pins                                                            | Vc()hi = V() - VDD; I() = 10 mA                                                                                                                        | 0.5                                          |       | 1.3                | V                        |

| 004    | Vc()lo            | Clamp-Voltage lo at all pins                                                            | I() = -10  mA                                                                                                                                          | -1.3                                         |       | -0.3               | V                        |

| Input  | Amplifier Pl      | NA, NINA, PINB, NINB                                                                    |                                                                                                                                                        |                                              |       |                    |                          |

| 101    | Vin()sig          | Permissible Input Voltage Range                                                         |                                                                                                                                                        | 1.4                                          |       | VDD -<br>1.2       | V                        |

| 102    | Step(GC)          | Nominal Coarse Gain Step Size                                                           |                                                                                                                                                        |                                              | 6.0   |                    | dB                       |

| 103    | AGabs(GC)         | Coarse Gain Absolute Accuracy                                                           |                                                                                                                                                        | -1.0                                         |       | 3.5                | dB                       |

| 104    | Step(GF)          | Nominal Fine Gain Step Size                                                             |                                                                                                                                                        |                                              | 0.7   |                    | dB                       |

| 105    | AGabs(GF)         | Fine Gain Absolute Accuracy                                                             |                                                                                                                                                        | -0.3                                         |       | 0.3                | dB                       |

| 106    | CGM               | Gain Matching G(CHA)/G(CHB)                                                             |                                                                                                                                                        | 0.85                                         |       | 1.15               |                          |

| 107    | Vin()os           | Input Referred Offset Voltage                                                           |                                                                                                                                                        | -15                                          |       | 15                 | mV                       |

| 108    | Vout()ossc        | Output Referred Offset Correction Step Accuracy                                         |                                                                                                                                                        | -10                                          |       | 10                 | mV                       |

| 109    | Step(OFSx)        | Nominal Offset Correction Step<br>Size                                                  |                                                                                                                                                        |                                              | 13    |                    | mV                       |

| 110    | Vout()os          | Output Referred Offset Voltage                                                          |                                                                                                                                                        | -40                                          |       | 40                 | mV                       |

| 111    | FR                | Permissible Input Frequency;<br>Frequency Ratio FR = f <sub>cal</sub> / f <sub>in</sub> | INTER=1 64, FREQ=0<br>INTER=1 64, FREQ=1<br>INTER=1 64, FREQ=2 127<br>INTER=65 128, FREQ=0<br>INTER=65 128, FREQ=1 127<br>INTER=129 255<br>INTER=0     | 64<br>128<br>256<br>128<br>256<br>256<br>256 |       |                    |                          |

| Oscill | ator              |                                                                                         |                                                                                                                                                        |                                              |       |                    |                          |

| 201    | f <sub>cal</sub>  | Permissible User Calibrated<br>Oscillator Frequency                                     | measured at pin A_U in calib mode 2 as 1/32;<br>VDD = 3.6 V, Tj = 25 °C<br>VDD = 5.5 V, Tj = 25 °C                                                     |                                              |       | 25<br>30           | MHz<br>MHz               |

| 202    | f <sub>osc</sub>  | Oscillator Frequency                                                                    | VDD = 3.0 V, Tj = 25 °C, CLOCK = 0<br>VDD = 3.0 V, Tj = 25 °C, CLOCK = 31<br>VDD = 5.5 V, Tj = 25 °C, CLOCK = 0<br>VDD = 5.5 V, Tj = 25 °C, CLOCK = 31 | 35<br>40                                     |       | 25<br>28           | MHz<br>MHz<br>MHz<br>MHz |

| 203    | TC <sub>osc</sub> | Oscillator Frequency<br>Temperature Drift                                               | VDD = 5.0 V +/- 2%                                                                                                                                     |                                              | -0.12 | 0                  | %/K                      |

| 204    | VC <sub>osc</sub> | Oscillator Frequency Power Supply Dependency                                            | Tj = 25 °C                                                                                                                                             |                                              | 10    |                    | %/V                      |

| 205    | df <sub>osc</sub> | Osc. Frequency Variation 3.3 V                                                          | supply voltage 3.3 V +/-10%, Tj = 25 °C                                                                                                                |                                              | +/-3  |                    | %                        |

| 206    | df <sub>osc</sub> | Osc. Frequency Variation 5 V                                                            | supply voltage 5 V +/-10%, Tj = 25 °C                                                                                                                  |                                              | +/-2  |                    | %                        |

| EEPR   | OM                |                                                                                         |                                                                                                                                                        |                                              |       |                    |                          |

| 301    | Tret              | Data Retention Time                                                                     | Tj = 125 °C<br>Tj = 85 °C                                                                                                                              | 10<br>100                                    |       |                    | years<br>years           |

| 302    | Ncycles           | Number of Erase/Write Cycles                                                            | Tj = 25 °C                                                                                                                                             | 1000                                         |       |                    |                          |

| 303    | Nread             | Number of Read Cycles                                                                   |                                                                                                                                                        | 10 <sup>6</sup>                              |       |                    |                          |

|        | *                 |                                                                                         |                                                                                                                                                        |                                              |       |                    |                          |

| Refer  | ence Voltage      | Output VC                                                                               |                                                                                                                                                        |                                              |       |                    |                          |

Rev E2, Page 6/28

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VDDA = 3.0...5.5 V. Ti = -40...125 °C. unless otherwise stated

| Item<br>No. | Symbol      | Parameter                                | Conditions                                                                                       | Min.       | Тур.                 | Max.        | Unit     |

|-------------|-------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------------|----------------------|-------------|----------|

| Digita      | I Inputs NR | ST                                       | ı                                                                                                | Ш          | , ,,                 |             |          |

| 501         | Vt()hi      | Input Threshold Voltage hi               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                     | 1.5<br>3.3 |                      |             | V        |

| 502         | Vt()lo      | Input Threshold Voltage lo               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                     |            |                      | 0.8<br>1.0  | V        |

| 503         | lpu()       | Input Pull-up Current                    | V() = 0VDD - 1 V                                                                                 |            |                      | -3          | μA       |

| 504         | Vpu()       | Input Pull-up Voltage                    | Vpu() = VDD - V(), I() = -3 μA                                                                   |            |                      | 500         | mV       |

| Digita      | Inputs CL   | KSEL, CLKEXT                             |                                                                                                  |            |                      |             |          |

| 601         | Vt()hi      | Input Threshold Voltage hi               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                     | 1.5<br>3.3 |                      |             | V<br>V   |

| 602         | Vt()lo      | Input Threshold Voltage lo               | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                                     |            |                      | 0.8<br>1.0  | V        |

| 603         | lpd()       | Input Pull-down Current                  | V() = 1 VVDD                                                                                     | 4          |                      |             | μΑ       |

| 604         | Vpd()       | Input Pull-down Voltage                  | I() = 3 µA                                                                                       |            |                      | 500         | mV       |

| Digita      | Outputs A   | _U, NA_NU, B_V, NB_NV, Z_W, N            | z_nw                                                                                             | U.         |                      | ,           |          |

| 701         | Vs()hi      | Output Saturation Voltage hi             | Vs()hi = V(VDD) - V(), I() = -6 mA;<br>VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %              |            |                      | 0.5<br>0.4  | V        |

| 702         | Isc()hi     | Short-circuit Current hi                 | V() = GND                                                                                        | -100       |                      | -15         | mA       |

| 703         | Vs()lo      | Output Saturation Voltage lo             | I() = 6 mA;<br>VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %                                      |            |                      | 0.3<br>0.25 | V        |

| 704         | Isc()lo     | Short-circuit Current lo                 | V() = VDD                                                                                        | 20         |                      | 140         | mA       |

| 705         | tr()        | Output Rise time                         | VDD = 3.0 V, CL() = 10 pF                                                                        |            |                      | 4           | ns       |

| 706         | tf()        | Output Fall Time                         | VDD = 3.0 V, CL() = 10 pF                                                                        |            |                      | 4           | ns       |

| 707         | I()max      | Permissible Load Current                 | source and sink                                                                                  | -10        |                      | 10          | mA       |

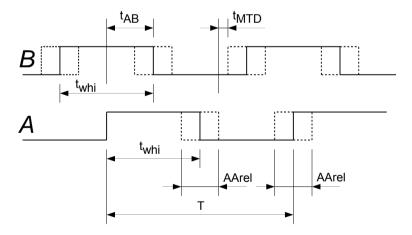

| 708         | twhi        | Duty Cycle at Output A, B                | referred to period T, see Fig. 1                                                                 |            | 50                   |             | %        |

| 709         | tAB         | Output Phase A vs. B                     | referred to period T, see Fig. 1                                                                 |            | 25                   |             | %        |

| 710         | tMTD        | Minimum Transition Distance              | see Fig. 1                                                                                       |            | 1/ f <sub>core</sub> |             |          |

| Signa       | l Processin | g                                        | 1                                                                                                | "          |                      |             |          |

| 801         | AAabs       | Absolute Angular Accuracy                | referred to 360° input signal<br>GC(2:0) = 1<br>INTER(7:0) = 0<br>FREQ(6:0) = 127<br>f() < 50 Hz | -6         |                      | 6           | DEG      |

| 802         | AArel       | Relative Angular Accuracy                | referred to period of A, B<br>GC(2:0) = 1<br>INTER(7:0) = 0<br>FREQ(6:0) = 127<br>f() < 50 Hz    | -20        |                      | 20          | %        |

| 803         | ABrel       | Relative Angular Accuracy<br>A vs. B     |                                                                                                  |            | 1/2<br>AArel         |             | %        |

| Index       |             | r PINZ, NINZ                             |                                                                                                  |            |                      |             |          |

| 901         | Vin()sig    | Permissible Input Voltage Range          |                                                                                                  | 0.0        |                      | VDD         | V        |

| 902         | Vin()os     | Input Referred Offset Voltage            |                                                                                                  | -15        |                      | +15         | mV       |

| 903         | Vin()step   | Comparator Offset Step Size              | OFSZ = 07<br>OFSZ = 815                                                                          |            | 1.5<br>-1.5          |             | mV<br>mV |

| Power       | r-Down-Res  | et                                       |                                                                                                  |            |                      |             |          |

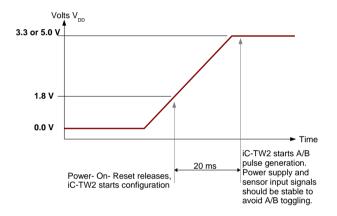

| A01         | VDDon       | Turn-on Threshold VDD (power on release) |                                                                                                  |            | 1.8                  |             | V        |

| A02         | tbusy()cfg  | Duration of Startup Configuration        |                                                                                                  |            | 20                   |             | ms       |

Rev E2, Page 7/28

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VDDA = 3.0...5.5 V, Tj = -40...125 °C, unless otherwise stated

| Item   | Symbol      | Parameter                           | Conditions                                            |            |      |            | Unit   |

|--------|-------------|-------------------------------------|-------------------------------------------------------|------------|------|------------|--------|

| No.    |             |                                     |                                                       | Min.       | Тур. | Max.       |        |

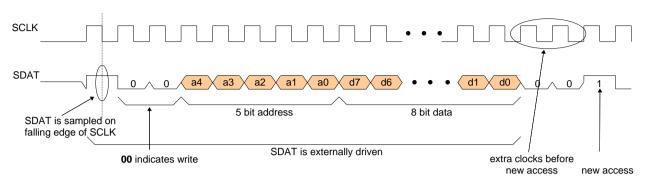

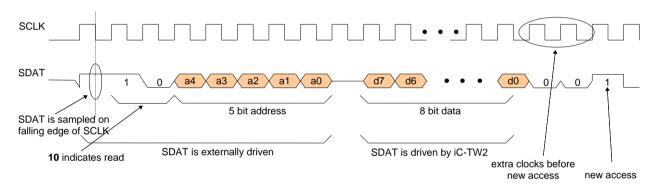

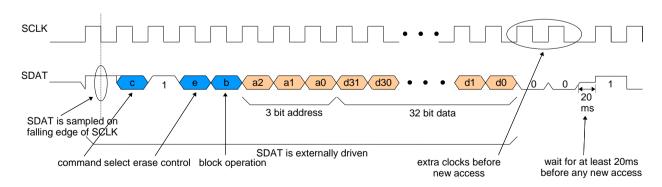

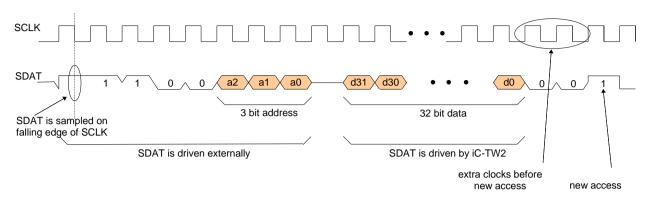

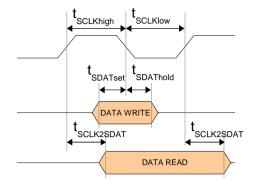

| 2-Wire | Interface S | DAT, SCLK                           |                                                       |            |      |            |        |

| B01    | Vt()hi      | Input Threshold Voltage hi          | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %          | 1.5<br>3.3 |      |            | V<br>V |

| B02    | Vt()lo      | Input Threshold Voltage lo          | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %          |            |      | 0.8<br>1.0 | V<br>V |

| B03    | lpd()       | Input Pull-down Current             | V() = 1 VVDD                                          | 4          |      |            | μA     |

| B04    | Vpd()       | Input Pull-down Voltage             | $I() = 3 \mu A$                                       |            |      | 500        | mV     |

| B05    | Vs()lo      | Saturation Voltage lo at SDAT       | I() = 2 mA                                            |            |      | 450        | mV     |

| B06    | Vs()hi      | Saturation Voltage hi at SDAT       | Vs()hi = VDD - V(); I() = -2 mA                       |            |      | 700        | mV     |

| B07    | Isc()lo     | Short-circuit Current lo at SDAT    |                                                       | 3          |      |            | mA     |

| B08    | Isc()hi     | Short-circuit Current hi at SDAT    |                                                       |            |      | -2.5       | mA     |

| B09    | fclk(SCLK)  | Permissible Clock Frequency<br>SCLK | scales with oscillator frequency timing, see Table 32 |            |      | 1.25       | MHz    |

| B10    | tbusy()e2p  | Max. Duration of EEPROM access      | scales with oscillator frequency timing, see Table 32 |            |      | 20         | ms     |

| 1-Wire | Interface 1 | w                                   |                                                       | "          |      |            |        |

| C01    | Vt()hi      | Input Threshold Voltage hi          | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %          | 1.5<br>3.3 |      |            | V      |

| C02    | Vt()lo      | Input Threshold Voltage lo          | VDD = 3.3 V +/- 10 %<br>VDD = 5.0 V +/- 10 %          |            |      | 0.8<br>1.0 | V<br>V |

| C03    | lpu()       | Input Pull-up Current               | V() = 0VDD - 1 V                                      |            |      | -3         | μA     |

| C04    | Vpu()       | Input Pull-up Voltage               | Vpu() = VDD - V(), I() = -3 μA                        |            |      | 500        | mV     |

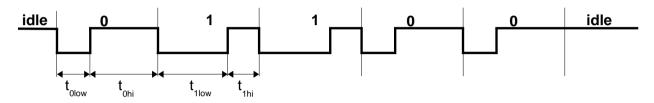

Figure 1: Relative phase distance

Rev E2, Page 8/28

#### **REGISTER MAP**

| Registe   | er Map                           |                     |                                      |                            |                             |                          |                 |                          |

|-----------|----------------------------------|---------------------|--------------------------------------|----------------------------|-----------------------------|--------------------------|-----------------|--------------------------|

| Addr      | Bit 7                            | Bit 6               | Bit 5                                | Bit 4                      | Bit 3                       | Bit 2                    | Bit 1           | Bit 0                    |

| Device I  | ndentification                   | 1                   | I                                    | 1                          | 1                           | l                        | 1               | l                        |

| 0x00      |                                  | IDA                 | (3:0)                                |                            |                             | IDB                      | (3:0)           |                          |

| Operatir  | ng Modes                         | Modes               |                                      |                            |                             |                          |                 |                          |

| 0x01      |                                  | RESET (P. 19)       | CALIB1 (P. 16)                       | STARTU                     | P(1:0)(P. 19)               | DIR (P. 12)              | MODE            | (1:0) <sub>(P. 12)</sub> |

| Interpola | olation Rate                     |                     |                                      |                            |                             |                          |                 |                          |

| 0x02      |                                  |                     |                                      | INTER                      | (7:0) <sub>(P. 12)</sub>    |                          |                 |                          |

| Index Po  | sition                           |                     |                                      |                            |                             |                          |                 |                          |

| 0x03      |                                  |                     |                                      | IPOS(                      | 7:0) <sub>(P. 13)</sub>     |                          |                 |                          |

| Index W   | idth                             |                     |                                      |                            |                             |                          |                 |                          |

| 0x04      |                                  |                     |                                      | IWIDTH                     | I(7:0) <sub>(P. 13)</sub>   |                          |                 |                          |

| Convers   | ion Settings                     |                     |                                      |                            |                             |                          |                 |                          |

| 0x05      | GRANU-<br>LAR <sub>(P. 25)</sub> |                     |                                      |                            | FREQ(6:0) <sub>(P. 17</sub> | 7)                       |                 |                          |

| 0x06      |                                  |                     |                                      |                            | FILTER                      | (1:0) <sub>(P. 17)</sub> | HYST(           | 1:0) <sub>(P. 17)</sub>  |

| Gain and  | d Offset                         |                     |                                      |                            |                             |                          |                 |                          |

| 0x07      |                                  | GFB(1               | :0) (P. 11)                          | GFA(1                      | :0) (P. 11)                 |                          | GC(2:0) (P. 11) |                          |

| 0x08      |                                  |                     |                                      |                            | OFSA(                       | ,                        |                 |                          |

| 0x09      |                                  |                     |                                      |                            | OFSB(                       | 5:0) <sub>(P. 11)</sub>  |                 |                          |

| Bias and  | d Oscillator Ti                  |                     |                                      |                            |                             |                          |                 |                          |

| 0x0A      |                                  | VC(1                | :0) <sub>(P. 25)</sub>               |                            | C                           | LOCK(4:0) <sub>(P.</sub> | 16)             |                          |

| Index Co  | omputation a                     | nd Miscellane       |                                      |                            |                             |                          |                 |                          |

| 0x0B      |                                  | OFSZ(               | 3:0) <sub>(P. 16)</sub>              |                            | EN_MON (P. 25)              | CLKDLY (P. 25)           | CLKDIV (P. 17)  | CLKMODE<br>(P. 25)       |

| Reserve   | d and Calibra                    | ation               |                                      |                            |                             |                          |                 |                          |

| 0x0C      |                                  |                     |                                      | Reserved <sub>(P. 25</sub> | )                           |                          |                 | CALIB2                   |

| 0x0D      |                                  |                     |                                      | Reser                      | ved <sub>(P. 25)</sub>      |                          |                 |                          |

| EEPRO     | /I Control                       |                     |                                      |                            |                             |                          |                 |                          |

| 0x0E      | EE_READ<br>(P. 25)               | EE_WRITE<br>(P. 24) | EE_WRITE Reserved <sub>(P. 25)</sub> |                            |                             |                          |                 |                          |

| Test Reg  | gister                           |                     |                                      |                            |                             |                          |                 |                          |

| 0x0F      |                                  |                     |                                      | MONITO                     | R(7:0) <sub>(P. 25)</sub>   |                          |                 |                          |

Table 4: Register Map

Rev E2, Page 9/28

#### **PROGRAMMING**

| IIIput Stage                               | Page 11                                                                                                                                             | Device Iden                    | tificationPage 18                                                                                                                                        |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| GC:                                        | Coarse gain control (P. 11)                                                                                                                         | IDA:                           | Major Device Revision (P. 18)                                                                                                                            |

| GFA/B:                                     | Fine gain control on channel A/B (P. 11)                                                                                                            | IDB:                           | Minor Device Revision (P. 18)                                                                                                                            |

| OFSA/B:                                    | Offset control on channel A/B (P. 11)                                                                                                               |                                | ,                                                                                                                                                        |

| MODE:<br>DIR:                              | Output mode selection (P. 12) Count direction (P. 12)                                                                                               | Start Up<br>STARTUP:<br>RESET: | Startup sequence selection (P. 19) Restart interpolation engine (P. 19)                                                                                  |

| INTER:<br>IPOS:                            | Interpolation rate selection (P. 12) Index pulse position (P. 13)                                                                                   | 1W-/2-W-Int                    | terface And EEPROM Access . Page 20                                                                                                                      |

| IWIDTH:                                    | Index pulse width selection (P. 13)                                                                                                                 | EE_WRITE:                      | EEPROM store command (P. 24)                                                                                                                             |

|                                            | , ,                                                                                                                                                 | T1 M                           | D 05                                                                                                                                                     |

| Index Gating                               | g Page 15                                                                                                                                           |                                | Page 25                                                                                                                                                  |

|                                            |                                                                                                                                                     |                                |                                                                                                                                                          |

| Calibration<br>CALIB1:<br>CALIB2:<br>OFSZ: |                                                                                                                                                     | GRANULAR<br>VC:                | A/B output edge granularity control (P. 25) Reference voltage fine tuning (P. 25)                                                                        |

| CALIB1:<br>CALIB2:                         | Calibration mode 1 select (P. 16) Calibration mode 2 select (P. 16)                                                                                 |                                | A/B output edge granularity control<br>(P. 25)<br>Reference voltage fine tuning (P. 25)<br>Clock source selection (P. 25)                                |

| CALIB1:<br>CALIB2:<br>OFSZ:<br>CLOCK:      | Calibration mode 1 select (P. 16) Calibration mode 2 select (P. 16) Index comparator offset control (P. 16) Oscillator tune (P. 16) On Dependencies | VC:                            | A/B output edge granularity control (P. 25) Reference voltage fine tuning (P. 25)                                                                        |

| CALIB1:<br>CALIB2:<br>OFSZ:<br>CLOCK:      | Calibration mode 1 select (P. 16) Calibration mode 2 select (P. 16) Index comparator offset control (P. 16) Oscillator tune (P. 16)                 | VC:<br>CLKMODE:                | A/B output edge granularity control (P. 25) Reference voltage fine tuning (P. 25) Clock source selection (P. 25) Clock distribution delay line selection |

Rev E2, Page 10/28

#### **DESCRIPTION OF INTERPOLATION**

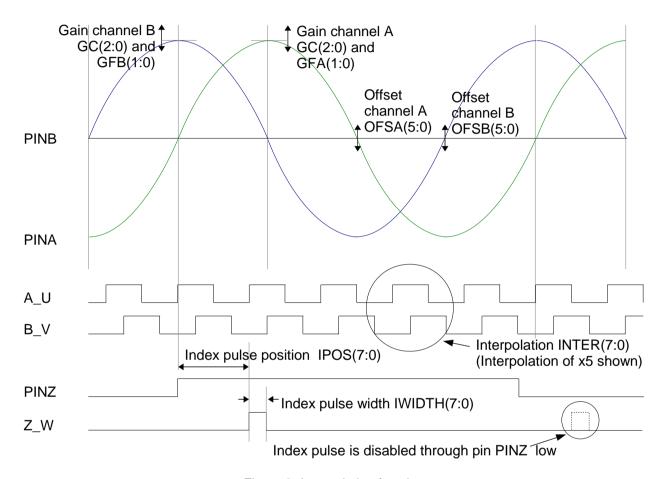

iC-TW2 is a monolithic A/D converter which converts sine/cosine sensor signals with a selectable resolution

and hysteresis into angle position data. The interpolation function is shown in Figure 2.

Figure 2: Interpolation function

#### Interpolation vs. Resolution

There is a difference between interpolation factor and resolution. Resolution (interpolation rate) is determined by the sum of edges at the incremental outputs (AB quadrature output) within one input signal period.

Dividing the resolution by the existing edges of the sine and cosine signals (=4) equals to the interpola-

tion factor. The interpolation factor equals to the the resolution divided by 4.

#### Example:

An interpolation factor of x8 brings a resolution of 32 (edges). To operate with an interpolation factor of 8 configure INTER(7:0) to 32.

Rev E2, Page 11/28

#### **INPUT STAGE**

#### **Programmable Gain Amplifier**

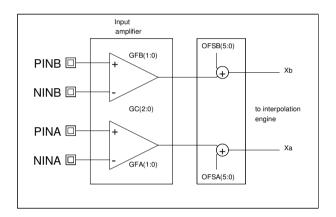

A programmable gain amplifier (PGA) with output referred offset adjustment is used as input stage, shown in Figure 3. The coarse gain is common for both channel A and B and is programmed through register GC(2:0).

Fine tuning gain is applied individually to channel A and B by programming registers GFA(1:0) and GFB(1:0) respectively.

Figure 3: Input stage

| GC(2:0) | Addr. 0x07; bit 2:0 R/W                                                         |

|---------|---------------------------------------------------------------------------------|

| Code    | Input Signal Range V <sub>IN peak-peak</sub> [V <sub>IN peak-peak diff.</sub> ] |

| 000     | 400 mV - 750 mV [800 mV - 1.5 V]<br>400 mV max. @VDD = 3.0 V                    |

| 001     | 200 mV - 400 mV                                                                 |

| 010     | 100 mV - 200 mV                                                                 |

| 011     | 50 mV - 100 mV                                                                  |

| 100     | 25 mV - 50 mV                                                                   |

| 101     | 12.5 mV - 25 mV                                                                 |

| 110     | 5 mV - 12.5 mV                                                                  |

| 111     | not defined (defaults to eeprom setting)                                        |

Table 5: Coarse gain control of channel A/B

| GFA(1:0) | Addr. 0x07; bit 4:3                    | R/W |

|----------|----------------------------------------|-----|

| GFB(1:0) | Addr. 0x07; bit 6:5                    | R/W |

| Code     | Fine Gain (defaults to eeprom setting) |     |

| 00       | 0 dB                                   |     |

| 01       | 0.7 dB                                 |     |

| 10       | 1.4 dB                                 |     |

| 11       | 2.1 dB                                 |     |

Table 6: Fine gain control of channel A/B

#### **Offset Adjustment**

Offset adjustment is provided at the output of the input amplifier. It is individually programmed through register OFSA(5:0) and OFSB(5:0). Adjustment is made in steps of 13 mV and the corresponding register values

are sign magnitude encoded. Input referred offset becomes gain dependent and is defined as follows:

$$V_{\text{OFS (A input referred)}} = \frac{13 \, mV * OFSA(5:0)}{GC(2:0)}$$

| OFSA(5:0) | Addr. 0x08; bit 5:0                            | R/W |

|-----------|------------------------------------------------|-----|

| OFSB(5:0) | Addr. 0x09; bit 5:0                            | R/W |

| Code      | Offset Correction (defaults to eeprom setting) |     |

| 111111    | maximum negative adjust: -403 mV               |     |

| 111110    | -390 mV                                        |     |

| 100001    | -13 mV                                         |     |

| 100000    | no correction                                  |     |

| 000000    | no correction                                  |     |

| 000001    | 13 mV                                          |     |

| 011110    | 390 mV                                         |     |

| 011111    | maximum positive adjust: 403 mV                |     |

Table 7: Offset control of channel A/B

Consider Table 8 regarding the relationship between coarse gain, permissible peak-to-peak input amplitude and the resulting offset correction range.

| Coarse  | Input Signal Range        | Input-referred       | Input-ref.  |

|---------|---------------------------|----------------------|-------------|

| Gain    |                           | offset corr. range   | offset step |

| GC(2:0) | V <sub>IN peak-peak</sub> | V <sub>OFS max</sub> | $dV_{OFS}$  |

| 0       | 400 mV - 750 mV           | ±806 mV              | 26 mV       |

|         | 400 mV max. @3 V          |                      |             |

| 1       | 200 mV - 400 mV           | ± 403 mV             | 13 mV       |

| 2       | 100 mV - 200 mV           | ± 202 mV             | 6.5 mV      |

| 3       | 50 mV - 100 mV            | ± 101 mV             | 3.25 mV     |

| 4       | 25 mV - 50 mV             | ± 50 mV              | 1.63 mV     |

| 5       | 12.5 mV - 25 mV           | ± 25 mV              | 0.81 mV     |

| 6       | 5 mV - 12.5 mV            | ± 12.6 mV            | 0.41 mV     |

Table 8: Input signal and offset correction ranges.

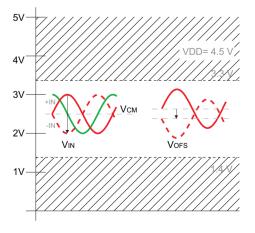

Figure 4: Permissible input voltage range at VDD = 5 V + /-10 %.

Rev E2, Page 12/28

#### **OUTPUT MODES**

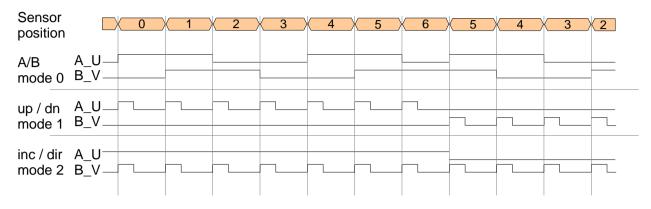

The iC-TW2 provides four different output modes, which are configured by programming bits MODE(1:0) of register 0x01. Modes 0, 1 and 2 are incremental modes whereas mode 3 is a 3-phase commutation output for brushless DC motors. Consider Figure 5 for a comparison of the 3 incremental output modes.

| MODE(1:0) | Addr. 0x01; bit 1:0                  | R/W |

|-----------|--------------------------------------|-----|

| Code      | Function, defaults to eeprom setting |     |

| 00        | AB quadrature (mode 0)               |     |

| 01        | up / dn (mode 1)                     |     |

| 10        | inc / dir (mode 2)                   |     |

| 11        | 3 phase commutation (mode 3)         |     |

Table 9: Output mode selection

In increment / direction mode the count direction can be inverted via control bit DIR of register 0x01.

| DIR  | Addr. 0x01; bit 2                    | R/W |

|------|--------------------------------------|-----|

| Code | Function, defaults to eeprom setting |     |

| 0    | Normal count direction               |     |

| 1    | Inverted count direction             |     |

Table 10: Count direction selection

| INTER<br>(7:0) | Adr 0x02, Bit 7:                  | 0 R/W                                                                                                          |                                                   |

|----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Code           | STEP<br>Angle Steps<br>Per Period | IPF<br>Interpolation<br>Factor                                                                                 | fin()max<br>Max. Permissible<br>Input Frequency * |

| 0x00           | 256                               | 64                                                                                                             | 115 kHz**                                         |

| 0x01           | 1                                 | 0.25                                                                                                           | 460 kHz                                           |

| 0x02           | 2                                 | 0.5                                                                                                            | 460 kHz                                           |

| 0x03           | 3                                 | 0.75                                                                                                           | 460 kHz                                           |

| 0x04           | 4                                 | 1                                                                                                              | 460 kHz                                           |

| 0x05           | 5                                 | 1.25                                                                                                           | 460 kHz                                           |

|                |                                   |                                                                                                                | 460 kHz                                           |

| 0x3C           | 60                                | 15                                                                                                             | 460 kHz                                           |

| 0x3D           | 61                                | 15.25                                                                                                          | 460 kHz                                           |

| 0x3E           | 62                                | 15.5                                                                                                           | 460 kHz                                           |

| 0x3F           | 63                                | 15.75                                                                                                          | 460 kHz                                           |

| 0x40           | 64                                | 16                                                                                                             | 460 kHz                                           |

| 0x41           | 65                                | 16.25                                                                                                          | 230 kHz                                           |

| 0x42           | 66                                | 16.5                                                                                                           | 230 kHz                                           |

| 0x43           | 67                                | 16.75                                                                                                          | 230 kHz                                           |

| 0x44           | 68                                | 17                                                                                                             | 230 kHz                                           |

| 0x45           | 69                                | 17.25                                                                                                          | 230 kHz                                           |

|                |                                   |                                                                                                                | 230 kHz                                           |

| 0x7C           | 124                               | 31                                                                                                             | 230 kHz                                           |

| 0x7D           | 125                               | 31.25                                                                                                          | 230 kHz                                           |

| 0x7E           | 126                               | 31.5                                                                                                           | 230 kHz                                           |

| 0x7F           | 127                               | 31.75                                                                                                          | 230 kHz                                           |

| 0x80           | 128                               | 32                                                                                                             | 230 kHz                                           |

| 0x81           | 129                               | 32.25                                                                                                          | 115 kHz                                           |

| 0x82           | 130                               | 32.5                                                                                                           | 115 kHz                                           |

| 0x83           | 131                               | 32.75                                                                                                          | 115 kHz                                           |

| 0x84           | 132                               | 33                                                                                                             | 115 kHz                                           |

| 0x85           | 133                               | 33.25                                                                                                          | 115 kHz                                           |

|                |                                   |                                                                                                                | 115 kHz                                           |

| 0xFA           | 250                               | 62.5                                                                                                           | 115 kHz                                           |

| 0xFB           | 251                               | 62.75                                                                                                          | 115 kHz                                           |

| 0xFC           | 252                               | 63                                                                                                             | 115 kHz                                           |

| 0xFD           | 253                               | 63.25                                                                                                          | 115 kHz                                           |

| 0xFE           | 254                               | 63.5                                                                                                           | 115 kHz                                           |

| 0xFF           | 255                               | 63.75                                                                                                          | 115 kHz                                           |

| Notes          |                                   | or $f_{\rm osc}$ = 29.4 MHz, FREQ = 0, CLKDIV = 0.<br>15 kHz is fin()max for commutation operation<br>DE = 3). |                                                   |

Table 11: Converter resolution

Rev E2, Page 13/28

#### AB Quadrature And Up/Down and Incr/Dir Modes

Figure 5: Incremental output modes (mode 0, 1, 2)

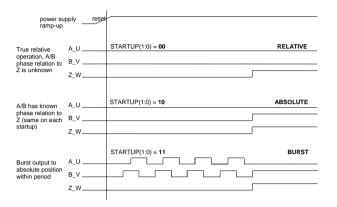

| IPOS(7:0) | Addr. 0x03; bit 7:0 R/W                                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| Code      | Function, defaults to eeprom setting                                                                                |

| 0         | No offset                                                                                                           |

| 1         | 1 increment offset                                                                                                  |

| 2         | 2 increments offset                                                                                                 |

|           |                                                                                                                     |

|           | Index pulse will be shifted by IWIDTH(7:0) increments. Programmed value is within the range of 0 to INTER(7:0) - 1. |

|           |                                                                                                                     |

| 255       | 255 increments offset                                                                                               |

| Note:     | A fixed phase relation to A/B is guaranteed only with STARTUP(1:0) = 0b10 ('ABSOLUTE") or                           |

|           | STARTUP(1:0) = 0b11 ('BURST").                                                                                      |

Table 12: Index pulse position

| IWIDTH(7:0        | ) Addr. 0x04; bit 7:0                                                                                              | R/W |

|-------------------|--------------------------------------------------------------------------------------------------------------------|-----|

| Code              | Function, defaults to eeprom setting                                                                               |     |

| 0                 | disable pulse generation                                                                                           |     |

| 1                 | 1 increment width                                                                                                  |     |

| 2                 | 2 increments width                                                                                                 |     |

|                   |                                                                                                                    |     |

| Any other value n | Index pulse will extend over IWIDTH(7:0) increments.  Programmed value is within the range of 0 to INTER(7:0) - 1. |     |

| 255               | 255 increments width                                                                                               |     |

Table 13: Index pulse width selection

Rev E2, Page 14/28

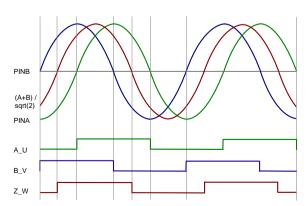

#### 3 Phase Commutation Mode

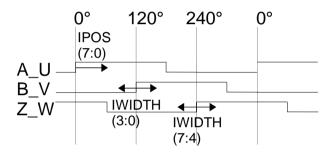

The 3 phase commutation output (mode 3) is shown in Figure 6. It is important that register INTER(7:0) is programmed with the value 0x00 in order for the commutation mode to work. The mode = 3 requires an internal interpolation INTER(7:0) of 256. Register IPOS(7:0) is used to accurately position the commutation. IWIDTH(7:4) and IWIDTH(3:0) is subsequently used to fine tune V and W in respect to U. All used offsets within the commutation mode (mode 3) as are IPOS(7:0), IWIDTH(3:0) and IWIDTH(7:4) operate in this step width of  $1.4^{\circ}$ . There is no other pole count commutation possible to configure as the described 3 phase commutation.

Figure 6: 3-Phase commutation output (mode 3)

| IPOS(7:0) | Addr. 0x03; bit 7:0                                          | R/W |

|-----------|--------------------------------------------------------------|-----|

| Code      | Function, defaults to eeprom setting                         |     |

| 0         | 0°                                                           |     |

| 1         | 1.40°                                                        |     |

| 2         | 2.81°                                                        |     |

|           |                                                              |     |

|           | Programmed value is within the range of 0 to INTER(7:0) - 1. |     |

|           |                                                              |     |

| 255       | 358,59°                                                      |     |

Table 14: UVW commutation signal position offset

| IWIDTH(3:0 | ) Addr. 0x04; bit 3:0                       | R/W |

|------------|---------------------------------------------|-----|

| Code       | V output offset, defaults to eeprom setting |     |

| 0111       | 9.84°                                       |     |

|            |                                             |     |

| 0010       | 2.81°                                       |     |

| 0001       | 1.40°                                       |     |

| 0000       | 0°                                          |     |

| 1111       | -1.40°                                      |     |

| 1110       | -2.81°                                      |     |

|            |                                             |     |

| 1111       | 11.25°                                      |     |

Table 15: V commutation signal position offset

| IWIDTH(7:4) | ) Addr. 0x04; bit 7:4                       | R/W |

|-------------|---------------------------------------------|-----|

| Code        | W output offset, defaults to eeprom setting |     |

| 0111        | 9.84°                                       |     |

|             |                                             |     |

| 0010        | 2.81°                                       |     |

| 0001        | 1.40°                                       |     |

| 0000        | 0°                                          |     |

| 1111        | -1.40°                                      |     |

| 1110        | -2.81°                                      |     |

|             |                                             |     |

| 1111        | 11.25°                                      |     |

Table 16: W commutation signal position offset

Rev E2, Page 15/28

#### **INDEX GATING**

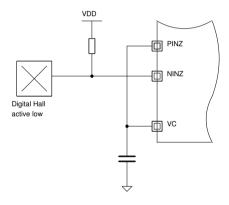

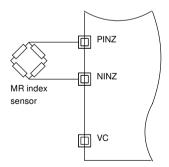

The iC-TW2 can interface to a wide range of index gating sources. Most commonly used are the digital Hall sensor and the MR sensor bridge.

The digital Hall sensor provides a large swing input signal to the iC-TW2. Depending on the polarity of the Hall it is either connected to pin NINZ or PINZ. Most Hall sensors use an open drain stage pulling the output low in the presence of a magnetic field. The unused terminal PINZ or NINZ should be biased to an adequate mid voltage level to guarantee good noise margin. The iC-TW2 provides a constant 1.21 V at pin VC that can be used for this purpose (refer to Figure 7).

Figure 7: Digital Hall sensor index configuration

Figure 8: MR sensor index configuration

An MR sensor differential bridge can also be used to gate the index. Typically, the MR sensor provides a small signal amplitude. In addition, residual side lobes are present that can trigger double indexing. The iC-

TW2 provides offset control capability to fine tune the threshold voltage of the index comparator. This greatly simplifies end product calibration as variation in sensor offset can be compensated for.

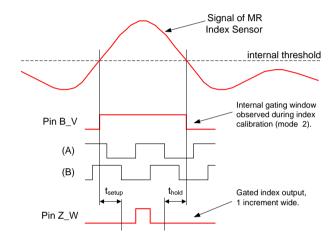

Figure 9 shows a correctly set threshold when using an MR gating sensor. The side lobes are below the threshold line and no parasitic triggering occurs.

Figure 9: Index gating and calibration

Index gating should be calibrated at sine/cosine input frequencies below 5 kHz to minimize the effect of latency. Timings shown in Table 17 are valid for input frequencies below 5 kHz and  $f_{\rm system}$  of 25 MHz. Once the timings are satisfied according to Table 17, correct operation is guaranteed up to the maximum input frequency as specified in Table 26 on page 18.

| Parameter          | Description                                       | Condition *                          | min                        |

|--------------------|---------------------------------------------------|--------------------------------------|----------------------------|

| t <sub>setup</sub> | Index window setup time before rising edge of Z_W | no filter<br>8 average<br>16 average | 0.4 µs<br>0.5 µs<br>0.7 µs |

| t <sub>hold</sub>  | Index window hold time after falling edge of Z_W  | no filter<br>8 average<br>16 average | 0.4 μs<br>0.5 μs<br>0.7 μs |

\*) According to register FILTER(1:0) f<sub>system</sub> = 25 MHz, all timings scale with f<sub>system</sub>. Refer to Table 26 for more information

Table 17: Index gating and timing

Rev E2, Page 16/28

#### **CALIBRATION**

In order to facilitate system gain and offset calibration, two calibration modes can be enabled by either setting bit CALIB1 of register 0x01 or CALIB2 of register 0x0C.

| CALIB2   | Addr. 0x0C; bit 0                       | R/W |

|----------|-----------------------------------------|-----|

| CALIB1   | Addr. 0x01; bit 5                       | R/W |

| CALIB2;1 | Function, defaults to eeprom setting    |     |

| 00       | Normal operation, no calibration        |     |

| 01       | A/B gain and index calbration           |     |

| 10       | Oscillator and index window calibration |     |

| 11       | Not permitted                           |     |

Table 18: Calibration modes

#### A/B gain and offset calibration

In calibration mode 1 the SIN/COS input is directly passed through two zero-cross comparators to output pin A and B respectively. In addition, the sum of the input signals

$$\frac{SIN + COS}{\sqrt{2}}$$

is also fed through a comparator and driven on pin Z.

The actual calibration process must be carried out in several steps.

- 1. Select proper coarse gain by programming register GC(2:0). Set GFA(1:0) and GFB(1:0) to 0.

- 2. Adjust offset register OFSA(5:0) and OFSB(5:0) until output A and B are 50% duty cycle.

- 3. Adjust fine gain register GFA(1:0) and GFB(1:0) until output Z is equidistant between output A and B.

- 4. Repeat step 1 and 2 until no more improvement can be achieved.

Figure 10: Output signals for A/B gain and offset adjustment in calibration mode 1.

#### Oscillator and index window calibration

When calibration mode 2 is enabled, the output of the index comparator is driven on pin B\_V. In conjunction with the actual index output on pin Z\_W, the gating window can be centered around the output pulse (see Figure 9). Fine offset adjustment applied to the input of the index comparator is possible through OFSZ(3:0) which is sign magnitude encoded. This is beneficial when using small amplitude index sources such as an MR sensor.

Simultaneously, the oscillator frequency  $f_{osc}/32$  can be observed on pin A\_U. Register CLOCK(4:0) is used to tune the oscillator to its desired frequency.

| OFSZ(3:0) | Addr. 0x0B; bit 7:4                  | R/W |

|-----------|--------------------------------------|-----|

| Code      | Function, defaults to eeprom setting |     |

| 1111      | maximum negative adjust, -10.5 mV    |     |

| 1110      | -9 mV                                |     |

| 1001      | -1.5 mV                              |     |

|           |                                      |     |

| 1000      | no correction                        |     |

| 0000      | no correction                        |     |

| 0001      | 1.5 mV                               |     |

|           |                                      |     |

| 0110      | 9 mV                                 |     |

| 0111      | 10.5 mV                              |     |

| 1         | calibration mode 2 activated         |     |

Table 19: Index comparator offset control

| CLOCK(4:0) | Addr. 0x0A; bit 4:0                  | R/W |

|------------|--------------------------------------|-----|

| Code       | Function, defaults to eeprom setting |     |

| 00000      | Slowest clock                        |     |

|            |                                      |     |

| 11111      | fastest clock                        |     |

Table 20: Oscillator tuning

Rev E2, Page 17/28

#### **CONFIGURATION DEPENDENCIES**

This section describes the dependencies between the chip configuration and the system's performance. It is vital to understand the implication of system parameters to be able to tune the iC-TW2 for full performance. It is especially important to correctly program register FREQ(6:0), since this directly affects accuracy and maximum allowed input frequency.

| Selecting  | configuration | parameters |

|------------|---------------|------------|

| OCICCUITIN | comingulation | parameters |

To select a proper configuration follow the outlined procedure below. Refer to Table 26 for reference.

- 1. Determine the maximum input frequency  $f_{\text{in}()\text{max}}$  as required by the application.

- 2. Calculate  $f_{core}$  based on  $f_{in()max}$  and resolution INTER(7:0).

- 3. Select  $f_{system}$  based on the accuracy requirements. Accuracy is a function of resolution INTER(7:0) and clock scaling FREQ(6:0). Always use the highest accuracy possible to still satisfy  $f_{in0max}$ .

- 4. Determine  $f_{\text{osc}}$ . Selecting the slowest possible  $f_{\text{osc}}$  lowers power consumption and improves jitter performance.

#### Clock tuning

- 1. Observe  $f_{osc}/32$  on pin A\_U during calibration mode 2.

- 2. Use CLOCK(4:0) to tune the oscillator to the desired  $f_{cal}$  frequency. ( $f_{pinA} = f_{osc}/32$ )

- 3. Be aware that the oscillator can have as much as 20% frequency variation over the operating temperature range (-40 °C to 125 °C). The oscillator runs slower at higher temperatures. To guarantee performance at 125 °C it is necessary to tune the oscillator to typ. 12% higher frequency at room temperature of 25 °C.

#### **Accuracy modes**

The converter resolution INTER(7:0) in conjunction with the clock scaling FREQ(6:0) define iC-TW2's accuracy mode. Based on the selected accuracy mode other system parameters are defined as shown in Table 26.

| INTER(7:0)    | FREQ(6:0) | Accuracy      | Theoretical |

|---------------|-----------|---------------|-------------|

|               |           | Mode          | Absolute    |

|               |           |               | Accuracy    |