Rev F2, Page 1/62

#### **FEATURES**

- ♦ 3 chan. simultaneous sampling 13 bit sine-to-digital conversion

- ♦ Differential and single-ended PGA inputs to 200 kHz

- ♦ Input adaptation to current or voltage signals

- ♦ Adjustable signal conditioning for offset, amplitude and phase

- ♦ Input signal stabilization by LED or MR bridge supply tracking (via controlled 50 mA and 2 x 10 mA highside sources)

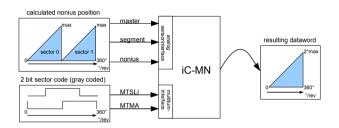

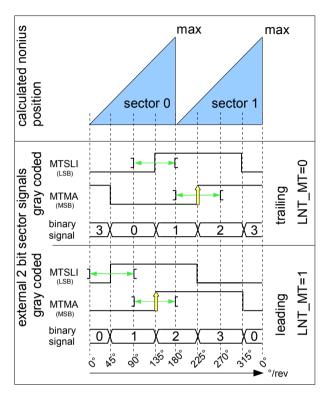

- ♦ 2 or 3 track nonius calculation of up to 25 bit singleturn position

- ♦ Data update within 7 µs supported by flash period counting

- ♦ Serial 2-wire interface to multiturn sensors (BiSS, SSI, 2-bit)

- ♦ Fast, serial I/O interface with fail-safe RS422 transceiver (SSI to 4 MHz, BiSS C to 10 MHz)

- ♦ Differential 1 Vpp sin/cos outputs to 100 Ω, short-circuit-proof

- ♦ Position preset function, selectable up/down code direction

- ♦ Signal and system monitoring with configurable error/warning messaging and diagnosis memory

- ♦ Device setup via I/O interface (BiSS) or serial EEPROM

- Reverse-polarity-proof and tolerant against faulty output wiring

- ♦ Power-good switch protecting the peripheral circuitry

- ♦ Single 5 V supply, operation from -40 to +110 °C

#### **APPLICATIONS**

- Multi-channel sine-to-digital converter

- Optical and magnetic position sensors

- Singleturn and multiturn absolute encoders

- Linear scales for absolute position

- ♦ Resolver systems

#### **PACKAGES**

QFN48-7x7

Rev F2, Page 2/62

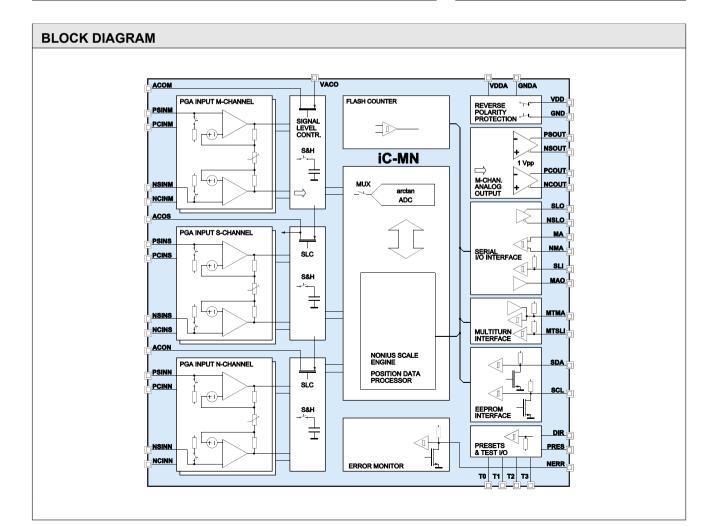

#### **DESCRIPTION**

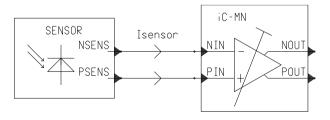

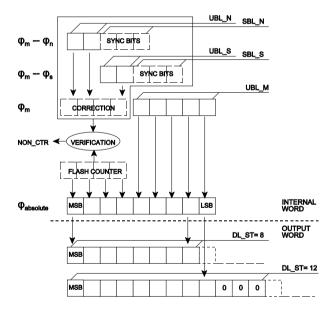

Encoder device iC-MN is a 3-channel, simultaneous sampling sine-to-digital converter which interpolates sine/cosine sensor signals using a high precision SAR converter with a selectable resolution of up to 13 bits. Each input has a separate sample-and-hold stage which halts the track signal for the subsequent sequential digitization. Various 2- and 3-track Vernier scale computations (after Nonius) can be configured for the calculation of high resolution angle positions; these computations permit angle resolutions of up to 25 bits.

The absolute angle position is output via the serial Interface with clock rates of up to 4 Mbit/s (SSI compatible; up to 10 Mbit/s with BiSS C protocol). The RS422 transceiver required to this end is integrated on the chip and has both a differential clock input and a differential line driver for data output.

Programmable instrumentation amplifiers with a selectable gain and offset and phase correction can be adjusted separately for each channel; these allow differential or single-ended input signals. At the same time the inputs can either be set to high impedance for voltage signals from magneto resistor sensor bridges, for example, or to low impedance for adaptation and use with photosensors which provide current signals, for instance. This enables the device to be directly connected up to a number of different optical and magnetic sensors.

For the purpose of input signal stabilization the conditioned signals are fed into signal level controllers featuring current source outputs of up to 50 mA (mas-

ter channel) and of up to 10 mA (for the nonius and segment channels each). These ACOx source pins either power the LEDs of an optical encoder or the magneto resistor bridges of a magnetic encoder. If the control thresholds are reached this event can be released for alarm messaging using the serial interface or the NERR output.

Both major chip functions and sensor errors are also monitored and can be enabled for alarm indication. In this manner typical sensor errors, such as signal loss due to wire breakage, short circuiting, dirt or aging, for example, can be signaled by alarms.

The device features further digital encoder functions covering the correction of phase errors between the tracks, for example, or the zeroing or presetting of a specific position offset for data output. Using the SSI master also integrated on the chip position data from multiturn sensors, provided by a second iC-MN, for example, can be read in and synchronized.

iC-MN is protected against a reversed power supply voltage; the integrated supply switch for loads of up to 20 mA extends this protection to cover the overall system. The device is configured via an external EEPROM.

The device described here is a multifunctional iC that contains integrated BiSS C interface components. The BiSS C process is protected by patent DE 10310622 B4 owned by iC-Haus GmbH and its application requires the conclusion of a license (free of charge).

Download the license at www.biss-interface.com/bua

Rev F2, Page 3/62

| 0 | ~~  | ıT  | 1   | re |

|---|-----|-----|-----|----|

| C | IJľ | 4 1 | N I | ıo |

| PACKAGING INFORMATION                             | 5  | Digital Frequency Monitoring                 | 32 |

|---------------------------------------------------|----|----------------------------------------------|----|

| PIN CONFIGURATION QFN48-7x7                       | 5  | S/D CONVERSION with MULTITURN                |    |

| ABSOLUTE MAXIMUM RATINGS                          | 6  | SYNCHRONIZATION                              | 33 |

|                                                   |    | Description Of Multiturn Operating Modes     | 33 |

| THERMAL DATA                                      | 6  | MODE_ST Code 0x0C                            | 33 |

| ELECTRICAL CHARACTERISTICS                        | -  | MODE_ST Code 0x0D                            | 33 |

| ELECTRICAL CHARACTERISTICS                        | 7  | MODE_ST Code 0x0E                            | 33 |

| OPERATING REQUIREMENTS                            | 15 | MODE_ST Code 0x0F                            | 33 |

| I/O Interface                                     | 15 | S/D CONVERSION with DIRECT OUTPUT            | 34 |

| CONFIGURATION PARAMETERS                          | 16 | Op. Mode Descriptions Of Direct Output Modes | 34 |

| CONTIONATION FARAMETERS                           | 10 | MODE_ST Code 0x0C                            | 34 |

| REGISTER MAP (EEPROM)                             | 17 | MODE_ST Code 0x0D                            | 34 |

|                                                   |    | MODE_ST Code 0x0E                            | 34 |

| OPERATING MODES and CALIBRATION PROCEDURES        | 21 | MODE_ST Code 0x0F                            | 34 |

| Calibration Using  Comparated Sine/Cosine Signals | 22 | TRACK OFFSET CALIBRATION                     | 35 |

| Comparated emorocomo orginalo i i i i             |    | I/O INTERFACE                                | 36 |

| SIGNAL CONDITIONING for MASTER-,                  |    | Protocol                                     | 36 |

| SEGMENT- and NONIUS-Channel (x= M,S,N)            |    | Output Data Length                           | 36 |

| Current Signals                                   | 23 | Output Options                               | 37 |

| Voltage Signals                                   | 23 |                                              |    |

| Gain Adjustment                                   | 23 | I/O INTERFACE with EXTENDED FUNCTIONS        | 38 |

| Offset Calibration                                | 24 | Protocol                                     | 38 |

| Phase Correction                                  | 26 | Output Data Length                           | 39 |

| ANALOG PARAMETERS                                 | 27 | Output Options                               | 39 |

| Signal Level Controller                           | 27 | Safety Application Settings                  | 40 |

| Bias Current Source                               | 28 | Busy Register                                | 40 |

| Temperature Sensor                                | 28 | CONFIGURATION OF DIGITAL DRIVER              |    |

| Signal Noise Filters                              | 28 | OUTPUTS                                      | 41 |

| SINE-TO-DIGITAL CONVERSION MODES                  | 29 | COMMAND and STATUS REGISTERS                 | 42 |

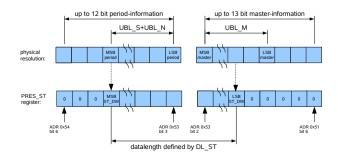

| Internal Bit Lengths                              | 29 | Execution Of Internal Commands               | 42 |

|                                                   |    | Execution Of Protocol Commands               | 42 |

| S/D CONVERSION with NONIUS CALCULATION            | 30 | Automatic Reset Function                     | 42 |

| Output Data Verification                          | 30 | Status Register                              | 43 |

| Op. Mode Descriptions Of Nonius Modes             | 30 | Non-Volatile Diagnosis Memory                | 43 |

| MODE_ST Codes 0x00, 0x01, 0x02                    | 30 |                                              |    |

| MODE_ST Codes 0x03, 0x04                          | 30 | ERROR AND WARNING BIT                        | 45 |

| MODE_ST Codes 0x05, 0x06, 0x7                     | 30 | Visibility Of Latched Status Messages        | 46 |

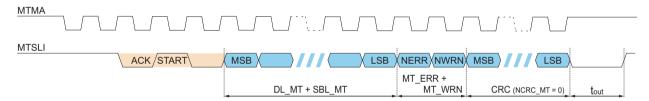

| MODE_ST Codes 0x08, 0x09, 0xA                     | 31 | MT INTERFACE                                 | 47 |

| MODE_ST Code 0x0B                                 | 31 | Configuration Of Data Lengths                | 47 |

| Principle PPR And Bit Length Dependencies         | 31 | Error Handling                               | 48 |

|                                            |    | Rev F2, Page                                                               | 4/62     |

|--------------------------------------------|----|----------------------------------------------------------------------------|----------|

| MT Interface with 2-bit mode               | 49 | Direct Addressing                                                          | 54<br>54 |

| MT INTERFACE with EXTENDED FUNCTIONS       | 50 | Daim viioo / taarooomig                                                    | •        |

| Direct Communication To Multiturn Sensor . | 50 | APPLICATION NOTES: Configuration As BiSS C-Slave Including EDS (Electronic |          |

| PRESET FUNCTION                            | 51 | Data Sheet)                                                                | 57       |

| STARTUP BEHAVIOR                           | 53 | APPLICATION NOTES: PLC Operation                                           | 58       |

|                                            |    | PLC Operation                                                              | 58       |

| Behaviour On Error During Startup          | 53 | ·                                                                          |          |

|                                            |    | <b>DESIGN REVIEW: Notes On Chip Functions</b>                              | 59       |

| EEPROM INTERFACE                           | 54 | ·                                                                          |          |

| Memory Map And Register Access             | 54 | REVISION HISTORY                                                           | 60       |

Rev F2, Page 5/62

#### **PACKAGING INFORMATION**

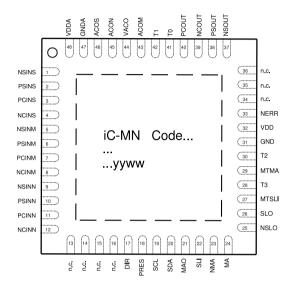

#### **PIN CONFIGURATION QFN48-7x7**

#### P

١

| PIN | FUNCTION     | ONS                             |

|-----|--------------|---------------------------------|

| No. | Name         | Function                        |

| 1   | NSINS        | Signal Input Sine - (Segment)   |

| 2   | <b>PSINS</b> | Signal Input Sine + (Segment)   |

| 3   | <b>PCINS</b> | Signal Input Cosine + (Segment) |

| 4   | NCINS        | Signal Input Cosine - (Segment) |

| 5   | NSINM        | Signal Input Sine - (Master)    |

| 6   | <b>PSINM</b> | Signal Input Sine + (Master)    |

| 7   | <b>PCINM</b> | Signal Input Cosine+ (Master)   |

| 8   | NCINM        | Signal Input Cosine - (Master)  |

| 9   | NSINN        | Signal Input Sine - (Nonius)    |

| 10  | <b>PSINN</b> | Signal Input Sine + (Nonius)    |

| 11  | <b>PCINN</b> | Signal Input Cosine + (Nonius)  |

| 12  | NCINN        | Signal Input Cosine - (Nonius)  |

| 13  | n.c.         |                                 |

| 14  | n.c.         |                                 |

| 15  | n.c.         |                                 |

Sense of Rotation Preselection Input, 17 DIR

Calibration Signal IPB

18 PRES Preset Input

16 n.c.

19 SCL EEPROM Interface, clock line EEPROM Interface, data line 20 SDA

#### DIN FUNCTIONS

| PIN | FUNCTIO | NS                                     |

|-----|---------|----------------------------------------|

| No. | Name    | Function                               |

| 21  | MAO     | I/O Interface, clock output            |

| 22  | SLI     | I/O Interface, data input              |

| 23  | NMA*    | I/O Interface, clock input -           |

| 24  | MA*     | I/O Interface, clock input +           |

| 25  | NSLO*   | I/O Interface, data output -           |

| 26  | SLO*    | I/O Interface, data output +           |

| 27  | MTSLI   | Multiturn Interface, data input        |

| 28  | T3      | External Trigger Input,                |

|     |         | Test Signal Input                      |

| 29  | MTMA    | Multiturn Interface, clock output      |

| 30  | T2      | Test Signal Input                      |

| 31  | GND*    | Ground                                 |

| 32  | VDD*    | +4.5 to 5.5 V Supply Voltage           |

| 33  | NERR*   | Error Message Output,                  |

|     |         | System Error Message Input             |

| 34  | n.c.    |                                        |

| 35  | n.c.    |                                        |

| 36  | n.c.    |                                        |

|     | NSOUT*  | Analog Output Sine - (Master)          |

|     | PSOUT*  | Analog Output Sine + (Master)          |

| 39  | NCOUT*  | Analog Output Cosine - (Master)        |

| 40  | PCOUT*  | Analog Output Cosine + (Master)        |

| 41  | T0      | Test Signal Output                     |

| 42  | T1      | Test Signal Output                     |

|     | ACOM*   | Signal Level Controller Outp. (Master) |

| 44  | VACO*   | +4.5 to 5.5 V Signal Level Controller  |

|     |         | Supply                                 |

|     | ACON*   | Signal Level Controller Output         |

| 46  | ACOS*   | Signal Level Controller Output,        |

|     |         | VREFin Ref. Voltage Input/Output       |

|     | GNDA    | Sub-System Ground Output               |

| 48  | VDDA    | Sub-System Positive Supply Output      |

|     | *:      | Pin is immune against faulty output    |

|     |         | or supply connection                   |

or supply connection.

n.c. : Pin is not connected.

Connecting pin VACO to VDD is mandatory. Wiring unused input pins can be recommended, especially for pins SLI, DIR, PRES and T2 (to GNDA). For calibrating the internal bias current source a pull-down resistor of  $5 \, \text{k}\Omega$  $\pm 1$  % connected from pin DIR to GNDA is useful (see Figure 10).

To improve heat dissipation the thermal pad of the QFN package (bottom side) should be joined to an extended copper area which must have GNDA potential.

Rev F2, Page 6/62

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol  | Parameter                                                                                                                                                                                              | Conditions                            |      |      | Unit |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------|------|

| No.  |         |                                                                                                                                                                                                        |                                       | Min. | Max. |      |

| G001 | V()     | Voltage at VDD, GND, NSLO, SLO,<br>NERR, PSOUT, NSOUT, PCOUT,<br>NCOUT, VACO                                                                                                                           | referenced to GND                     | -6   | 6    | V    |

| G002 | V()     | Voltage at MA, NMA                                                                                                                                                                                     | referenced to GND                     | -9   | 14   | V    |

| G003 | V()     | Pin-to-Pin Voltage vs. VDD, GND,<br>NSLO, SLO, NERR, PSOUT, NSOUT,<br>PCOUT, NCOUT, VACO                                                                                                               |                                       |      | 6    | V    |

| G004 | V()     | Voltage at NSINS, PSINS, PCINS,<br>NCINS, NSINM, PSINM, PCINM,<br>NCINM, NSINN, PSINN, PCINN,<br>NCINN, DIR, PRES, SCL, SDA, MAO,<br>SLI, MTSLI, T2, MTMA, T3, T0, T1,<br>ACOM, ACON, ACOS, GNDA, VDDA | referenced to AGND, V() < VDD + 0.3 V | -0.3 | 6    | V    |

| G005 | I(VDD)  | Current in VDD                                                                                                                                                                                         |                                       | -100 | 400  | mA   |

| G006 | I()     | Current in VDDA, GNDA, PSOUT, NSOUT, PCOUT, NCOUT                                                                                                                                                      |                                       | -50  | 50   | mA   |

| G007 | I()     | Current in PSINM, NSINM, PCINM,<br>NCINM, PSINS, NSINS, PCINS,<br>NCINS, PSINN, NSINN, PCINN,<br>NCINN, DIR, PRES, SCL, SDA, MAO,<br>SLI, T3, T2, NERR, T0, T1                                         |                                       | -20  | 20   | mA   |

| G008 | I()     | Current in SLO, NSLO, VACO                                                                                                                                                                             |                                       | -120 | 120  | mA   |

| G009 | I()     | Current in MA, NMA                                                                                                                                                                                     |                                       | -0.6 | 1    | mA   |

| G010 | I(ACOM) | Current in ACOM                                                                                                                                                                                        |                                       | -100 | 20   | mA   |

| G011 | I()     | Current in ACOS, ACON                                                                                                                                                                                  |                                       | -50  | 20   | mA   |

| G012 | Vd()    | ESD Susceptibility at all pins                                                                                                                                                                         | HBM 100 pF discharged through 1.5 kΩ  |      | 2    | kV   |

| G013 | Tj      | Junction Temperature                                                                                                                                                                                   |                                       | -40  | 150  | °C   |

| G014 | Ts      | Storage Temperature Range                                                                                                                                                                              |                                       | -40  | 150  | °C   |

#### THERMAL DATA

Operating conditions: VDD =  $5 V \pm 10 \%$

| Item | Symbol | Parameter                           | Conditions                                             |      |      |      | Unit |

|------|--------|-------------------------------------|--------------------------------------------------------|------|------|------|------|

| No.  |        |                                     |                                                        | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range | package QFN48-7x7                                      | -40  |      | 110  | °C   |

| T02  | Rthja  |                                     | QFN48-7x7 surface mounted to PCB according to JEDEC 51 |      | 30   |      | K/W  |

Rev F2, Page 7/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = - $40...125 \,^{\circ}\text{C}$ , IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| Item<br>No. | Symbol       | Parameter                                                             | Conditions                                                                                                  | Min.                     | Тур.                     | Max.                           | Unit                 |

|-------------|--------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------------|----------------------|

| Total       | Device       |                                                                       |                                                                                                             | U                        |                          |                                |                      |

| 001         | VDD,<br>VACO | Permissible Supply Voltage                                            |                                                                                                             | 4.5                      |                          | 5.5                            | V                    |

| 002         | I(VDD)       | Supply Current in VDD                                                 | Tj = 27 °C, no load                                                                                         |                          | 45                       | 60                             | mA                   |

| 003         | I(VDDA)      | Permissible Load Current at VDDA                                      |                                                                                                             | -20                      |                          | 0                              | mA                   |

| 004         | Vc()hi       | Clamp Voltage hi<br>(all pins with the exception of MA,<br>NMA)       | Vc()hi = V() — VDD, I() = 1 mA                                                                              | 0.4                      |                          | 1.5                            | V                    |

| 005         | Vc()hi       | Clamp Voltage hi MA, NMA                                              | Vc()hi = V() - VDD, I() = 10 mA                                                                             | 12.5                     |                          | 16                             | V                    |

| 006         | Vc()lo       | Clamp Voltage Io<br>(all pins with the exception of<br>VDDA, MA, NMA) | I() = -1 mA                                                                                                 | -1.5                     |                          | -0.3                           | V                    |

| 007         | Vc()lo       | Clamp Voltage lo at VDDA                                              | I() = -1 mA                                                                                                 | -1.5                     |                          | -0.2                           | V                    |

| 800         | Vc()lo       | Clamp Voltage lo at MA, NMA                                           | I() = -10 mA                                                                                                | -17                      |                          | -10                            | V                    |

| Signa       | I Conditioni | ng and Inputs: PSINx, NSINx, PC                                       | CINX, NCINX (X = M, S, N)                                                                                   |                          |                          |                                |                      |

| 101         | Vin()sig     | Permissible V-Mode Input<br>Voltage                                   | UIN = 1, TUIN = 0<br>UIN = 1, TUIN = 1, DCPOS = 1                                                           | 0.75<br>-0.1             |                          | VDDA<br>- 1.5<br>VDDA +<br>0.1 | V                    |

| 102         | lin()        | V-Mode Input Current                                                  | UIN = 1, TUIN = 0                                                                                           | -100                     |                          | 100                            | nA                   |

| 103         | Rin()        | V-Mode Input Resistance                                               | vs. VREFin, Tj = 27 °C, UIN = 1, TUIN = 1                                                                   | 16.4                     | 20                       | 23.6                           | kΩ                   |

| 104         | lin()sig     | Permissible I-Mode Input Current                                      | UIN = 0;<br>DCPOS = 0<br>DCPOS = 1                                                                          | -10<br>10                |                          | -300<br>300                    | μA<br>μA             |

| 105         | SCR()        | Permissible Signal Contrast Ratio                                     | ratio of lin()pk vs. lin()dc                                                                                | 0.125                    |                          | 1                              |                      |

| 106         | Rin()        | I-Mode Input Resistance                                               | Tj = 27 °C, vs. VREFin;<br>UIN = 0, RIN = 00<br>UIN = 0, RIN = 01<br>UIN = 0, RIN = 10<br>UIN = 0, RIN = 11 | 1.1<br>1.6<br>2.2<br>3.2 | 1.6<br>2.3<br>3.2<br>4.6 | 2.1<br>3.0<br>4.2<br>6.0       | kΩ<br>kΩ<br>kΩ<br>kΩ |

| 107         | TCRin        | Temperature Coefficient Rin                                           |                                                                                                             |                          | 0.15                     |                                | %/K                  |

| 108         | VREFin       | Input Reference Voltage                                               | DCPOS = 1<br>DCPOS = 0                                                                                      | 1.35<br>2.25             | 1.5<br>2.5               | 1.65<br>2.75                   | V                    |

| 110         | Vin()diff    | Recommended Differential Input<br>Voltage                             | Vin()diff = V(PSINx) - V(NSINx),<br>Vin()diff = V(PCINx) - V(NCINx);<br>TUIN = 0<br>TUIN = 1                | 20<br>80                 |                          | 1000<br>4000                   | mVpp<br>mVpp         |

| 111         | Vcore()      | Recommended Internal Signal Level                                     | G * Vin()diff                                                                                               |                          | 6                        |                                | Vpp                  |

| 112         | GF, GC       | Selectable Gain Factors                                               | TUIN = 0<br>TUIN = 1                                                                                        | 6<br>1.5                 |                          | 300<br>75                      |                      |

| 113         | ∆GFdiff      | Differential Gain Accuracy (Master)                                   | referenced to fine gain range                                                                               | -1                       |                          | 1                              | LSB                  |

| 114         | ∆GFdiff      | Differential Gain Accuracy (Segment, Nonius)                          | referenced to fine gain range                                                                               | -2                       |                          | 2                              | LSB                  |

| 115         | ∆GFSabs      | Absolute Gain Accuracy Sine (Master)                                  | referenced to fine gain range, guaranteed monotony                                                          | -20                      |                          | 20                             | LSB                  |

| 116         | ∆GFCabs      | Absolute Gain Accuracy Cosine (Master)                                | referenced to fine gain range, guaranteed monotony                                                          | -1                       |                          | 1                              | LSB                  |

| 117         | ∆GFSabs      | Absolute Gain Accuracy Sine (Segment, Nonius)                         | referenced to fine gain range, guaranteed monotony                                                          | -20                      |                          | 20                             | LSB                  |

| 118         | ∆GFCabs      | Absolute Gain Accuracy Cosine (Segment, Nonius)                       | referenced to fine gain range, guaranteed monotony                                                          | -1                       |                          | 1                              | LSB                  |

| 119         | ∆GCabs       | Gain Accuracy                                                         | referenced to coarse gain range                                                                             | -8                       |                          | 8                              | %                    |

Rev F2, Page 8/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = - $40...125 \,^{\circ}\text{C}$ , IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| ltem<br>No. | Symbol           | Parameter                                                                | Conditions                                                                                                                               | Min.  | Тур.                              | Max. | Unit           |

|-------------|------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|------|----------------|

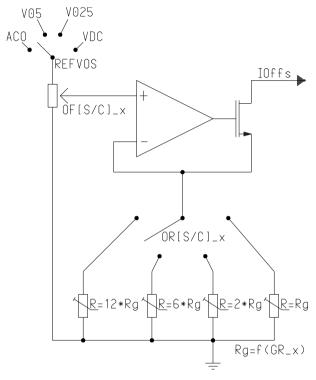

| 120         | VOScal           | Offset Calibration Range                                                 | measured at output, source V(ACOx) = 3 V, REFVOS = 00; ORS_X/ORC_x = 00 ORS_X/ORC_x = 01 ORS_X/ORC_x = 10 ORS_X/ORC_x = 11               |       | ±450<br>±900<br>±2700<br>±5400    |      | mV<br>mV<br>mV |

| 121         | VOScal2          | Offset Calibration Range                                                 | measured at output, source V05, REFVOS = 01; ORS_x/ORC_x = 00 ORS_x/ORC_x = 01 ORS_x/ORC_x = 10 ORS_x/ORC_x = 11                         |       | ±1500<br>±3000<br>±9000<br>±18000 |      | mV<br>mV<br>mV |

| 122         | VOScal3          | Offset Calibration Range                                                 | measured at output, source V025, REFVOS = 10; ORS_x/ORC_x = 00 ORS_x/ORC_x = 01 ORS_x/ORC_x = 10 ORS_x/ORC_x = 11                        |       | ±750<br>±1500<br>±4500<br>±9000   |      | mV<br>mV<br>mV |

| 123         | VOScal4          | Offset Calibration Range                                                 | measured at output, source VDC = 125 mV,<br>REFVOS = 11;<br>ORS_x/ORC_x = 00<br>ORS_x/ORC_x = 01<br>ORS_x/ORC_x = 10<br>ORS_x/ORC_x = 11 |       | ±375<br>±750<br>±2250<br>±4500    |      | mV<br>mV<br>mV |

| 124         | $\Delta$ VOSdiff | Differential Linearity Error of Offset Correction Master                 |                                                                                                                                          | -0.5  |                                   | 0.5  | LSB            |

| 125         | $\Delta$ VOSdiff | Differential Linearity Error of Off-<br>set Correction Segment, Nonius   |                                                                                                                                          | -2    |                                   | 2    | LSB            |

| 126         | △VOSint          | Integral Linearity Error of Offset<br>Correction Master                  |                                                                                                                                          | -100  |                                   | 100  | LSB            |

| 127         | △VOSint          | Integral Linearity Error of Offset Correction Segment, Nonius            |                                                                                                                                          | -100  |                                   | 100  | LSB            |

| 128         | PHIcal           | Phase Correction Range                                                   | sine vs. cosine signal                                                                                                                   |       | ±10.4                             |      | ۰              |

| 129         | ΔPHIdiff         | Differential Linearity Error of<br>Phase Correction Master               |                                                                                                                                          | -0.25 |                                   | 0.25 | LSB            |

| 130         | ΔPHIdiff         | Differential Linearity Error of<br>Phase Correction Segment, Non-<br>ius |                                                                                                                                          | -2    |                                   | 2    | LSB            |

| 131         | ∆PHlint          | Integral Linearity Error of Phase Correction Master                      |                                                                                                                                          | -20   |                                   | 20   | LSB            |

| 132         | ∆PHlint          | Integral Linearity Error of Phase Correction Segment, Nonius             |                                                                                                                                          | -20   |                                   | 20   | LSB            |

| 133         | fin()max         | Permissible Input Frequency                                              | angle accuracy better 8 bit                                                                                                              | 200   |                                   |      | kHz            |

| 134         | fhc()            | Input Amplifier Cut-off Frequency (-3 dB)                                |                                                                                                                                          | 250   |                                   |      | kHz            |

Rev F2, Page 9/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = -40...125 °C, IBP calibrated to 200 µA, reference point GNDA (GND for digital I/O pins), unless otherwise stated

| ltem<br>No. | Symbol     | Parameter                                               | Conditions                                                                                                                                                     | Min.                      | Тур.                      | Max.                    | Unit                 |

|-------------|------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|-------------------------|----------------------|

| Signa       | Level Cont | roller: ACOM                                            |                                                                                                                                                                | II                        | , ,,                      |                         |                      |

| 401         | Vs()hi     | Saturation Voltage hi                                   | Vs()hi = V(VACO) - V();<br>ACOR_M(6:5) = 00, I() = -5 mA<br>ACOR_M(6:5) = 01, I() = -10 mA<br>ACOR_M(6:5) = 10, I() = -25 mA<br>ACOR_M(6:5) = 11, I() = -50 mA |                           |                           | 1<br>1<br>1             | V<br>V<br>V          |

| 402         | Isc()hi    | Short-circuit Current hi                                | V() = 0V(VACO) - 1V;<br>ACOR_M(6:5) = 00<br>ACOR_M(6:5) = 01<br>ACOR_M(6:5) = 10<br>ACOR_M(6:5) = 11                                                           | -9.5<br>-19<br>-46<br>-85 | -7<br>-14.5<br>-36<br>-73 | -5<br>-10<br>-25<br>-50 | mA<br>mA<br>mA<br>mA |

| 403         | llk()      | Residual Current With Reversed Supply                   |                                                                                                                                                                |                           |                           | 50                      | μA                   |

| 404         | Tctrl      | Control Time Constant                                   | control to sine square or sum                                                                                                                                  |                           | 1.6                       |                         | ms                   |

| 405         | Vpk()avg   | Controlled Differential S/C Signal Amplitude (averaged) | square control: ACOT_M(8:7) = 00,<br>Op.mode ANA_M                                                                                                             | 2.7                       | 3                         | 3.3                     | V                    |

| 406         | Vt()min    | Signal Monitoring AM_Min                                | referrend to Vscq() = SQRT of [V(PSOUT) - V(NSOUT)] <sup>2</sup> ++ [V(PCOUT) - V(NCOUT)] <sup>2</sup>                                                         |                           | 40                        |                         | %                    |

| 407         | Vt()max    | Signal Monitoring AM_Max                                | referred to Vscq(), see 406                                                                                                                                    |                           | 135                       |                         | %                    |

| 408         | It()min    | Control Monitoring ACM_Min                              | referenced to range ACOR_M()                                                                                                                                   |                           | 3                         |                         | %lsc                 |

| 409         | It()max    | Control Monitoring ACM_Max                              | referenced to range ACOR_M()                                                                                                                                   |                           | 90                        |                         | %lsc                 |

| 410         | t()set     | Settling time                                           | MN Y5: t()set after tbusy()cfg (D09)                                                                                                                           |                           | 3                         |                         | ms                   |

| Signa       | Level Cont | roller: ACOS, ACON                                      |                                                                                                                                                                | "                         |                           |                         |                      |

| 501         | Vs()hi     | Saturation Voltage hi                                   | Vs()hi = V(VACO) — V();<br>ACOR_x(5) = 0, I() = -5 mA<br>ACOR_x(5) = 1, I() = -10 mA                                                                           |                           |                           | 1 1                     | V                    |

| 502         | Isc()hi    | Short-circuit Current hi                                | V() = 0V(VACO) - 1V;<br>ACOR_x(5) = 0<br>ACOR_x(5) = 1                                                                                                         | -9.5<br>-19               | -7<br>-14.5               | -5<br>-10               | mA<br>mA             |

| 503         | llk()      | Residual Current with Reverse Polarity                  |                                                                                                                                                                |                           |                           | 50                      | μA                   |

| 504         | Tctrl      | Control Time Constant                                   | control to sine square or sum                                                                                                                                  |                           | 1.6                       |                         | ms                   |

| 505         | Vpk()avg   | Controlled Differential S/C Signal Amplitude (averaged) | square control: ACOT_x(7:6) = 00, operating mode ANA_x                                                                                                         | 2.4                       | 3                         | 3.6                     | V                    |

| 506         | Vt()min    | Signal Monitoring AN_Min,<br>AS_Min                     | referred to Vscq() = SQRT of [V(PSOUT) - V(NSOUT)] <sup>2</sup> + [V(PCOUT) - V(NCOUT)] <sup>2</sup>                                                           |                           | 40                        |                         | %                    |

| 507         | Vt()max    | Signal Monitoring AN_Max,<br>AS_Max                     | referred to Vscq(), see 506                                                                                                                                    |                           | 135                       |                         | %                    |

| 508         | It()min    | Control Monitoring ACN_Min, ACS_Min                     | referenced to range ACOR_x()                                                                                                                                   |                           | 3                         |                         | %Isc                 |

| 509         | It()max    | Control Monitoring ACN_Max, ACS_Max                     | referenced to range ACOR_x()                                                                                                                                   |                           | 90                        |                         | %Isc                 |

| 510         | Vin(ACOS)  | Permissible Ref. Input Voltage at ACOS                  | CVREF = 11                                                                                                                                                     | 0.75                      |                           | VDDA<br>– 2             | V                    |

Rev F2, Page 10/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = -40...125 °C, IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| ltem<br>No. | Symbol       | Parameter                                                                     | Conditions                                                                                                                         | Min. | Тур.                                                                     | Max.  | Unit                                   |

|-------------|--------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------|-------|----------------------------------------|

| Samp        | le-&-Hold S  | tage, Signal Filter and Sine-To-Di                                            | gital Conversion                                                                                                                   |      |                                                                          |       |                                        |

| 601         | fc1()        | Cut-off Frequency of M/S/N<br>Channel Signal Filter<br>(-3 dB lowpass filter) | ENF(1) = 1;<br>fin (master channel) < 20 Hz<br>fin (master channel) > 1300 Hz                                                      |      | 4<br>300                                                                 |       | kHz<br>kHz                             |

| 602         | amax         | Permissible Angle Acceleration for 3(2) track nonius calculation              | ENF(1) = 1                                                                                                                         |      | 1000                                                                     |       | Mrad/s <sup>2</sup>                    |

| 603         | AAabs        | Absolute Angular Accuracy                                                     | Used bit length UBL_x = 0x0D: 13 bit                                                                                               |      | ±2                                                                       |       | LSB                                    |

| 604         | AAR          | Repeatability                                                                 |                                                                                                                                    |      | ±1                                                                       |       | LSB                                    |

| 605         | tenv         | Conversion Time (1 Channel)                                                   | Used bit length UBL_M, respectively UBL_x + SBL_x (with x = S, N): 13 bit 12 bit 11 bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit |      | 4.25<br>3.88<br>3.5<br>3.13<br>2.75<br>2.5<br>2.25<br>2.0<br>1.75<br>1.5 |       | hs<br>hs<br>hs<br>hs<br>hs<br>hs<br>hs |

| 606         | trec()       | Recovery Time Sampling-to-Sampling                                            | termination of calculation and synchronization (Nonius or MT modes) to follow-up S&H trigger                                       |      |                                                                          | 1.25  | μs                                     |

| Analo       | g Line Drive | er Outputs: PSOUT, NSOUT, PCO                                                 | UT, NCOUT                                                                                                                          |      |                                                                          |       |                                        |

| 701         | Vout()       | Output Amplitude                                                              | RLdiff = $100 \Omega$ , VDD = $4.5 V$ ,<br>DC level = VDD/2                                                                        |      |                                                                          | 300   | mV                                     |

| 702         | Vpk()        | Differential Output Amplitude with Signal Level Control by ACOM               | square control: ACOT_M(8:7) = 00, Op.mode normal                                                                                   | 450  | 500                                                                      | 550   | mV                                     |

| 703         | fc2()        | Cut-off Frequency of Line Driver<br>Signal Filter<br>(-3 dB low-pass filter)  | ENF(0) = 1;<br>fin (master channel) < 20 Hz<br>fin (master channel) > 1300 Hz                                                      |      | 8<br>600                                                                 |       | kHz<br>kHz                             |

| 704         | fc3()        | Cut-off Frequency of Line Driver (-3 dB)                                      | CL = 500 pF, Vpp = 0.5 V, ENF0 = 1                                                                                                 | 500  |                                                                          |       | kHz                                    |

| 705         | Voffs()      | Offset Voltage                                                                |                                                                                                                                    | -8   |                                                                          | 8     | mV                                     |

| 706         | Isc()hi      | Short-circuit Current hi                                                      | V()= GND                                                                                                                           | -40  | -20                                                                      | -15   | mA                                     |

| 707         | Isc()lo      | Short-circuit Current lo                                                      | V() = VDD                                                                                                                          | 15   | 20                                                                       | 40    | mA                                     |

| 708         | SR()         | Slew Rate                                                                     | RLdiff = $100 \Omega$ , CL = $25 pF$                                                                                               |      | 5                                                                        |       | V/µs                                   |

| 709         | llk()        | Residual Current with Reverse Polarity                                        |                                                                                                                                    | -50  |                                                                          | 50    | μA                                     |

| 710         | Vout()err    | Output Signal with Temperature Error                                          | VTs > VTth                                                                                                                         |      | 50                                                                       |       | %VDD                                   |

| 711         | Rout()       | Output Impedance                                                              | Op.Mode ANA_M, ANA_N, ANA_S                                                                                                        | 2    | 4                                                                        | 8     | kΩ                                     |

| 712         | fout()cal    | Permissible Output Frequency<br>During Calibration                            | Op.Mode ANA_M, ANA_N, ANA_S;<br>CL = 200 pF                                                                                        |      |                                                                          | 2     | kHz                                    |

| Bias (      | Current Sou  | rce and Reference Voltages                                                    |                                                                                                                                    |      |                                                                          | ,     |                                        |

| 801         | IBP          | Bias Current Source                                                           | IBP calibrated to 200 μA                                                                                                           | 92.5 | 100                                                                      | 107.5 | %                                      |

| 802         | VPAH         | Reference Voltage VPAH                                                        | referenced to GNDA                                                                                                                 | 48   | 50                                                                       | 52    | %VDD                                   |

| 803         | V05          | Reference Voltage V05                                                         | referenced to GNDA                                                                                                                 | 460  | 512                                                                      | 570   | mV                                     |

| 804         | V025         | Reference Voltage V025                                                        | referenced to GNDA                                                                                                                 |      | 50                                                                       |       | %V05                                   |

Rev F2, Page 11/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = -40...125 °C, IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| Item  | Symbol            | Parameter                                    | Conditions                                                                                        |                   |                   |                   | Unit           |

|-------|-------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|----------------|

| No.   |                   |                                              |                                                                                                   | Min.              | Тур.              | Max.              |                |

|       | r-Down-Res        | 1                                            | T.                                                                                                | 1                 |                   |                   | 1              |

| 901   | VDDon             | Turn-on Threshold VDD (power on release)     | increasing voltage VDD                                                                            | 3.9               | 4.25              | 4.5               | V              |

| 902   | VDDoff            | Turn-off Threshold VDD (power down reset)    | decreasing voltage VDD                                                                            | 3.4               | 3.75              | 4.2               | V              |

| 903   | VDDhys            | Hysteresis                                   | VDDhys = VDDon — VDDoff                                                                           | 400               |                   |                   | mV             |

| 904   | tready()cfg       | Operation Start-Up Time                      | includes tbusy()cfg;<br>MODE_MT = 00<br>MODE_MT ≠ 00                                              |                   | 21<br>29          |                   | ms<br>ms       |

| Clock | Oscillator        |                                              |                                                                                                   |                   |                   |                   |                |

| A01   | fosc              | Clock Frequency                              | presented at pin SCL with subdivision of 128                                                      | 5.6               | 8                 | 9.92              | MHz            |

| Suppl | y Switch an       | d Reverse Polarity Protection: V             | DDA, GNDA                                                                                         |                   |                   |                   | ,              |

| B01   | Vs()              | Switch Drop-Off Voltage vs. VDD (unloaded)   | V() = V(VDD) - V(VDDA), I(VDDA) = 0                                                               |                   | 115               |                   | mV             |

| B02   | Rs()              | VDDA Switch On-Resistance                    | VDD vs. VDDA, load current to 20 mA                                                               | 5                 | 10                | 20                | Ω              |

| B03   | Vs()              | Switch Drop-Off Voltage vs. GNDA (unloaded)  | V() = V(GNDA) - V(GND), I(GNDA) = 0                                                               |                   | 105               |                   | mV             |

| B04   | Rs()              | GNDA Switch On-Resistance                    | ground current to 20 mA                                                                           | 1                 | 3.8               | 7                 | Ω              |

| Temp  | erature Mon       | itoring                                      | ,                                                                                                 |                   |                   |                   | 1              |

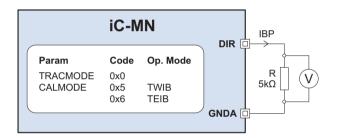

| C01   | VTSw              | Sensor Voltage for Warning<br>Temperature    | VTSw() = VDDA - V(T1), Tj = 27 °C, operating mode TWIB                                            | 610               | 640               | 670               | mV             |

| C02   | VTSe              | Sensor Voltage for Shutdown<br>Temperature   | VTSe() = VDDA — V(T1), Tj = 27 °C, operating mode TEIB                                            | 635               | 665               | 695               | mV             |

| C03   | TCs               | Sensor Voltage Temperature<br>Coefficient    |                                                                                                   |                   | -1.95             |                   | mV/K           |

| C04   | VTth              | Activation Threshold<br>Temperature Warning  | VTth() = VDDA - V(T0), Tj = 27 °C;<br>CFGTA(4:0) = 0x00<br>CFGTA(4:0) = 0x0F<br>CFGTA(4:0) = 0x1F | 225<br>400<br>585 | 285<br>498<br>725 | 355<br>615<br>895 | mV<br>mV<br>mV |

| C05   | TCth              | Activation Threshold Temperature Coefficient |                                                                                                   |                   | 1.32              |                   | ‰/K            |

| C06   | Thys <sub>w</sub> | Warning Temperature Hysteresis               |                                                                                                   | 4                 | 15                | 19                | °C             |

| C07   | ΔΤ                | Relative Shutdown Temperature                | $\Delta T = Te - Tw$                                                                              | 5                 | 15                | 20                | °C             |

| C08   | Thyse             | Shutdown Temperature Hysteresis              |                                                                                                   | 9                 | 30                | 39                | °C             |

| EEPR  | OM Interfac       | e: SCL, SDA                                  |                                                                                                   |                   |                   |                   |                |

| D01   | Vs()lo            | Saturation Voltage Io                        | I() = 4 mA                                                                                        |                   |                   | 450               | mV             |

| D02   | lsc()lo           | Short-circuit Current lo                     |                                                                                                   | 4                 |                   | 60                | mA             |

| D03   | Vt()hi            | Input Threshold Voltage hi                   |                                                                                                   |                   |                   | 2                 | V              |

| D04   | Vt(lo)            | Input Threshold Voltage lo                   |                                                                                                   | 800               |                   |                   | mV             |

| D05   | Vt()hys           | Input Hysteresis                             | Vt(hys) = Vt()hi - Vt()lo                                                                         | 100               | 250               |                   | mV             |

| D06   | lpu()             | Input Pull-up Current                        | V() = 0VDD - 1 V                                                                                  | -750              | -300              | -60               | μA             |

| D07   | Vpu()             | Input Pull-up Voltage                        | Vpu() = VDD — V(), I() = -5 μA                                                                    |                   |                   | 400               | mV             |

| D08   | fclk(SCL)         | Clock Frequency                              |                                                                                                   | 43.75             | 62.5              | 77.5              | kHz            |

| D09   | tbusy()cfg        | Duration Of Startup Configuration            | error free EEPROM access                                                                          |                   | 13                | 15                | ms             |

Rev F2, Page 12/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ W}$ , Tj =  $-40...125 \,^{\circ}\text{C}$ , IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| ltem    | Symbol      | Parameter                                                | Conditions                                                                                                                                                                                  |                          |                                               |                          | Unit                 |

|---------|-------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------|--------------------------|----------------------|

| No.     |             | 00 Line Delever Outroote 01 0 NO                         |                                                                                                                                                                                             | Min.                     | Тур.                                          | Max.                     |                      |

| E01     | 1           | 22 Line Driver Outputs SLO, NSI<br>Saturation Voltage hi |                                                                                                                                                                                             |                          |                                               |                          |                      |

| EUI     | Vs()hi      | Saturation voltage in                                    | Vs() = VDD - V();<br>DSC(1:0) = 11, I() = -1.2 mA<br>DSC(1:0) = 10, I() = -4 mA<br>DSC(1:0) = 01, I() = -20 mA<br>DSC(1:0) = 00, I() = -50 mA                                               |                          |                                               | 200<br>200<br>400<br>900 | mV<br>mV<br>mV       |

| E02     | Vs()lo      | Saturation Voltage lo                                    | DSC(1:0) = 11, I() = 1.2 mA<br>DSC(1:0) = 10, I() = 4 mA<br>DSC(1:0) = 01, I() = 20 mA<br>DSC(1:0) = 00, I() = 50 mA                                                                        |                          |                                               | 200<br>200<br>400<br>900 | mV<br>mV<br>mV       |

| E03     | lsc()hi     | Short-circuit Current hi                                 | V() = 0 V;<br>DSC(1:0) = 11<br>DSC(1:0) = 10<br>DSC(1:0) = 01<br>DSC(1:0) = 00                                                                                                              | -3<br>-10<br>-45<br>-120 |                                               | -1.2<br>-4<br>-20<br>-50 | mA<br>mA<br>mA<br>mA |

| E04     | Isc()lo     | Short-circuit Current lo                                 | V() = VDD<br>DSC(1:0) = 11<br>DSC(1:0) = 10<br>DSC(1:0) = 01<br>DSC(1:0) = 00                                                                                                               | 1.2<br>4<br>20<br>50     |                                               | 3<br>10<br>45<br>120     | mA<br>mA<br>mA<br>mA |

| E05     | IIk()tri    | Tristate Leakage Current                                 | DTRI(1:0) = 11                                                                                                                                                                              | -10                      |                                               | 10                       | μA                   |

| E06     | tr()        | Rise Time hi                                             | RL = $100 \Omega$ to GND, DSC(1:0) = 00;<br>DSR(1:0) = 00<br>DSR(1:0) = 01<br>DSR(1:0) = 10<br>DSR(1:0) = 11                                                                                | 10<br>22<br>60<br>250    |                                               | 30<br>40<br>140<br>350   | ns<br>ns<br>ns       |

| E07     | tf()        | Fall Time lo                                             | RL = 100 Ω to VDD, DSC(1:0) = 00;<br>DSR(1:0) = 00<br>DSR(1:0) = 01<br>DSR(1:0) = 10<br>DSR(1:0) = 11                                                                                       | 5<br>22<br>60<br>250     |                                               | 15<br>40<br>140<br>350   | ns<br>ns<br>ns<br>ns |

| E08     | llk()       | Residual Current with Reverse Polarity                   |                                                                                                                                                                                             | -100                     |                                               | 100                      | μA                   |

| I/O Int | erface: RS4 | 22 Line Receiver MA, NMA                                 |                                                                                                                                                                                             |                          |                                               |                          |                      |

| F01     | Vin()       | Permissible Input Voltage                                |                                                                                                                                                                                             | -7                       |                                               | 12                       | V                    |

| F02     | Rin()       | Input Resistance                                         | MA vs. GND, NMA vs. GND                                                                                                                                                                     | 15                       | 20                                            | 25                       | kΩ                   |

| F03     | Vhys()      | Differential Input Hysteresis                            | Vhys() = (V(MA) - V(NMA)) / 2                                                                                                                                                               | 50                       |                                               | 200                      | mV                   |

| F04     | Vt()hi      | Input Threshold Voltage hi at MA                         | pin NMA open                                                                                                                                                                                |                          |                                               | 2                        | V                    |

| F05     | Vt()lo      | Input Threshold Voltage lo at MA                         | pin NMA open                                                                                                                                                                                | 800                      |                                               |                          | mV                   |

| F06     | fclk()      | Permissible Clock Frequency:<br>SSI protocol             | MODE_ST = 0x05 to 0x0B, 0x0D to 0x0F                                                                                                                                                        |                          |                                               | 4                        | MHz                  |

| F07     | fclk()      | Permissible Clock Frequency:<br>BiSS protocol            | NBISS = 0                                                                                                                                                                                   |                          |                                               | 10                       | MHz                  |

| F08     | tp(MA-SLO)  | Propagation Delay:<br>MA edge vs. SLO output             | RL(SLO/NSLO) = $120 \Omega$                                                                                                                                                                 | 10                       |                                               | 50                       | ns                   |

| F09     | tbusy_s     | Processing Time Singlecycle<br>Data (delay of start bit) | Nonius modes:  MODE_ST = 0x00 to 0x02  MODE_ST = 0x03 to 0x04, 2 track  MODE_ST = 0x03 to 0x04, 3 track  MODE_ST = 0x05 to 0x0B  MT modes:  MODE_ST = 0x0C, 3 track  MODE_ST = 0x0D to 0x0F |                          | tcnv *1<br>tcnv *2<br>tcnv *3<br>0<br>tcnv *3 |                          | hs<br>hs<br>hs<br>hs |

| F10     | tbusy_r     | Processing Time Register Access (delay of start bit)     | _                                                                                                                                                                                           |                          |                                               | 2                        | ms                   |

|         | tidle       | Interface Blocking Time                                  | powering up without EEPROM                                                                                                                                                                  | -                        |                                               | 2                        | ms                   |

Rev F2, Page 13/62

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = VACO =  $5 \text{ V} \pm 10 \text{ %}$ , Tj = -40...125 °C, IBP calibrated to  $200 \,\mu\text{A}$ , reference point GNDA (GND for digital I/O pins), unless otherwise stated

| ltem<br>No. | Symbol                          | Parameter                          | Conditions                                                | Min. | Тур. | Max. | Unit |

|-------------|---------------------------------|------------------------------------|-----------------------------------------------------------|------|------|------|------|

| I/O Int     | erface: Clo                     | ock Line Output MAO                |                                                           |      |      |      |      |

| G01         | Vs()hi                          | Saturation Voltage hi              | Vs()hi = VDD - V(), I() = -4 mA                           |      |      | 450  | mV   |

| G02         | Vs()lo                          | Saturation Voltage lo              | I() = 4 mA                                                |      |      | 450  | mV   |

| G03         | lsc()hi                         | Short-circuit Current hi           |                                                           | -85  |      | -30  | mA   |

| G04         | lsc()lo                         | Short-circuit Current lo           |                                                           | 20   |      | 65   | mA   |

| Test S      | ignal Inpu                      | ts: T2, T3                         |                                                           |      |      |      | ,    |

| H01         | Vt()hi                          | Input Threshold Voltage hi         |                                                           |      |      | 2    | V    |

| H02         | Vt()lo                          | Input Threshold Voltage lo         |                                                           | 800  |      |      | mV   |

| H03         | Vt()hys                         | Input Hysteresis                   |                                                           | 150  | 250  |      | mV   |

| H04         | lpd()                           | Input-Pull-Down-Current at T2      | V() = 1 VVDD                                              | 4    | 30   | 75   | μA   |

| H05         | Vpd()                           | Input-Pull-Down-Voltage at T2      | I() = 5 μA                                                |      |      | 650  | mV   |

| H06         | lpu()                           | Input Pull-up Current at T3        | V() = 0VDD - 1 V                                          | -65  | -30  | -5   | μA   |

| H07         | Vpu()                           | Input Pull-up Voltage at T3        | $Vpu() = VDD - V(), I() = -5 \mu A$                       |      |      | 650  | mV   |

| Test S      | ignal Outp                      | uts: T0, T1                        |                                                           |      |      |      |      |

| 101         | Vs()hi                          | Saturation Voltage hi              | Vs()hi = VDD - V(), I() = -4 mA                           |      |      | 500  | mV   |

| 102         | Vs()lo                          | Saturation Voltage lo              | I() = 4 mA                                                |      |      | 600  | mV   |

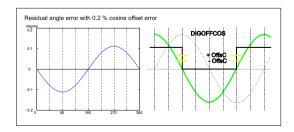

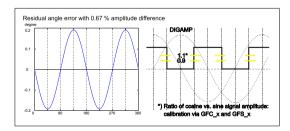

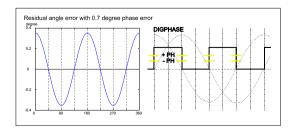

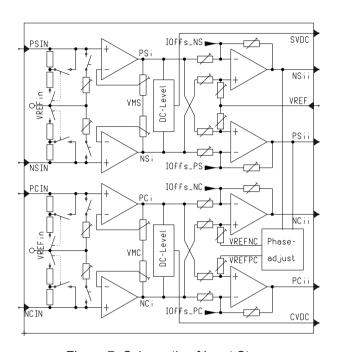

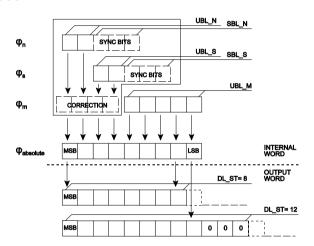

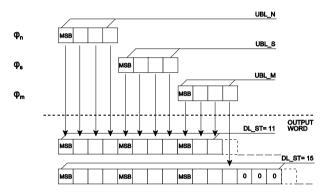

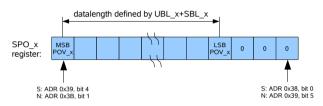

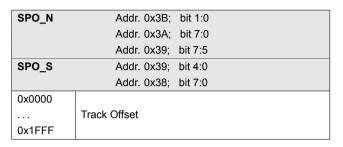

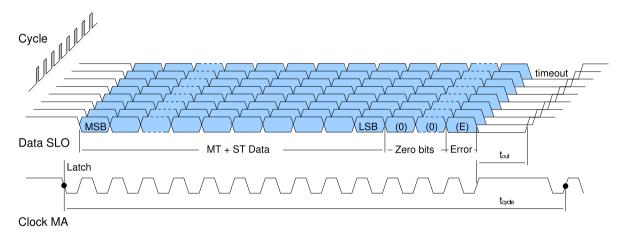

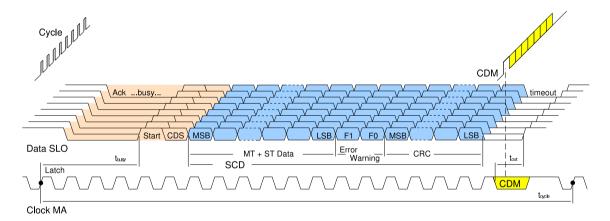

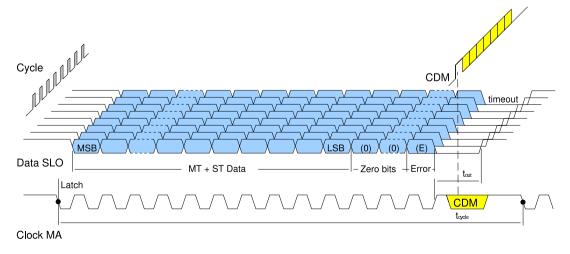

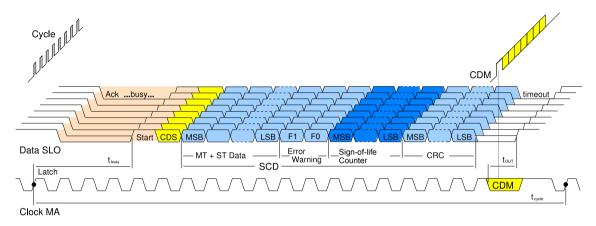

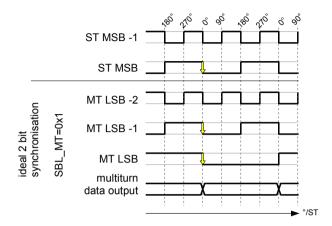

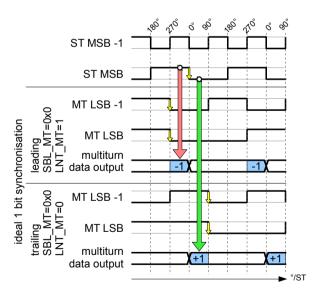

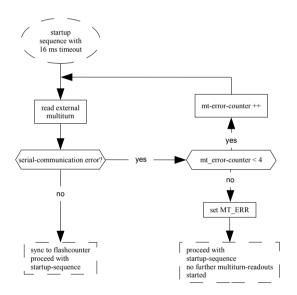

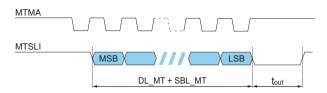

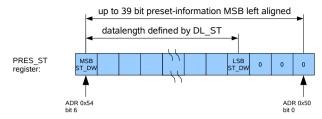

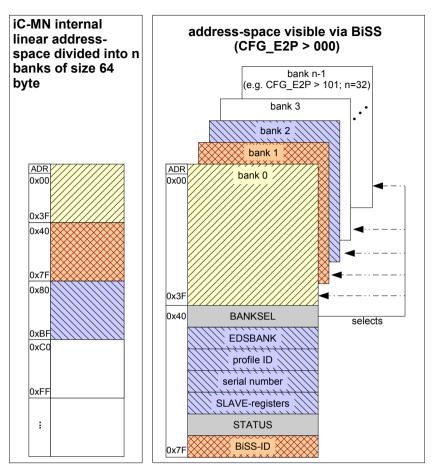

| 103         | Isc()hi                         | Short-circuit Current hi           |                                                           | -60  |      | -15  | mA   |