## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 1/19

#### **FEATURES**

- ♦ Quadruple Hall sensor array for error-tolerant adjustment

- ♦ Non-sensitive to magnetic stray fields due to differential measurement technique

- ♦ Interpolator with a resolution of up to 256 angle steps per cycle

- ♦ Rotational speeds up to 60 000 rpm

- ♦ 4 buffered I/O stages for signal outputs

- ♦ Three configuration inputs for operating mode selection

- ♦ Analog operation modes:

- sine/cosine signals controlled to 2 Vpp

- triangle or sawtooth signal with selectable amplitude

- ♦ Digital operation modes:

- A/B quadrature signals with Z index pulse

- Counter pulses for external binary counters

- ♦ Cascading of multiple iC-MA possible for chain operation

- ♦ Error signal output for detection of low magnetic field strength

- ♦ Additional operating modes with reduced power consumption

- ♦ Standby mode when not enabled

- ♦ Extended temperature range of -40...+125 °C

#### **APPLICATIONS**

- ♦ Analog and digital angle sensors

- Incremental angular encoders

- ♦ Magnetic multiturn encoders

- ♦ Potentiometer replacement

- ♦ Contactless rotary switch

- Commutation of brushless DC motors

- ♦ Flow meter

#### **PACKAGES**

DFN10 4 mm x 4 mm x 0.9 mm RoHS compliant

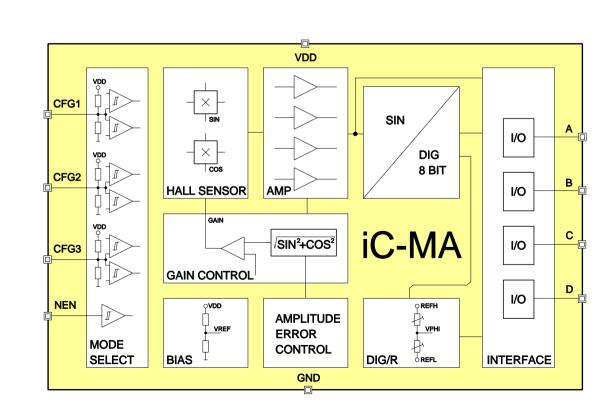

#### **BLOCK DIAGRAM**

### 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 2/19

#### DESCRIPTION

The CMOS device iC-MA consists of a quadruple Hall sensor array which has been optimized for the magnetic measurement of angles of rotation. This array permits error-tolerant adjustment of the magnet, reducing assembly efforts. The integrated signal conditioning unit provides a differential sine/cosine signal at the output. The sensor generates one sine cycle per each full rotation of the magnet, enabling the angle to be clearly determined. At the same time the internal amplitude control unit produces an regulated output amplitude of 2 Vpp regardless of variations in the magnetic field strength, supply voltage and temperature. Furthermore, signals are provided which enable the sensor amplitude to be assessed and also report any magnet loss.

With the aid of the integrated 8-bit sine/digital converter the angle of rotation is determined from the sine/cosine signals. This is output via an incremental interface in a number of selectable resolutions. The

zero angle is indicated by an index pulse. The maximum resolution of 8-bit is maintained up to rotations of 60 000 rpm.

The absolute angle of rotation can be converted back to a linear analog output signal using the internal D/A converter; here, output voltage limits can be set as required using the external pins. Either a periodic linear signal (sawtooth) or a delta voltage (triangle) can be provided. iC-MA can be easily cascaded in three different modes of chain operation so that several axes of rotation can be scanned. The angle positions of the individual axes can then be read via a common bus.

Used in conjunction with a permanent magnet iC-MA can act as an encoder system with an integrated magnetic scanning feature. No further components are required.

#### **CONTENTS**

| PACKAGING INFORMATION                  | 3 | OPERATING MODES                     | 11 |

|----------------------------------------|---|-------------------------------------|----|

| PIN CONFIGURATION<br>DFN10 4 mm x 4 mm |   | ANALOG MODES OF OPERATION           | 12 |

| (according to the JEDEC standard)      | 3 | S-Sensor Mode                       | 12 |

| PACKAGE DIMENSIONS                     | 4 | D-Sensor Mode                       | 12 |

| ABSOLUTE MAXIMUM RATINGS               | 5 | RESISTOR MODES OF OPERATION         | 13 |

|                                        |   | Resistor Modes of Operation         | 13 |

| THERMAL DATA                           | 5 |                                     |    |

|                                        |   | AB-CHAIN, D-CHAIN AND S-CHAIN MODES | 14 |

| ELECTRICAL CHARACTERISTICS             | 6 | AB-Chain Mode                       | 15 |

|                                        |   | D-Chain Mode                        | 15 |

| OPERATING REQUIREMENTS                 | 7 | S-Chain Mode                        | 15 |

| Logic                                  | 8 |                                     |    |

|                                        |   | INCREMENTAL ABZ MODES               | 16 |

| THE SENSOR PRINCIPLE                   | 9 |                                     |    |

|                                        |   | INCREMENTAL CLK MODES               | 17 |

| DEFINITION OF THE ANGLE OF ROTATION    |   | CLK-INC Mode                        | 17 |

| AND THE DIRECTION OF ROTATION          | 9 | DIR-INC Mode                        | 18 |

| PROGRAMMING THE CONFIGURATION          | 9 | REVISION HISTORY                    | 18 |

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 3/19

#### **PACKAGING INFORMATION**

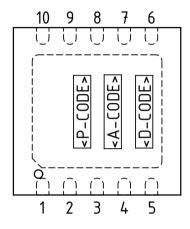

PIN CONFIGURATION

DFN10 4 mm x 4 mm

(according to the JEDEC standard)

# PIN FUNCTIONS No. Name Function

ΒP

| 1  | NEN  | Enable Input, low active     |

|----|------|------------------------------|

| 2  | GND  | Ground                       |

| 3  | CFG2 | Configuration Input 2        |

| 4  | В    | Bidirectional Input/Output B |

| 5  | Α    | Bidirectional Input/Output A |

| 6  | D    | Bidirectional Input/Output D |

| 7  | С    | Bidirectional Input/Output C |

| 8  | CFG3 | Configuration Input 3        |

| 9  | VDD  | +5 V Supply Voltage          |

| 10 | CFG1 | Configuration Input 1        |

Backside paddle 1)

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes), <D-CODE> = date code (subject to changes);

1) Connecting the backside paddle is recommended by a single link to GND. A current flow across the paddle is not permissible.

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 4/19

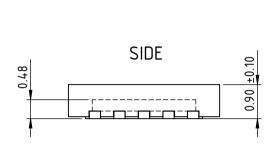

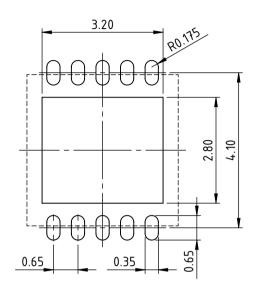

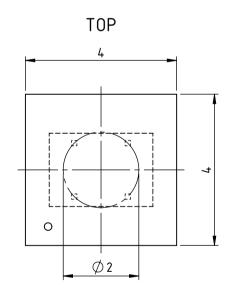

### **PACKAGE DIMENSIONS**

## RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm.

Tolerances of form and position according to JEDEC MO-229.

Tolerance of sensor pattern: ±0.10mm / ±1° (with respect to center of backside pad). dra\_dfn10-4x4-1\_ma\_u\_pack\_1, 10:1

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 5/19

### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol   | Parameter                               | Conditions                        |      |      | Unit |

|------|----------|-----------------------------------------|-----------------------------------|------|------|------|

| No.  |          |                                         |                                   | Min. | Max. |      |

| G001 | VDD      | Supply Voltage                          |                                   | -0.3 | 6    | V    |

| G002 | V()      | Voltages at A, B, C, D, NEN, CFG1, CFG2 | V() < VDD + 0.3 V                 | -0.3 | 6    | V    |

| G003 | Imx(VDD) | Current at VDD                          |                                   | -30  | 30   | mA   |

| G004 | Imx(GND) | Current at GND                          |                                   | -30  | 30   | mA   |

| G005 | lmx()    | Current at A, B, C, D, NEN, CFG1, CFG2  |                                   | -10  | 10   | mA   |

| G006 | llu()    | Pulse Current (Latch-up Immunity)       | pulse width < 10 µs               | -100 | 100  | mA   |

| G007 | Vd()     | ESD-Voltage at all pins                 | HBM 100 pF discharged over 1.5 kΩ |      | 2    | kV   |

| G008 | Ts       | Storage Temperature                     |                                   | -40  | 150  | °C   |

#### THERMAL DATA

Operating conditions: VDD = 5 V ±10 %

| Item | Symbol | Parameter                       | Conditions                                          |      |      |      | Unit |

|------|--------|---------------------------------|-----------------------------------------------------|------|------|------|------|

| No.  |        |                                 |                                                     | Min. | Тур. | Max. |      |

| T01  | Та     | Ambient Temperature             |                                                     | -40  |      | 125  | °C   |

| T02  | Rthja  | Thermal Resistance Chip/Ambient | DFN10 on multi-layer test board acc. JEDEC standard |      |      | 200  | K/W  |

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 6/19

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 5 V  $\pm 10 \%$ , Tj = -40 ... 125 °C, unless otherwise noted

| Item<br>No. | Symbol               | Parameter                                              | Conditions                                                           | Min. | Тур.    | Max.     | Unit     |

|-------------|----------------------|--------------------------------------------------------|----------------------------------------------------------------------|------|---------|----------|----------|

| Gene        | al                   |                                                        |                                                                      |      |         |          |          |

| 001         | VDD                  | Supply Voltage                                         |                                                                      | 4.5  | 5       | 5.5      | V        |

| 002         | I(VDD)               | Supply Current                                         | open pins, normal operation open pins, power reduction mode (PRM)    |      | 14<br>7 | 21<br>14 | mA<br>mA |

| 003         | I(VDD)sb             | Standby Supply Current                                 | NEN = VDD                                                            |      |         | 200      | μA       |

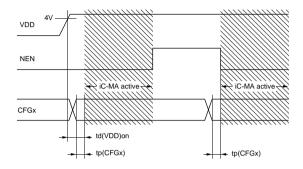

| 004         | td(VDD)on            | Turn-on Delay                                          | VDD > 4 V, see Figure 5                                              |      | 10      |          | μs       |

| 005         | td(VDD)off           | Turn-off Delay                                         | VDD < 2.6 V                                                          |      | 10      |          | μs       |

| Hall S      | ensor Array          | ·                                                      |                                                                      |      |         |          |          |

| 101         | Hext                 | Required External Magnetic Field Strength              | at chip surface                                                      | 20   | 50      | 100      | kA/m     |

| 102         | dsens                | Diameter of Hall Sensor Array                          |                                                                      |      | 2       |          | mm       |

| 103         | xdis                 | Displacement of Hall Sensor<br>Array to Package        | Package DFN10                                                        | -0.2 |         | 0.2      | mm       |

| 104         | <b></b> <i>Φ</i> dis | Angular Displacement of Chip with Reference to Package | Package DFN10                                                        | -3   |         | 3        | DEG      |

| 105         | hsens                | Distance Chip Surface to Top of Package                | Package DFN10                                                        |      | 400     |          | μm       |

| 106         | Aabs                 | Absolute Angular Position                              | using magnet with 4 mm diameter, centered to chip, Hext = 20100 kA/m | -3   |         | 3        | DEG      |

| Signa       | l Conditioni         | ng                                                     |                                                                      |      |         |          | .11      |

| 201         | Voff                 | Offset Voltage                                         | on output, with external magnetic field amplitude of 20 kA/m         | -50  |         | 50       | mV       |

| 202         | TC(Voff)             | Temperature Coefficient of Offset Voltage              |                                                                      | -50  |         | 50       | μV/K     |

| 203         | Vdc                  | Output Mean Value                                      |                                                                      | 45   | 50      | 55       | %VDD     |

| 204         | Ratio                | Amplitude Ratio of SIN / COS                           |                                                                      | 0.95 | 1.00    | 1.05     |          |

| 205         | fhc                  | Cut-off Frequency                                      |                                                                      |      | 20      |          | kHz      |

| 206         | t()settle            | Settling Time                                          | to 70 % amplitude, Hext = 40 kA/m                                    |      | 80      | 150      | μs       |

| 207         | V()gain              | Gain Output Voltage                                    |                                                                      | 0.05 |         | 4.0      | V        |

| 208         | V()ampl              | Sine/Cosine Amplitude                                  | V()ampl = V()max - Vdc                                               | 0.9  | 1.0     | 1.1      | V        |

| Sine/[      | Digital Conve        | erter                                                  |                                                                      |      |         |          |          |

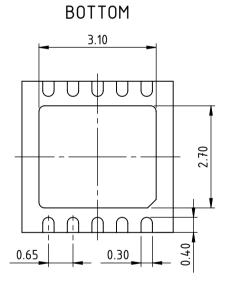

| 301         | AArel                | Relative Angular Error                                 | with reference to one period, see Figure 1                           | -20  |         | 20       | %        |

| 302         | f(OSC)               | Oscillator Frequency                                   |                                                                      | 200  | 256     | 300      | kHz      |

| 303         | TC(OSC)              | Temperature Coefficient of Oscillator Frequency        |                                                                      |      | -0.1    |          | %/K      |

| 304         | hys                  | Converter Hysteresis                                   |                                                                      |      | 1       |          | LSB      |

| Confi       | guration Inp         | uts CFG1, CFG2, CFG3                                   |                                                                      |      |         |          |          |

| 401         | Vt()hi               | Threshold Voltage high                                 |                                                                      | 60   |         | 78       | % VDD    |

| 402         | Vt()lo               | Threshold Voltage low                                  |                                                                      | 25   |         | 40       | % VDD    |

| 403         | V0()                 | Open Circuit Voltage                                   |                                                                      | 43   |         | 57       | % VDD    |

| 404         | Ri()                 | Input Resistance                                       |                                                                      | 45   | 150     | 750      | kΩ       |

| Enabl       | e Input NEN          |                                                        |                                                                      |      |         |          |          |

| 501         | Vt()hi               | Threshold Voltage high                                 |                                                                      |      |         | 2        | V        |

| 502         | Vt()lo               | Threshold Voltage low                                  |                                                                      | 0.8  |         |          | V        |

| 503         | Vt()hys              | Hysteresis                                             | Vt()hys = Vt()hi - Vt()lo                                            | 100  |         | 300      | mV       |

| 504         | lpu()                | Pull-up Current                                        | V() = 0VDD - 1 V                                                     | -240 | -120    | -25      | μA       |

| Digita      | l Outputs: A         | A, B, C, D                                             |                                                                      |      |         |          |          |

| 601         | Vs()hi               | Saturation Voltage high                                | Vs()hi = VDD - V(), I() = -4 mA                                      |      |         | 0.4      | V        |

| 602         | Vs()lo               | Saturation Voltage low                                 | I() = 4 mA                                                           |      |         | 0.4      | V        |

| 603         | tr()                 | Rise Time                                              | CL() = 50 pF                                                         |      |         | 60       | ns       |

| 604         | tf()                 | Fall Time                                              | CL() = 50 pF                                                         |      |         | 60       | ns       |

| 605         | llk()                | Leakage Current                                        | NEN = high, V() = 0 VDD                                              | -5   |         | 5        | μA       |

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 7/19

## **ELECTRICAL CHARACTERISTICS**

Operating conditions: VDD = 5 V  $\pm 10 \%$ , Tj = -40 ... 125 °C, unless otherwise noted

| Item   | Symbol     | Parameter                      | Conditions                                 | 1    |      |      | Unit |

|--------|------------|--------------------------------|--------------------------------------------|------|------|------|------|

| No.    |            |                                |                                            | Min. | Тур. | Max. |      |

| 606    | Vc()hi     | Clamp-Voltage high             | Vc()hi = V() - VDD, NEN = high, I() = 4 mA | 0.3  |      | 1.6  | V    |

| 607    | Vc()lo     | Clamp-Voltage low              | NEN = high, I() = -4 mA                    | -1.5 |      | -0.3 | V    |

| Digita | Inputs: A, | B, C, D                        |                                            |      |      |      |      |

| 701    | Vt()hi     | Threshold Voltage high         |                                            |      |      | 2    | V    |

| 702    | Vt()lo     | Threshold Voltage low          |                                            | 0.8  |      |      | V    |

| 703    | Vt()hys    | Hysteresis                     | Vt()hys = Vt()hi - Vt()lo                  | 300  |      |      | mV   |

| 704    | lpd()      | Pull-down Current              | V() = 1 VVDD                               | 5    | 30   | 65   | μΑ   |

| Analo  | g Outputs: | A, B, C, D                     |                                            |      |      |      |      |

| 801    | SR         | Slew Rate                      |                                            | 2    |      |      | V/µs |

| 802    | fhc()      | Cut-off Frequency              |                                            | 500  |      |      | kHz  |

| 803    | I()        | Output Current                 |                                            | -1   |      | 1    | mA   |

| 804    | R()eda     | Input Resistance DA-Converter  | between pin B and pin C                    | 6    | 8    | 10   | kΩ   |

| 805    | R()ada     | Output Resistance DA-Converter | at pin A                                   |      | 100  |      | kΩ   |

Figure 1: Definition of relative angular error

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 8/19

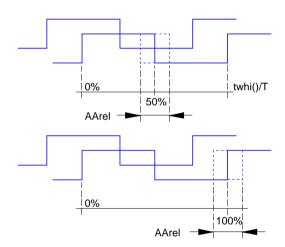

## **OPERATING REQUIREMENTS: Logic**

Operating conditions: VDD = 5 V  $\pm$ 10 %, Tj = -40...125 °C, unless otherwise noted Input level low = 0...0.45 V, high = 2.4 V...VDD, timing according Figure 2

| ltem  | Symbol   | Parameter                  | Conditions                      |      |    | Unit |

|-------|----------|----------------------------|---------------------------------|------|----|------|

| No.   |          |                            | Min.                            | Max. |    |      |

| Logic |          |                            |                                 |      |    |      |

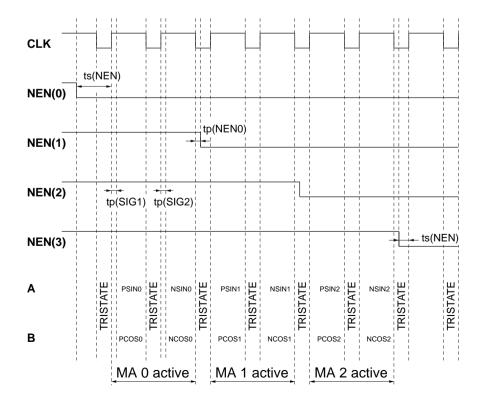

| 1001  | ts(NEN)  | Setup Time NEN             | CLK: low → high (see Figure 11) | 30   |    | ns   |

| 1002  | tp(NEN)  | Delay Time NENO            | CLK: high → low (see Figure 11) |      | 30 | ns   |

| 1003  | tp(SIG1) | Delay Time SIG1            | CL() = 50 pF (see Figure 11)    |      | 60 | μs   |

| 1004  | tp(SIG2) | Delay Time SIG2            | CL() = 50 pF (see Figure 11)    |      | 2  | μs   |

| 1005  | tp(CFGx) | Setup Time at CFGx, x = 13 | see Figure 5                    |      | 10 | μs   |

Figure 2: Reference levels for delays

Rev C1, Page 9/19

#### THE SENSOR PRINCIPLE

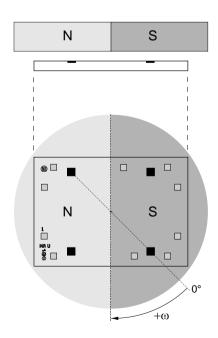

Figure 3: The principle of magnetic field measurement using a Hall sensor

In conjunction with a permanent magnet iC-MA can be used to create a complete encoder system. A cylindri-

cal, diametrically magnetized permanent magnet (with a diameter D of 4 mm and length L of 4 mm, for example) provides optimal sensor signals. Magnetic materials such as neodymium iron boron (NdFeB) or samarium cobalt (SmCo) are very well suited to the sensor and not readily influenced by external magnetic disturbance fields. The L/D ratio of a magnet magnetized to saturation point has a bearing on the resulting field strength and should lie within the region of 0.3 to 2.

iC-MA has four Hall sensors which are used to determine angles and to convert the magnetic field into a measurable Hall voltage. Only the z component of the magnetic field is assessed where the line of magnetic flux must pass through two facing Hall sensors in the opposite direction. An example line of magnetic flux is given in Figure 4. The Hall sensors have been arranged in such a way that the assembly of the magnet with iC-MA is extremely tolerant. Two Hall sensors combined generate a differential Hall signal. If the magnet is rotated along its longitudinal axis sine and cosine output voltages are created which can be used to determine angles.

### **DEFINITION OF THE ANGLE OF ROTATION AND THE DIRECTION OF ROTATION**

The arrangement of permanent magnet and iC-MA illustrated in Figure 4, where the diametrically magnetized magnet is placed vertical to the chip's surface, is used to determine both the angle  $\omega$  and direction of rotation. An angle of 0° lies along the diagonal. Rotating the magnet clockwise as shown in Figure 4 increases the angular position and hence the output signal.

Figure 4: Definition of the angle and direction of rotation

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 10/19

#### PROGRAMMING THE CONFIGURATION

iC-MA has 28 modes of operation (see tables on the following pages). After the device has been switched on or *woken up* from standby mode by a low signal at pin NEN the levels at the configuration inputs CFG1 to CFG3 are assessed. These three-level inputs can be connected to GND = low level, left open = open or connected to VDD = high level. For correct identification, a setup time of at least  $tp(CFGx) = 4 \mu s$  must be maintained between programming the configuration and activating the device. While the device is active changes in signal at the configuration inputs are ignored.

If several iC-MAs are connected in series in chain operation (see the description of functions on page 14) it must be ensured that the NEN input of the devices level is switched to low during the various clock cycles and that the programming default does thus not lie within the active phase of the devices.

In standby all ports are switched to tristate, i.e. high impedance. Only in chain operation modes port D level is active high so that the devices arranged further behind can also be deactivated.

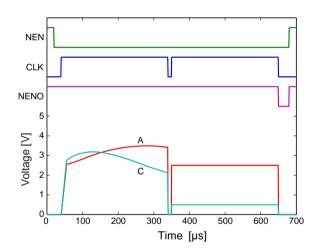

Figure 5: Programming the configuration

## 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 11/19

## **OPERATING MODES**

| Mode         | NEN    | CFG1   | CFG2 | CFG3 | Port A    | Port B | Port C    | Port D           | Res. | Comments      |

|--------------|--------|--------|------|------|-----------|--------|-----------|------------------|------|---------------|

| Analog       |        |        |      |      |           |        |           |                  |      |               |

| S-Sensor     | low    | low    | low  | low  | PSIN      | VREF   | PCOS      | GAIN             |      |               |

| D-Sensor     | low    | open   | low  | low  | PSIN      | NSIN   | PCOS      | NCOS             |      | PRM           |

| D-Sensor     | low    | high   | low  | low  | PSIN      | NSIN   | PCOS      | NCOS             |      |               |

| Linear Out   | tput   |        |      |      |           |        |           |                  |      |               |

| R-Sensor     | low    | low    | open | low  | VTRI      | REFH   | MSB       | NERR             | 8    |               |

|              | low    | open   | open | low  | VTRI      | REFH   | MSB       | GAIN             | 8    |               |

|              | low    | high   | open | low  | VSAW      | REFH   | REFL      | NERR             | 8    |               |

|              | low    | high   | open | high | VSAW      | REFH   | REFL      | GAIN             | 8    |               |

| Chain Mod    | de     |        |      |      |           |        |           |                  |      |               |

| AB-Chain     | low    | low    | high | low  | Α         | CLK    | В         | NENO             | 8    |               |

| D-Chain      | low    | open   | high | low  | PSIN/NSIN | CLK    | PCOS/NCOS | NENO             |      |               |

| S-Chain      | low    | high   | high | low  | PSIN/VREF | CLK    | PCOS/GAIN | NENO             |      |               |

| Incr. ABZ    |        |        |      |      |           |        |           |                  |      |               |

| ABZ 8-1      | low    | low    | low  | open | Α         | В      | Z         | NERR             | 8    | AB = 1        |

| ABZ 8-0      | low    | open   | low  | open | Α         | В      | Z         | NERR             | 8    | AB = 0        |

| ABZ 7-1      | low    | low    | open | open | А         | В      | Z         | NERR             | 7    | AB = 1        |

| ABZ 7-0      | low    | open   | open | open | Α         | В      | Z         | NERR             | 7    | AB = 0        |

| ABZ 6-1      | low    | low    | high | open | Α         | В      | Z         | NERR             | 6    | AB = 1        |

| ABZ 6-0      | low    | open   | high | open | Α         | В      | Z         | NERR             | 6    | AB = 0        |

| ABZ 8-1      | low    | low    | low  | high | Α         | В      | Z         | NERR             | 8    | AB = 1, PRM   |

| ABZ 8-0      | low    | open   | low  | high | Α         | В      | Z         | NERR             | 8    | AB = 0, $PRM$ |

| ABZ 7-1      | low    | low    | open | high | Α         | В      | Z         | NERR             | 7    | AB = 1, PRM   |

| ABZ 7-0      | low    | open   | open | high | Α         | В      | Z         | NERR             | 7    | AB = 0, $PRM$ |

| ABZ 6-1      | low    | low    | high | high | Α         | В      | Z         | NERR             | 6    | AB = 1, PRM   |

| ABZ 6-0      | low    | open   | high | high | Α         | В      | Z         | NERR             | 6    | AB = 0, $PRM$ |

| Incr. CLK    |        |        |      |      |           |        |           |                  |      |               |

| CLK 8        | low    | high   | low  | open | NCLKUP    | NCLKDN | NCLR      | NERR             | 8    |               |

| CLK 6        | low    | high   | high | open | NCLKUP    | NCLKDN | NCLR      | NERR             | 6    |               |

| DIR 8        | low    | high   | low  | high | NCLK      | DIR    | NCLR      | NERR             | 8    |               |

| DIR 6        | low    | high   | high | high | NCLK      | DIR    | NCLR      | NERR             | 6    |               |

| Test (for iC | C-Haus | use or | nly) |      |           |        |           |                  |      |               |

| Test         | low    | high   | open | open |           |        |           |                  |      | Test          |

| Standby      |        |        |      |      |           |        |           |                  |      |               |

|              | high   | Х      | Х    | Х    | TRI       | TRI    | TRI       | TRI <sup>1</sup> |      |               |

<sup>&</sup>lt;sup>1</sup> In chain operation port D level is active high so that the backend devices can also be deactivated.

### 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 12/19

#### **ANALOG MODES OF OPERATION**

| Mode     | NEN | CFG1 | CFG2 | CFG3 | Port A | Port B | Port C | Port D | Res. C | Comment |

|----------|-----|------|------|------|--------|--------|--------|--------|--------|---------|

| Analog   |     |      |      |      |        |        |        |        |        |         |

| S-Sensor | low | low  | low  | low  | PSIN   | VREF   | PCOS   | GAIN   |        |         |

| D-Sensor | low | open | low  | low  | PSIN   | NSIN   | PCOS   | NCOS   | F      | PRM     |

| D-Sensor | low | high | low  | low  | PSIN   | NSIN   | PCOS   | NCOS   |        |         |

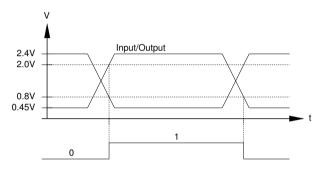

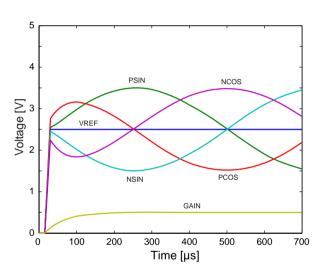

In the analog modes of operation the amplified Hall voltages are available at the output ports. The sine/cosine output signals are controlled to have stable amplitudes of 1 V and referenced to a DC value equivalent to half of the supply voltage (VREF). Due to the internal signal conditioning unit, no special adjustment is required. An externally connected interpolator can be used if further trimming of the output signals is desired.

Figure 6: Analog mode output signals after switching on the device

#### S-Sensor Mode

After the device has been activated via NEN = low the sensor is set to its operating point. All signals are referenced to half the supply voltage (VREF). In S-Sensor mode this potential is available at port B. Ports A and C output the sine and cosine Hall voltages set to 2 Vss. The angle can be calculated from the relation of the sine voltage (difference in voltage PSIN to VREF) to the cosine voltage (difference in voltage PCOS to VREF). The device supplies an angle which remains non-ambiguous over a 360° rotation of the permanent magnet.

Signal GAIN allows conclusions to be drawn as to the operating point of the sensor. This is influenced by the amplitude of the magnetic field, the sensor supply voltage and temperature. The higher the GAIN potential, the greater the necessary amplification of the Hall voltages; the external magnetic field is smaller. Besides recording the direction of magnetization of the permanent magnet the distance between the magnet and sensor may also be assessed using the GAIN signal. If the gain is insufficient to boost the Hall voltages to 2 Vss the amplitude control reaches its upper limit and the output amplitude becomes smaller.

The GAIN signal can be used to adjust the permanent magnet. If the central point of both the magnet and sensor iC-MA are the same the GAIN signal has no harmonics. A misaligned sensor must readjust the operating point depending on the angle; the GAIN signal varies in amplitude. To adjust the sensor to the magnet this must be shifted along its X- and Y-axis so that the GAIN signal has to readjust as little as possible.

#### **D-Sensor Mode**

In D-Sensor mode differential sine (pin A and pin B) and cosine (pin C and pin D) signals are supplied at the output; as opposed to S-Sensor mode inverted Hall signals are now also available at the ports. The advantage of this mode of operation is the doubled signal amplitude of the differential Hall voltages and the lack of dependence on reference voltage VREF. The angle is now calculated via the ratio of the difference between PSIN and NSIN and between PCOS and NCOS.

D-Sensor mode is also available with a reduced power consumption (PRM or Power Reduced Mode). In this mode the Hall sensor is supplied with current less frequently, reducing the power consumption. Here it must be observed that the maximum rotating frequency also drops by a factor of 2.

Rev C1, Page 13/19

### **RESISTOR MODES OF OPERATION**

| Mode          | NEN | CFG1 | CFG2 | CFG3 | Port A | Port B | Port C | Port D | Res. | Comments |  |  |

|---------------|-----|------|------|------|--------|--------|--------|--------|------|----------|--|--|

| Linear Output |     |      |      |      |        |        |        |        |      |          |  |  |

| R-Sensor      | low | low  | open | low  | VTRI   | REFH   | MSB    | NERR   | 8    |          |  |  |

|               | low | open | open | low  | VTRI   | REFH   | MSB    | GAIN   | 8    |          |  |  |

|               | low | high | open | low  | VSAW   | REFH   | REFL   | NERR   | 8    |          |  |  |

|               | low | high | open | high | VSAW   | REFH   | REFL   | GAIN   | 8    |          |  |  |

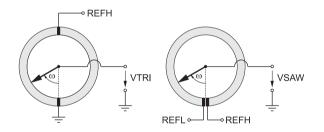

#### **Resistor Modes of Operation**

In R-Sensor mode the taps of an integrated resistive divider are selected depending on the angular position (potentiometer replacement). The value of the absolute angular position acts as a *wiper* and selects one of the 256 taps on the resistor chain.

Figure 7: Potentiometer equivalents for resistor mode operations

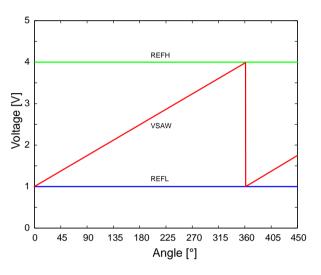

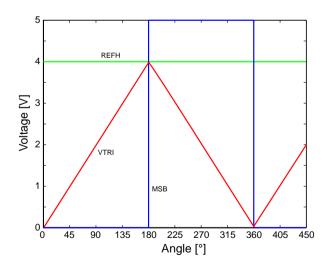

In modes with a sawtooth voltage VSAW at port A the angle is converted into a linear voltage which lies within thresholds REFH and REFL at ports B and C (see Figure 8). The integrated resistor chain is directly available at the ports so that thresholds REFH and REFL can also be reversed. Depending on the selected mode either a GAIN signal or a NERR error signal are present at port D to monitor the amplitude. If the amplitude is at least 70 %, NERR level is high; should the amplitude sink to below 50 % of the set amplitude, NERR switches to active low.

Modes of operation with a triangular voltage VTRI avoids the discontinuity at the zero angular position. Signal MSB can be used to differentiate between the first and second half rotation. The delta voltage is limited by thresholds REFH and GND. As in VSAW mode both GAIN and NERR signals are available.

Figure 8: R-Sensor mode with sawtooth output voltage VSAW

Figure 9: R-Sensor mode with triangular output voltage VTRI

Rev C1, Page 14/19

#### **AB-CHAIN, D-CHAIN AND S-CHAIN MODES**

| Mode      | NEN     | CFG1 | CFG2 | CFG3 | Port A    | Port B | Port C    | Port D | Res. | Comments |

|-----------|---------|------|------|------|-----------|--------|-----------|--------|------|----------|

| Chain Ope | eration |      |      |      |           |        |           |        |      |          |

| AB-Chain  | low     | low  | high | low  | Α         | CLK    | В         | NENO   | 8    |          |

| D-Chain   | low     | open | high | low  | PSIN/NSIN | CLK    | PCOS/NCOS | NENO   |      |          |

| S-Chain   | low     | high | high | low  | PSIN/VREF | CLK    | PCOS/GAIN | NENO   |      |          |

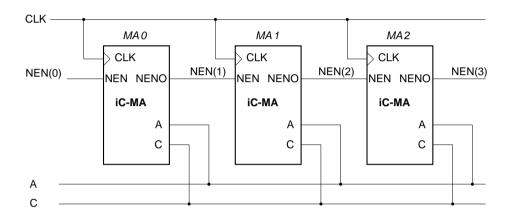

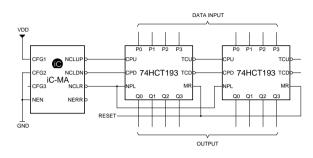

Figure 10: Chain modes for iC-MA

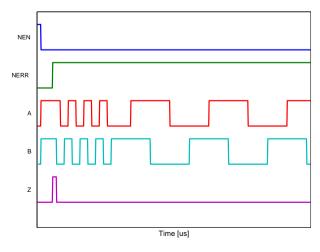

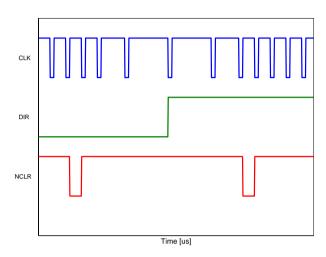

Figure 11: Signal patterns in D-Chain mode

### 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 15/19

In the various chain modes multiple iC-MAs can be arranged in a chain (see Figure 10) where all of the devices are connected by a shared CLK line (pin B). The NEN input is evaluated synchronously with the rising CLK edge. If the NEN input level is switched to low, the device is active during the following CLK cycle(s). To allow the devices to be cascaded a delayed enable signal is generated at output pin NENO (pin D) with which the follow-on device can be activated. If the NEN input of the first device in the chain is reset to high, all devices in the chain are deactivated. Bus lines A (pin A) and C (pin C) are activated by tristate output stages which are high impedance when NEN is high and CLK is low and also following the second rising CLK edge.

#### **AB-Chain Mode**

In AB-Chain mode two A/B digital incremental signals are generated at ports A and C. The two square-wave signals are phase shifted at either +90° or -90°, depending on the direction of rotation. Following a CLK pulse the next device in the chain is enabled. Here the falling CLK edge deactivates the current device (e.g. MA 1 in Figure 10) and activates the next device in the chain (MA 2) with a low signal at its NEN input. After a device has been activated the two bus lines A (port A) and B (port C) are first switched to low (see Figure 11). This is then followed by the incremental signals being output, starting at the zero position. In the event of error the bus lines remain low.

## **D-Chain Mode**

In D-Chain mode differential sine and cosine signals are generated at ports A and C. During the first clock pulse signals PSIN and PCOS are presented to the bus; during the second pulse signals NSIN and NCOS are on the bus (see Figure 11). In this mode each device is thus active for two clock pulses. During the first clock pulse the non-inverted sine (port A) and cosine (port C) signals are first presented to the bus, with the inverted signals following on the positive CLK edge during the second pulse. The falling CLK edge in the second clock pulse deactivates the current device and

activates the following device in the chain with a low signal at its NEN input.

#### S-Chain Mode

In S-Chain mode the non-inverted sine (port A) and cosine (port C) signals are presented to the bus during the first clock pulse, with the mean of the two signals (VREF, port A) and the amplification signal GAIN (port C) following on the positive CLK edge of the next pulse. Each device is thus active for two clock pulses. The falling CLK edge in the second clock pulse deactivates the current device and activates the following device in the chain with a low signal at its NEN input.

The sine and cosine signals can be assessed using signal VREF. Signal GAIN (pin D) indicates iC-MA's internal amplification (see Electrical Characteristics No. 207) and can be used to estimate the signal amplitude of the internal Hall sensor. The GAIN signal can also be used to adjust the rotary axis of the magnet to the center of the chip.

Figure 12: Bus signals and control signals in S-Chain mode

Rev C1, Page 16/19

#### **INCREMENTAL ABZ MODES**

| Mode      | NEN      | CFG1 | CFG2 | CFG3 | Port A | Port B | Port C | Port D | Res. | Comments  |

|-----------|----------|------|------|------|--------|--------|--------|--------|------|-----------|

| Incr. ABZ | <u> </u> |      |      |      |        |        |        |        |      |           |

| ABZ 8-1   | low      | low  | low  | open | Α      | В      | Z      | NERR   | 8    | AB=1      |

| ABZ 8-0   | low      | open | low  | open | Α      | В      | Z      | NERR   | 8    | AB=0      |

| ABZ 7-1   | low      | low  | open | open | Α      | В      | Z      | NERR   | 7    | AB=1      |

| ABZ 7-0   | low      | open | open | open | Α      | В      | Z      | NERR   | 7    | AB=0      |

| ABZ 6-1   | low      | low  | high | open | Α      | В      | Z      | NERR   | 6    | AB=1      |

| ABZ 6-0   | low      | open | high | open | Α      | В      | Z      | NERR   | 6    | AB=0      |

| ABZ 8-1   | low      | low  | low  | high | Α      | В      | Z      | NERR   | 8    | AB=1, PRM |

| ABZ 8-0   | low      | open | low  | high | Α      | В      | Z      | NERR   | 8    | AB=0, PRM |

| ABZ 7-1   | low      | low  | open | high | Α      | В      | Z      | NERR   | 7    | AB=1, PRM |

| ABZ 7-0   | low      | open | open | high | Α      | В      | Z      | NERR   | 7    | AB=0, PRM |

| ABZ 6-1   | low      | low  | high | high | Α      | В      | Z      | NERR   | 6    | AB=1, PRM |

| ABZ 6-0   | low      | open | high | high | Α      | В      | Z      | NERR   | 6    | AB=0, PRM |

iC-MA has an 8-bit sine/digital converter which can convert the sine/cosine sensor signals into a digitized angle. This angle is made available at the ports as an incremental value. Signal Z is always high when the angle is 0°; otherwise the signal is low. In all incremental modes of operation error signal NERR is available so that the plausibility of the counter value can be verified. At an amplitude which is less than 50% of the set amplitude the error signal level switches to low; at an amplitude greater than 70% the error signal is reset, i.e. set to high.

Three different quantities regarding the number of edges per rotation of the magnet can be selected. These are a resolution of 6 bits (64 edges per rotation), 7 bits (128 edges) or 8 bits (256 edges). The conversion process is count-safe, i. e. the output of all edges up to the current angle position is guaranteed as long as the input frequency is less than the maximum possible rotation.

All incremental resolutions also have a reduced power consumption mode (PRM). In this mode the Hall sensor is supplied with current intermittently, reducing the power consumption. Here it must be noted that the maximum input frequency drops by a factor of 2.

A distinction can be made between the various modes of operation by studying the level of the AB signals on the Z pulse. In mode AB = 1 signals A and B are both high, as is Z at an angle of 0°. In mode AB = 0, however, both signals A and B are low when the Z signal is high.

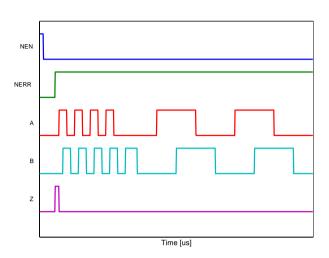

Firstly, the behavior of the sensor on switching on the device is described when the permanent magnet rotates in the direction of the increasing angle  $\omega$  (Fig-

ure 13). After switching on the sensor via NEN at low level the sensor looks for its operating point. If 70% of the set amplitude is achieved the error signal is reset. An error status during this phase is also signaled when signals A and B are high and Z = low. In an errorfree state Z level is always high when the angle is 0°. iC-MA continues to search for its operating point by outputting the angle of the external magnetic field at maximum count frequency via the incremental interface. Once the angle has been obtained the device follows a changed input signal in real time. The edge frequency is thus 256 times the frequency of rotation of the magnet at a set resolution of 8 bits. If a (rising) edge reaches B before a (rising) edge A, this means that the counter value has risen. If the edge reaches A before B. however, this indicates that the absolute value is lower.

Figure 13: Incremental signals after switching on the device, counting up

### 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 17/19

Figure 14: Incremental signals after switching on the device, counting down

Always starting at an angle of 0° the device begins searching for the absolute angle, locating it as quickly

as possible. If this absolute angle is between 0° and 180° the device counts up to the operating point; if the angle is between 180° and 360°, it first counts down. Starting when the device is switched on all edges are output until the absolute position is reached. The setup has to wait until a certain time has elapsed; this is dependent on the selected resolution and is the settling time of the sensor until the error bit is deleted plus the time needed to count up or down to the absolute position. With a resolution of 8 bits and an angle of 180°, for example, this period constitutes 100  $\mu$ s sensor settling time plus 128 times 4  $\mu$ s until the absolute position has been pinpointed. The absolute position is thus available after a maximum of 612  $\mu$ s has elapsed.

By way of example Figure 14 illustrates how the incremental interface behaves when the device first counts down to the absolute position and the magnet then rotates forwards, with the sensor following with the relevant sequence. The Z signal is synchronous with A and B at low level.

#### **INCREMENTAL CLK MODES**

| Mode    | NEN       | CFG1 | CFG2 | CFG3 | Port A | Port B | Port C | Port D | Res. | Comments |

|---------|-----------|------|------|------|--------|--------|--------|--------|------|----------|

| Incr. C | Incr. CLK |      |      |      |        |        |        |        |      |          |

| CLK 8   | low       | high | low  | open | NCLKUP | NCLKDN | NCLR   | NERR   | 8    |          |

| CLK 6   | low       | high | high | open | NCLKUP | NCLKDN | NCLR   | NERR   | 6    |          |

| DIR 8   | low       | high | low  | high | NCLK   | DIR    | NCLR   | NERR   | 8    |          |

| DIR 6   | low       | high | high | high | NCLK   | DIR    | NCLR   | NERR   | 6    |          |

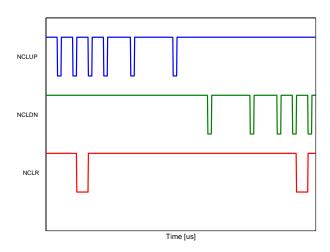

#### **CLK-INC Mode**

In CLK-INC mode two different count signals are provided for the countup and countdown sequences. Depending on the direction of rotation either signal NCLKUP (pin A) is pulsed when the device counts up or signal NCLKDN (pin B) when the device counts down. In each case the remaining signal level is high. The zero angle is displayed by the NCLR index track which can serve as an asynchronous reset for an external counter.

Figure 15 demonstrates how iC-MA behaves in CLK-INC mode, firstly when it counts up from the zero position and then, following a change in the direction of rotation, when it counts back down to an angle of 0°.

This mode permits the operation of external binary counter modules (such as 74HC/HCT193, for example), with signal NCLR (pin C) being used to reset the counter. With a rising edge of clock signal NCLKUP and a high level at NCLKDN the counter status is incremented; with a rising edge of clock signal NCLKDN and a high level at NCLKUP the counter status is

decremented. Two 4-bit counters can be cascaded here to create a full 8-bit counter.

Figure 15: CLK-INC mode

### 8-BIT ANGULAR HALL SENSOR / ENCODER

Rev C1, Page 18/19

Figure 16: iC-MA with binary counter

#### **DIR-INC Mode**

In DIR-INC mode a change in angle for both directions of rotation generates an output pulse for signal CLK (pin A). Signal DIR (pin B) gives the direction of rotation. This mode permits the operation of external binary counter modules (such as 74HC/HCT191, for example), with signal NCLR (pin C) being used to reset the external counter. With a rising edge at CLK the counter status is counted up or down, depending on the value of the DIR signal. A low level at DIR trig-

gers a countup; a high level causes the setup to count down. Figure 17 shows a countup sequence followed by a countdown sequence, both across the zero position.

Figure 17: DIR-INC mode

#### **REVISION HISTORY**

| Rel | Rel.Date | Chapter | Modification    | Page |

|-----|----------|---------|-----------------|------|

| A1  | 05-01-21 | All     | Initial release | All  |

|   | Rel | Rel.Date | Chapter                    | Modification               | Page |

|---|-----|----------|----------------------------|----------------------------|------|

| ĺ | A2  | 06-05-10 | ELECTRICAL CHARACTERISTICS | Items and drawings updated |      |

|   | Rel | Rel.Date | Chapter                    | Modification                               | Page |

|---|-----|----------|----------------------------|--------------------------------------------|------|

| ſ | B1  | 06-07-20 | ELECTRICAL CHARACTERISTICS | Item 404 max.: 750 kΩ, Item 704 min.: 5 μA | 4, 5 |

| Rel | Rel.Date | Chapter               | Modification                 | Page |

|-----|----------|-----------------------|------------------------------|------|

| B2  | 07-07-02 | PACKAGING INFORMATION | Backside paddle complemented | 3    |

|   | Rel | Rel.Date | Chapter                    | Modification                                                                      | Page |

|---|-----|----------|----------------------------|-----------------------------------------------------------------------------------|------|

| ſ | ВЗ  | 09-07-09 | ELECTRICAL CHARACTERISTICS | Item 106 conditions: using magnet with 4mm diameter                               | 5    |

|   |     |          |                            | Item 201 conditions: on output, with external magnetic field amplitude of 20 kA/m |      |

| Rel | Rel.Date | Chapter                    | Modification                | Page    |

|-----|----------|----------------------------|-----------------------------|---------|

| C1  | 14-10-28 |                            | All package Figures updated | 1, 3, 4 |

|     |          | CONTENTS, REVISION HISTORY | Chapter introduced          | 2, 18   |

|     |          | ELECTRICAL CHARACTERISTICS | Item 503 max.: 300 mV       | 6       |

iC-Haus expressly reserves the right to change its products and/or specifications. An info letter gives details as to any amendments and additions made to the relevant current specifications on our internet website <a href="https://www.ichaus.com/infoletter">www.ichaus.com/infoletter</a>; this letter is generated automatically and shall be sent to registered users by email

Copying - even as an excerpt - is only permitted with iC-Haus' approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification and does not assume liability for any errors or omissions in these materials.

The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus products are not designed for and must not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (Safety-Critical Applications) without iC-Haus' specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems. iC-Haus products are not designed nor intended for use in military or aerospace applications or environments or in automotive applications unless specifically designated for such use by iC-Haus.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

Rev C1, Page 19/19

#### **ORDERING INFORMATION**

| Туре                         | Package           | Options | Order Designation |

|------------------------------|-------------------|---------|-------------------|

| iC-MA                        | DFN10 4 mm x 4 mm |         | iC-MA DFN10       |

| iC-MA<br>Evaluation<br>Board |                   |         | iC-MA EVAL MA1D   |

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Tel.: +49 (0) 61 35 - 92 92 - 0

Am Kuemmerling 18 Fax: +49 (0) 61 35 - 92 92 - 192

D-55294 Bodenheim Web: http://www.ichaus.com

GERMANY E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.com/sales\_partners