## Rev D3, Page 1/21

## FEATURES

- Real-time interpolator with a programmable resolution of up to 256 steps/period

- Calibration features permit adaptation of distorted sine/cosine signals

- Output with A/B/Z incremental signals of up to 400kHz, as a parallel 8-bit absolute vector or via a serial interface

- Error messaging with excessive input frequency

- Programmable index position

- Fast 24-bit multiturn counting (position capture with target position interrupt)

- ♦ 8-bit µP interface

- Interrupt controller

- Adjustable clock oscillator

- Front-end amplifiers configurable externally

- Chip setup can be loaded from a serial EEPROM

- TTL-compatible inputs, TTL-/CMOS-compatible outputs

- Inputs and outputs protected against destruction by ESD

# PACKAGES

Absolute and incremental angle

interpolation from orthogonal

Interpolating interface for MR

sensors and optical analog

sinusoidal input signals

**APPLICATIONS**

encoders

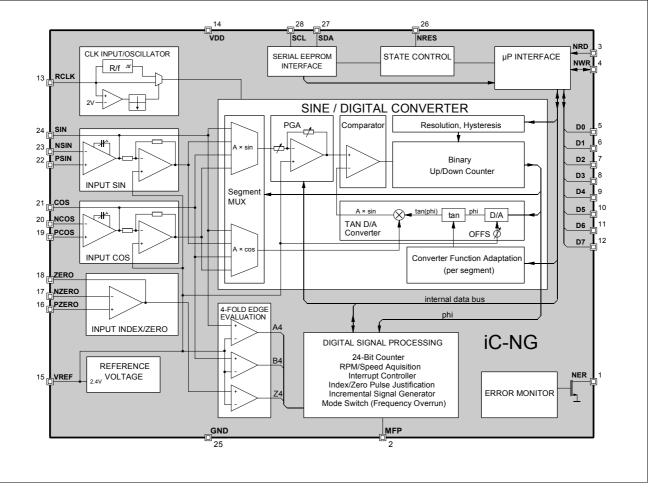

## **BLOCK DIAGRAM**

## DESCRIPTION

iC-NG is a monolithic A/D converter which determines the angle value of two sinusoidal input signals phaseshifted at 90° with a given resolution and hysteresis. In this process a cycle is divided into 8 segments; each of these segments can be given a resolution of up to 32 angular steps. Resolutions of 1 to 256 divisions per cycle are possible.

The converter can be adjusted for each individual segment to suit various types of input signal, meaning that even distorted sine signals or triangular signals, for example, can be converted. In addition, the direction of rotation can be inverted and the zero position can be set in steps of 45°.

Output values and parameters are stored in registers connected to the internal 8-bit data bus. A parallel microcontroller interface gives read and write access to these registers. If an EEPROM is connected to the serial interface, the chip setup can be automatically read in following a reset.

The output value consists of an 8-bit word for interpolation within a cycle and a 24-bit position counter which logs the number of turns. In addition to normal accessibility, the output value can also be transferred serially.

The position counter can be reset via the zero pulse or stopped and started using the bi-directional MFP pin.

When programmed as an output, pin MFP shows the change in output value or indicates when a certain position has been reached (interrupt output). After a reset, the interpolation result is correct after just a few clock cycles, even with static input signals.

If incremental mode is selected, the changes in angle are output as square-wave signals phase-shifted at 90° at pins D0(AX) and D1(BX) with a selected resolution and at pins D3(A4) and D4(B4) with a resolution of four. The suitably prepared zero signal is at D2(ZX) and D5(Z4). Pin D6(ROT) shows the direction of rotation. Tracks AX and BX are EX-OR-gated at pin D7(AXB).

The front-end amplifier connections are all lead out, enabling current or voltage inputs to be made. Complementary input signals can also be connected. The front-end amplifiers are compensated internally; the value of compensation can be programmed.

The internal clock frequency can be adjusted using an external resistor or can be fed in via pin RCLK. The clock pulses which occur between two changes in output are counted in order to calculate the number of revolutions. Low voltage and excessive input frequency errors are signaled at output NER (open drain). These error codes are stored in the relevant register.

## Rev D3, Page 3/21

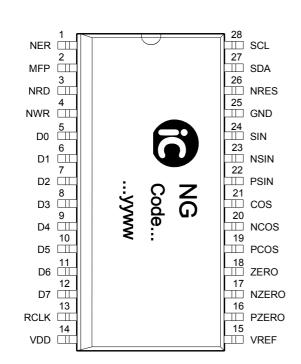

#### PACKAGE SO28, SSOP28 to JEDEC Standard

#### **PIN CONFIGURATION SO28** (top view)

| PIN FUNCT                                                                                                                                                                                                                                                                                                                                                                                                     | PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| No. Name                                                                                                                                                                                                                                                                                                                                                                                                      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| No.     Name       1     NER       2     MFP       3     NRD       4     NWR       5     D0       6     D1       7     D2       8     D3       9     D4       10     D5       11     D6       12     D7       13     RCLK       14     VDD       15     VREF       16     PZERO       17     NZERO       18     ZERO       19     PCOS       20     NCOS       21     COS       22     PSIN       23     NSIN | Function<br>Error Message Output, Iow active<br>Multi-Functional I/O Pin<br>Read Signal, Iow active <sup>1)</sup> / SSI Clock<br>Write Signal, Iow active <sup>1)</sup> / SSI Output<br>Data Bus / Incremental Output A (AX)<br>Data Bus / Incremental Output B (BX)<br>Data Bus / Index Output Z (ZX)<br>Data Bus / Sine-to-Square Output A (A4)<br>Data Bus / Index-to-Square Output B (B4)<br>Data Bus / Index-to-Square Output Z (Z4)<br>Data Bus / CW-CCW Signal (ROT)<br>Data Bus / AX EXOR BX (AXB)<br>Clock Input / Clock Oscillator Setting<br>+5V Supply Voltage<br>Reference Center Voltage<br>Zero Amplifier Positive Input<br>Zero Amplifier Positive Input<br>Cosine Amplifier Positive Input<br>Cosine Amplifier Positive Input<br>Sine Amplifier Positive Input<br>Sine Amplifier Positive Input |  |  |  |  |  |  |  |  |  |

| 24 SIN                                                                                                                                                                                                                                                                                                                                                                                                        | Sine Amplifier Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| 25 GND<br>26 NRES                                                                                                                                                                                                                                                                                                                                                                                             | Ground<br>Reset, low active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 27 SDA                                                                                                                                                                                                                                                                                                                                                                                                        | Mode Select / Data (Serial Interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| 28 SCL                                                                                                                                                                                                                                                                                                                                                                                                        | Mode Select / Clock (Serial Interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

Notes: 1) wiring to VDD recommended when not in use.

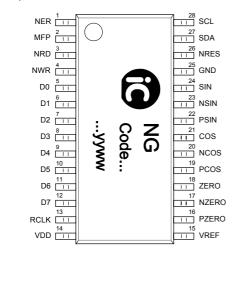

#### **PIN CONFIGURATION SSOP28 5.3mm**

(top view)

Rev D3, Page 4/21

#### **ABSOLUTE MAXIMUM RATINGS**

#### Values beyond which damage may occur; device operation is not guaranteed.

| ltem | Symbol   | Parameter                                                                                                                                          | Conditions                                                       | Fig. |      |         | Unit |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|------|---------|------|

|      |          |                                                                                                                                                    |                                                                  |      | Min. | Max.    |      |

| G001 | VDD      | Supply Voltage                                                                                                                                     |                                                                  |      | -0.3 | 6.0     | V    |

| G002 | V()      | Voltage at<br>SIN, NSIN, PSIN, COS, NCOS, PCOS,<br>ZERO, NZERO, PZERO, VREF, MFP,<br>RCLK, NER, D07, NRD, NWR,<br>NRES, SCL, SDA                   |                                                                  |      | -0.3 | VDD+0.3 | V    |

| G003 | Imx(VDD) | Current in VDD                                                                                                                                     |                                                                  |      | -50  | 50      | mA   |

| G004 | Imx(GND) | Current in GND                                                                                                                                     |                                                                  |      | -50  | 50      | mA   |

| G005 | lc()     | Current in Clamping Diodes SIN,<br>NSIN, PSIN, COS, NCOS, PCOS, ZE-<br>RO, NZERO, PZERO, VREF, MFP,<br>RCLK, NER, D07, NRD, NWR,<br>NRES, SCL, SDA | MFP, D07, NWR<br>with input function                             |      | -5   | 5       | mA   |

| G006 | I()      | Current in SIN, COS, ZERO, VREF,<br>MFP, NER, D07, NWR, SCL                                                                                        | MFP, D07, NWR<br>with output function                            |      | -10  | 10      | mA   |

| G007 | llu()    | Pulse Current in all Pins<br>(Latch-Up Strength)                                                                                                   | pulse duration ≤ 10µs                                            |      | -100 | 100     | mA   |

| E001 | Vd()     | ESD Susceptibility at all Pins                                                                                                                     | MIL-STD-883, Method 3015, HBM;<br>100pf discharged through 1.5kΩ |      |      | 2       | kV   |

| TG1  | Tj       | Junction Temperature                                                                                                                               |                                                                  |      | -40  | 150     | °C   |

| TG2  | Ts       | Storage Temperature                                                                                                                                |                                                                  |      | -40  | 150     | °C   |

#### THERMAL DATA

Operating conditions: VDD= 5V ±10%

| ltem | Symbol | Parameter                               | Conditions | Fig. |      |      |      | Unit |

|------|--------|-----------------------------------------|------------|------|------|------|------|------|

|      |        |                                         |            |      | Min. | Тур. | Max. |      |

| T1   | Та     | Operating Ambient Temperature Range     |            |      | -20  |      | 70   | °C   |

|      |        | (extended temperature range on request) |            |      |      |      |      |      |

All currents into the device pins are positive; all currents out of the device pins are negative.

Rev D3, Page 5/21

#### **ELECTRICAL CHARACTERISTICS**

| tem   | Symbol     | Parameter                                            | Conditions                                     | Tj | Fig.     |      |      |             | Unit |

|-------|------------|------------------------------------------------------|------------------------------------------------|----|----------|------|------|-------------|------|

|       |            |                                                      |                                                | °C |          | Min. | Тур. | Max.        |      |

| Total | Device     |                                                      |                                                |    | <u> </u> |      |      |             |      |

| 001   | VDD        | Permissible Supply Voltage                           |                                                |    |          | 4.5  |      | 5.5         | V    |

| 002   | I(VDD)     | Supply Current                                       | outputs not active                             |    |          | 5    |      | 25          | mA   |

| 003   | Vt()hi     | Input Threshold Voltage hi at D0D7, MFP,NRD,NWR,NRES |                                                |    |          |      |      | 2           | V    |

| 004   | Vt()lo     | Input Threshold Voltage Io at D0D7, MFP,NRD,NWR,NRES |                                                |    |          | 0.8  |      |             | V    |

| 005   | Vt()hys    | Input Hysteresis at<br>D0D7, MFP,NRD,NWR,NRES        | Vt()hys= Vt()hi -Vt()lo                        |    |          | 100  |      |             | mV   |

| 006   | lin()      | Input Current at<br>D0D7, MFP,NRD,NWR,NRES           |                                                |    |          | -1   |      | +1          | μA   |

| 7     | Vs()lo     | Saturation Voltage lo at D0D7, MFP                   | l()= 4mA                                       |    |          |      |      | 0.4         | V    |

| 8     | Vs()hi     | Saturation Voltage hi at D0D7, MFP                   | Vs()hi= VDD -V();<br>I()= -4mA                 |    |          |      |      | 0.4         | V    |

| E001  | Vc()hi     | Clamp Voltage hi at all Pins                         | Vc()hi= V() -VDD;<br>I()= 1mA, other pins open |    |          | 0.3  |      | 1.5         | V    |

| E002  | Vc()lo     | Clamp Voltage lo at all Pins                         | I()= -1mA, other pins open                     |    |          | -1.5 |      | -0.3        | V    |

| Input | Amplifiers | SIN, COS, INDEX/ZERO                                 |                                                |    |          |      |      |             |      |

| 101   | Vin()      | Recommended Input Voltage<br>Range                   |                                                |    |          | 1    |      | 3.5         | Vpp  |

| 102   | Vos()      | Input Offset Voltage                                 | Vin()= 1VVDD -1V                               |    |          | -10  |      | +10         | mV   |

| 103   | lin()      | Input Current                                        |                                                |    |          | -50  |      | +50         | nA   |

| 104   | Vcm()      | Common Mode Voltage Range                            | lout()= 0±5mA                                  |    |          | 0.1  |      | VDD-<br>1.0 | V    |

| 105   | Vs()hi     | Saturation Voltage hi                                | Vs()hi= VDD -V(), lout()= -5mA                 |    |          |      |      | 0.5         | V    |

| 106   | Vs()lo     | Saturation Voltage lo                                | lout()= 5mA                                    |    |          |      |      | 0.5         | V    |

| 107   | SR0        | Slew-Rate                                            | CL= 0, $C_c$ = 0 ( $C_c$ programmed)           |    |          |      | 4    |             | V/µs |

| 108   | SR1        | Slew-Rate                                            | CL= 300pF, C <sub>c</sub> = 4pF                |    |          |      | 2    |             | V/µs |

| 109   | SR2        | Slew-Rate                                            | CL= 800pF, C <sub>c</sub> = 6.4pF              |    |          |      | 1.2  |             | V/µs |

| 110   | SR3        | Slew-Rate                                            | CL= 1.5nF, C <sub>c</sub> = 12pF               |    |          |      | 0.8  |             | V/µs |

| 111   | GBW0       | Gain Bandwidth Product                               | CL= 0, $C_c$ = 0 ( $C_c$ programmed)           |    |          |      | 4.1  |             | MHz  |

| 112   | GBW1       | Gain Bandwidth Product                               | CL= 300pF, C <sub>c</sub> = 4pF                | _  |          |      | 1    |             | MHz  |

| 113   | GBW2       | Gain Bandwidth Product                               | CL= 800pF, C <sub>C</sub> = 6.4pF              | _  | <u> </u> |      | 0.75 |             | MHz  |

| 114   | GBW3       | Gain Bandwidth Product                               | CL= 1.5nF, C <sub>c</sub> = 12pF               |    |          |      | 0.4  |             | MHz  |

|       | ence VRE   |                                                      |                                                | _  | <u> </u> |      |      |             |      |

| 115   | V(VREF)    | Reference Voltage                                    | I(VREF)= 01mA                                  |    |          | 2.2  | 2.4  | 2.6         | V    |

|       | Monitor N  |                                                      |                                                |    |          |      |      |             |      |

| 201   | Vs()lo     | Saturation Voltage lo at NER                         | I(NER)= 5mA                                    | _  |          | _    | 0.2  | 0.7         | V    |

| 202   | lsc()lo    | Short-Circuit Current Io in NER                      | V(NER)= 0.4VDD+0.3V                            | _  |          | 5    |      | 21          | mA   |

| 203   | 10()       | Leakage Current in NER                               | V(NER)= 0VDD+0.3V,<br>NER= hi oder VDD< 0.3V   |    |          |      |      | 10          | μA   |

| 204   | VDDon      | Turn-on Threshold VDD                                |                                                | _  |          |      | 4.7  |             | V    |

| 205   | VDDoff     | Undervoltage Threshold VDD                           | decreasing voltage VDD                         | _  |          |      | 4.5  |             | V    |

| 206   | VDDhys     | Hysteresis                                           | VDDhys= VDDon -VDDoff                          | _  |          |      | 200  |             | mV   |

| 207   | VDDerr     | Supply Voltage VDD for Monitor<br>Operation          |                                                |    |          | 2.2  |      | 5.5         | V    |

Rev D3, Page 6/21

## **ELECTRICAL CHARACTERISTICS**

| ltem  | Symbol     | Parameter                                                          | Conditions                                                                                                                                                                        | Tj | Fig. |                      | 1          | 1                    | Unit              |

|-------|------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|----------------------|------------|----------------------|-------------------|

|       |            |                                                                    |                                                                                                                                                                                   | °C |      | Min.                 | Тур.       | Max.                 |                   |

| Oscil | lator RCL  | κ                                                                  | 1                                                                                                                                                                                 |    |      |                      |            |                      |                   |

| 301   | fmax       | Permissible Oscillator Frequency                                   |                                                                                                                                                                                   |    |      |                      |            | 5                    | MHz               |

| 302   | fosc       | Oscillator Frequency                                               | Rosc= 56kΩ<br>Rosc= 18.2kΩ                                                                                                                                                        |    |      | 550<br>1.6           | 670<br>1.8 | 800<br>2.0           | kHz<br>MHz        |

| 303   | R(RCLK)    | Permissible Resistor                                               |                                                                                                                                                                                   |    |      | 5                    |            | 500                  | kΩ                |

| 304   | Vt()hi     | Threshold Voltage hi                                               |                                                                                                                                                                                   |    |      |                      |            | 3                    | V                 |

| 305   | Vt()lo     | Threshold Voltage lo                                               | tw()lo< 10µs                                                                                                                                                                      |    |      | 0.8                  |            |                      | V                 |

| 306   | Vt()hys    | Hysteresis                                                         | Vt()hys= Vt()hi -Vt()lo                                                                                                                                                           |    |      | 100                  |            |                      | mV                |

| 307   | tmx()lo    | Permissible Pulse Width lo when<br>applying external clock signals |                                                                                                                                                                                   |    |      |                      |            | 10                   | μs                |

| Seria | EEPROM     | Interface SCL, SDA                                                 |                                                                                                                                                                                   |    |      |                      |            |                      |                   |

| 401   | Vt()hi     | Threshold Voltage hi                                               |                                                                                                                                                                                   |    |      |                      |            | 2                    | V                 |

| 402   | Vt()lo     | Threshold Voltage lo                                               |                                                                                                                                                                                   |    |      | 0.8                  |            |                      | V                 |

| 403   | Vt()hys    | Input Hysteresis                                                   | Vt()hys= Vt()hi -Vt()lo                                                                                                                                                           |    |      | 300                  |            |                      | mV                |

| 404   | Vs()lo     | Saturation Voltage lo                                              | l()= 4mA                                                                                                                                                                          |    |      |                      | 0.26       | 0.4                  | V                 |

| 405   | Vs()hi     | Saturation Voltage hi                                              | Vs()hi= VDD -V();<br>I()= -4mA                                                                                                                                                    |    |      |                      |            | 0.4                  | V                 |

| 406   | Rpu()      | Pull-up Resistor                                                   |                                                                                                                                                                                   |    |      | 5                    | 10         | 20                   | kΩ                |

| Conv  | erter Accu | racy                                                               |                                                                                                                                                                                   |    |      |                      |            |                      |                   |

| 501   | AAabs      | Absolute Angular Accuracy                                          | referred to 360° input signal;<br>VDD= 5V, V(SIN,COS)= 3Vpp,<br>RES= 256, ADAP= 0, FREQ= 1;<br>Rosc= 56kΩ, Tj= -2070°C<br>Rosc= 18.2kΩ, Tj= -2070°C<br>Rosc= 18.2kΩ, Tj= -40125°C |    |      | -0.8<br>-1.6<br>-2.8 |            | +0.8<br>+1.6<br>+2.8 | DEG<br>DEG<br>DEG |

| 502   | AArel      | Relative Angular Accuracy                                          | see 501, referred to period of AX<br>output signal;<br>Rosc= 56kΩ, Tj= -2070°C<br>Rosc= 18.2kΩ, Tj= -2070°C<br>Rosc= 18.2kΩ, Tj= -40125°C                                         |    |      | -20<br>-30<br>-30    |            | +20<br>+30<br>+30    | %<br>%<br>%       |

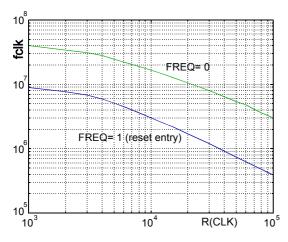

# ELECTRICAL CHARACTERISTICS DIAGRAMS

Fig. 1: oscillator frequency characteristics.

Rev D3, Page 7/21

#### **OPERATING REQUIREMENTS: Logic**

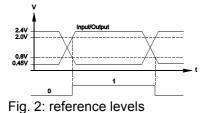

Operating conditions: VCC= 5V ±10%, Ta= -20..70°C, CL()= 150pF, input levels lo= 0..0.45V, hi= 2.4V..VCC, see Fig. 2 for reference levels and waveforms

| ltem  | Symbol       | Parameter                                                                                                                                | Conditions                                             | Fig. |               |                 | Unit |

|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|---------------|-----------------|------|

|       |              |                                                                                                                                          |                                                        |      | Min.          | Max.            |      |

| Read  | l cycle      |                                                                                                                                          |                                                        |      |               |                 |      |

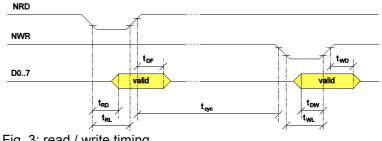

| 11    | trd          | Read Data Access Time:<br>data valid after NRD hi⊸lo                                                                                     | 1 <sup>st</sup> access with latching NG and COUNT data | 3    |               | 1.5x<br>td(CLK) |      |

|       |              |                                                                                                                                          | ongoing access                                         |      |               | 120             | ns   |

| 12    | tDF          | Read Data Hold Time:<br>ports high impedance after NRD lo⊸hi                                                                             |                                                        | 3    |               | 65              | ns   |

| 13    | trl          | Required Read Signal Duration at NRD                                                                                                     | SSI signal                                             | 3    | 200           | 2.5x            | ns   |

|       |              |                                                                                                                                          |                                                        |      |               | td(CLK)         |      |

| Write | cycle        |                                                                                                                                          |                                                        |      |               |                 |      |

| 14    | tow          | Write Data Setup Time:<br>data valid before NWR lo⊸hi                                                                                    |                                                        | 3    | 100           |                 | ns   |

| 15    | twD          | Write Data Hold Time:<br>data valid after NWR Io⊸hi                                                                                      |                                                        | 3    | 10            |                 | ns   |

| 16    | tw∟          | Required Write Signal Duration at NWR                                                                                                    |                                                        | 3    | 200           |                 | ns   |

| Write | e / read tim | ning                                                                                                                                     | -                                                      |      |               |                 |      |

| 17    | tcyc         | Recovery Time between Cycles:<br>NRD lo∽hi to NRD hi⊸lo,<br>NRD lo∽hi to NWR hi⊸lo,<br>NWR lo∽hi to NWR hi⊸lo,<br>NWR lo∽hi to NRD hi⊸lo |                                                        | 3    | 2×<br>td(CLK) |                 | ns   |

Fig. 3: read / write timing

#### **DESCRIPTION OF FUNCTIONS**

#### **Converter principle**

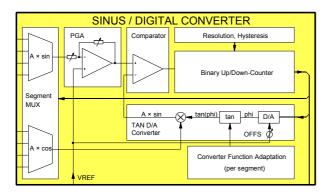

iC-NG is an analog-digital tracking-type converter (compensation process). The output value is stored in an up/down counter. This is converted to analog voltage by a D/A converter and compared to the input signal by a comparator. The comparator output controls the direction input of the counter. The count direction is maintained until the output voltage of the D/A converter, which is proportional to the output value, corresponds to the value of the input voltage.

Fig. 4: core of the TAN D/A converter

In contrast to conventional A/D converters, the output value in the sine/digital converter is proportional not to the input voltage but to its phase. In the following, the input value is referred to as "PHI" and the output value as "phi".

Fig. 5: converter principle

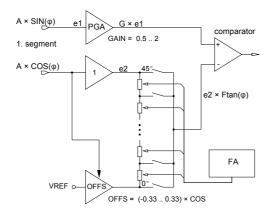

The phase is available at the input in the form A x SIN(PHI) and A x COS(PHI). From the output value, the tangent function is formed in the feedback loop and multiplied by COS(PHI). The result is compared to SIN(PHI). The rule for regulation is as follows:

$$A * SIN(\Phi) = A * COS(\Phi) \times TAN(\phi)$$

Since the tangent function has pole points and cannot be formed over a whole cycle, a cycle is divided into eight segments. For certain segments the input signals are reversed and the cotangent function is formed in the feedback loop. The segment changeover function is indicated in the following table:

|   | Segments      | Comparator Inputs |                         |  |  |  |  |  |

|---|---------------|-------------------|-------------------------|--|--|--|--|--|

| 1 | phi= 0°45°    | A×SIN(PHI)        | A×COS(PHI) ×  TAN(phi)  |  |  |  |  |  |

| 2 | phi= 45°90°   | A×COS(PHI)        | A×SIN(PHI) ×  COT(phi)  |  |  |  |  |  |

| 3 | phi= 90°135°  | -A×COS(PHI)       | A×SIN(PHI) ×  COT(phi)  |  |  |  |  |  |

| 4 | phi= 135°180° | A×SIN(PHI)        | -A×COS(PHI) ×  TAN(phi) |  |  |  |  |  |

| 5 | phi= 180°225° | -A×SIN(PHI)       | -A×COS(PHI) ×  TAN(phi) |  |  |  |  |  |

| 6 | phi= 225°270° | -A×COS(PHI)       | -A×SIN(PHI) ×  COT(phi) |  |  |  |  |  |

| 7 | phi= 270°315° | A×COS(PHI)        | -A×SIN(PHI) ×  COT(phi) |  |  |  |  |  |

| 8 | phi= 315°360° | -A×SIN(PHI)       | A×COS(PHI) ×  TAN(phi)  |  |  |  |  |  |

Fig. 6: segmentation

The sine/digital converter automatically runs via the shortest route into the correct segment and thus, with a static input signal, reaches its operating point after a maximum of n/2 clock cycles (n corresponds to the resolution).

A converter of the type described above will never reach a quiescent state. With a constant input signal, the counter would continuously increment or decrement one LSB, which is prevented here by hysteresis. A range is set up by the programmable hysteresis on both sides of the counter value and the input signal is checked over two clock cycles as to whether it is still within this range. The output frequency is therefore only half the clock frequency.

#### Rev D3, Page 9/21

#### Interfaces

The chip must be configured for the application in use after being switched on and after every reset. The settings and output values are stored in registers in iC-NG.

There are various ways of accessing these registers. If a serial EEPROM (e.g. SDA 2516, ST24CO2) is con-nected to pins SDA and SCL, all parameters will be read in automatically from there. The access mode is also determined by the EEPROM (ACCMOD(1:0)).

In the absence of an EEPROM, the access mode is set directly by pins SDA and SCL, which are equipped with internal pull-up resistors. Three modes are supported:

| SDA | SCL | Access Mode (no EEPROM) |

|-----|-----|-------------------------|

| 0   | 0   | Parallel absolute mode  |

| 1   | 0   | Serial mode             |

| 1   | 1   | Incremental mode        |

Fig. 7: access modes

#### 1. Parallel-absolute mode

This mode is suitable for using iC-NG as peripheral chip in an 8-bit bus system. The registers can be accessed via the data ports D0 to D7, controlled by read / write access inputs NWR and NRD. The two pins should not simultaneously receive low level.

Addressing is controlled via an internal address register and a status machine. The internal status (A or B) determines whether write access affects the address register or a data register addressed by it. The chip is in status A after a reset and each read, and in status B after each write (Figure 8).

Fig. 8: status control.

#### Write access

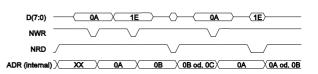

The data to be written is applied to pins D0 to D7 and a low pulse to NWR. The data is accepted with the rising edge at NWR. A write cycle consists of at least two accesses. The register address is given by the first access and the date by the second. The internal address register is automatically increased by one after each write. The registers of successive addresses can thus be easily written without having to reload the address register. A write cycle to address 10 and a subsequent read out are indicated in Figure 9.

Fig. 9: write access to address 10 and subsequent read out.

#### **Read access**

For a read cycle, the register address is also given first (write access), the data content then being read out with NRD at low.

The length of the output value is set to 1..4 bytes with the OUTSEL(1:0) registers. OUTSEL also influences the content of the internal address counter after a read. It is not increased if the length of the output value is set to one byte. Other settings reset the address counter to zero after the highest byte of the output value has been read, otherwise it is increased by one.

The outputs remain constant during the read process, even if the relevant register changes (except incremental signals and interrupt and error status).

The NG, COUNT and TACHO registers are again stored with the falling edge at NRD if OUTSEL has been programmed to zero or the address counter is at zero. It is thus possible to read a 4-byte output value in four accesses.

The interval between two consecutive pulses to NRD or NWR must be at least 3 clock cycles. The cyclic read out of a 2-byte output value (OUTSEL(1:0)= 1) is shown in Figure 10.

Fig. 10: cyclic read out of the output value (16-bit).

#### Rev D3, Page 10/21

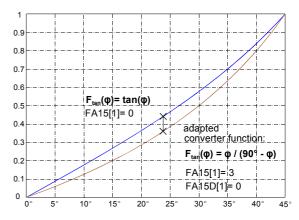

#### 2. Synchronous-serial mode with 33-bit format

In this mode, communication is via a synchronous twowire connection. The registers cannot be accessed; only the output value and the error bit are transmitted.

The two-wire connection exists of a clock input (NRD) and a data output with driver at NWR. Data transmission is controlled externally by the clock line.

The output value is latched with the first falling edge at NRD. With every subsequent rising edge the output value is serially output to NWR in binary code, beginning with the MSB set by OUTSEL. The error bit is transmitted after the output value.

In this mode, pin SDA can be used as serial data input. The data read in here at the beginning of the data transmission is output after the error bit.

A cyclic read out can be achieved by linking NWR to SDA. A one is output after the error bit as a stop bit.

To store the output value for a new data transmission, an interval of at least 64 clock pulses must be maintained at the clock input.

Fig. 11: synchronous-serial data transmission.

#### 3. Incremental mode

Here, every change of angle with respect to the set resolution is signaled as a change in output on track DO(AX) or D1(BX). The square-wave signals produced have a phase shift of plus or minus 90°, depending on the direction of rotation.

In addition, the input signals are compared to reference voltage VREF and output to pins D3(A4) and D4(B4). This corresponds to a resolution of four.

The zero signals, suitably prepared, are available at pins D2(ZX) and D5(Z4). A direction signal is also output to D6(ROT) and signals AX and BX are EX-OR-gated at D7(AXB).

Incremental mode can be emulated in parallel-absolute mode by reading address 4.

#### Resolution RES(4:0) and RES(6,5)

One period of the input signal is internally divided into eight segments. The following segments  $[45^{\circ}..90^{\circ}, 90^{\circ}..135^{\circ}, 135^{\circ}..180^{\circ}$  etc. to  $360^{\circ}$ ] are mapped on the first segment  $[0^{\circ}..45^{\circ}]$ . The resulting output resolution thus amounts to 8 times that of the TAN D/A converter.

The converter resolution per segment can be set to all whole-number values between 17 and 32. Subresolutions result only if every nth subdivision is used. A further decrease is possible by effecting a right shift by n-bit of the output value.

The following table shows all possible settings and resulting resolutions. With equal values, settings with more favorable characteristics are shown in bold type.

# Rev D3, Page 11/21

| _                          |            |                                        |                    |                    |                    |                        | TAN                | D/A Co             | nverter F          | Resolutio                   | on (per s          | egment             | )                  |                       |                    |                    |                    |

|----------------------------|------------|----------------------------------------|--------------------|--------------------|--------------------|------------------------|--------------------|--------------------|--------------------|-----------------------------|--------------------|--------------------|--------------------|-----------------------|--------------------|--------------------|--------------------|

| Reso                       | olution    | 32                                     | 31                 | 30                 | 29                 | 28                     | 27                 | 26                 | 25                 | 24                          | 23                 | 22                 | 21                 | 20                    | 19                 | 18                 | 17                 |

|                            | 1<br>"00"  | <b>256</b><br>[1F]                     | <b>248</b><br>[1E] | <b>240</b><br>[1D] | <b>232</b><br>[1C] | <b>224</b><br>[1B]     | <b>216</b><br>[1A] | <b>208</b><br>[19] | <b>200</b><br>[18] | <b>192</b><br>[17]          | <b>184</b><br>[16] | <b>176</b><br>[15] | <b>168</b><br>[14] | <b>160</b><br>[13]    | <b>152</b><br>[12] | <b>144</b><br>[11] | <b>136</b><br>[10] |

| pesr                       | 2<br>"00"  | <b>128</b><br>[0F]                     |                    | <b>120</b><br>[0E] |                    | <b>112</b><br>[0D]     |                    | <b>104</b><br>[0C] |                    | <b>96</b><br>[0B]           |                    | <b>88</b><br>[0A]  |                    | <b>80</b><br>[09]     |                    | <b>72</b><br>[08]  |                    |

| ivisions (                 | 4<br>"00"  | <b>64</b><br>[07]                      |                    |                    |                    | <b>56</b><br>[06]      |                    |                    |                    | <b>48</b><br>[05]           |                    |                    |                    | <b>40</b><br>[04]     |                    |                    |                    |

| all n-th subdivisions used | 8<br>"00"  | <b>32</b><br>[03]                      |                    |                    |                    |                        |                    |                    |                    | <b>24</b><br>[02]           |                    |                    |                    |                       |                    |                    |                    |

| all n                      | 16<br>"00" | <b>16</b><br>[01]                      |                    |                    |                    |                        |                    |                    |                    |                             |                    |                    |                    |                       |                    |                    |                    |

|                            | 32<br>"00" | <b>8</b><br>[00]                       |                    |                    |                    |                        |                    |                    |                    |                             |                    |                    |                    |                       |                    |                    |                    |

| Ľ,                         | 1<br>"01"  | 128<br>64<br>32<br>16<br>8<br><b>4</b> | 124                | 120<br>60          | 116                | 112<br>56<br><b>28</b> | 108                | 104<br><b>52</b>   | 100                | 96<br>48<br>24<br><b>12</b> | 92                 | 88<br><b>44</b>    | 84                 | 80<br>40<br><b>20</b> | 76                 | 72<br><b>36</b>    | 68                 |

| right shift by n-bit       | 2<br>"10"  | 64<br>32<br>16<br>8<br>4<br><b>2</b>   | 62                 | 60<br><b>30</b>    | 58                 | 56<br>28<br><b>14</b>  | 54                 | 52<br><b>26</b>    | 50                 | 48<br>24<br>12<br><b>6</b>  | 46                 | 44<br><b>22</b>    | 42                 | 40<br>20<br><b>10</b> | 38                 | 36<br><b>18</b>    | 34                 |

|                            | 3<br>"11"  | 32<br>16<br>8<br>4<br>2<br><b>1</b>    | 31                 | 30<br><b>15</b>    | 29                 | 28<br>14<br><b>7</b>   | 27                 | 26<br><b>13</b>    | 25                 | 24<br>12<br>6<br><b>3</b>   | 23                 | 22<br><b>11</b>    | 21                 | 20<br>10<br><b>5</b>  | 19                 | 18<br>9            | 17                 |

Fig. 12: programming the resolution: hexadecimal [1F] for RES(4:0), binary "00" for RES(6:5).

#### **Hysteresis**

If the maximum possible converter resolution is not used, hysteresis can be obtained from free resolution steps. In so doing, the resolution chosen determines the number of possible hysteresis settings.

The following are possible in compliance with the upper half of the table of resolution printed above:

|   | H      |    | Hysteresis given in % (resistive) |          |          |    |           |          |           |    |           |          |           |    |           |          |           |     |

|---|--------|----|-----------------------------------|----------|----------|----|-----------|----------|-----------|----|-----------|----------|-----------|----|-----------|----------|-----------|-----|

| 3 | Y<br>S | 0  | 625                               | 12.<br>5 | 187<br>5 | 25 | 31.<br>25 | 37.<br>5 | 43.<br>75 | 50 | 56.<br>25 | 62.<br>5 | 68.<br>75 | 75 | 81.<br>25 | 87.<br>5 | 93.<br>75 | 100 |

|   | 1      | -  | -                                 | -        | -        | -  | -         | -        | -         | -  | -         | -        | -         | -  | -         | -        | -         | 30  |

|   | 2      | 20 | -                                 | -        | -        | -  | -         | -        | -         | -  | -         | -        | -         | -  | -         | -        | -         | 30  |

|   | 4      | 20 | -                                 | -        | -        | -  | -         | -        | -         | 28 | -         | -        | -         | -  | -         | -        | -         | 30  |

|   | 8      | 20 | -                                 | -        | -        | 24 | -         | -        | -         | 28 | -         | -        | -         | 2C | -         | -        | -         | 30  |

|   | 16     | 20 | -                                 | 22       | -        | 24 | -         | 26       | -         | 28 | -         | 2A       | -         | 2C | -         | 2E       | -         | 30  |

|   | 32     | 20 | 21                                | 22       | 23       | 24 | 25        | 26       | 27        | 28 | 29        | 2A       | 2B        | 2C | 2D        | 2E       | 2F        | 30  |

Fig. 13: resistive hysteresis.

'-' indicates unauthorized programming.

When setting high converter resolutions which use all resolution steps, to produce hysteresis the resolution of the converter is increased in an intermediate step by switching on a capacitive voltage divider.

Hysteresis can be set in intervals of 5% from 0..95% in conjunction with the output values given in the upper half of the above table of resolution (output values are without a right shift).

|   |        |                               | Hysteresis given in % (capacitive)                          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|--------|-------------------------------|-------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   | Н      | 0                             | 5                                                           | 10 | 15 | 20 | 25 | 30 | 35 | 40 | 45 | 50 | 55 | 60 | 65 | 70 | 75 | 80 | 85 | 90 | 95 |

|   | Y<br>S | 00                            | 00 01 02 03 04 05 06 07 10 11 12 13 14 15 16 17 1C 1D 1E 1F |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| l | Fic    | g. 14: capacitive hysteresis. |                                                             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

#### Rev D3, Page 12/21

laus

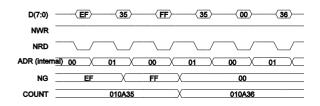

#### Programming the zero position

Fig. 15: programming the zero position.

A zero crossing can be set to multiples of  $45^{\circ}$  via register ZCONF(2:0) (Figure 15). If the value is an even number (ZCONF0= 0), then each of the zero pulses (ZX and Z4) are 1/2 period in width; otherwise their width is only 1/4 period.

Z4 remains ungated when ZCONF3= 1. ROT inverts the direction of rotation referred to the zero point set by ZCONF.

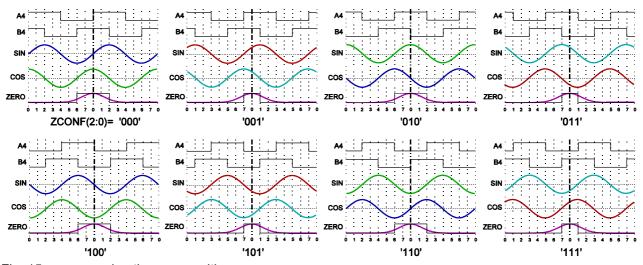

# Converter adaptation to non-sinusoidal input signals

Adaptation is carried out in two steps and is performed separately for each of the eight segments.

In the **first step**, the offset and gain of the programmable gain amplifier (PGA) are set. The offset is corrected so that at the beginning of the first segment the signal at the PGA output is zero  $(\sin 0^\circ = 0)$ . The signal at the end of the first segment is then adapted to the cosine signal  $(\sin 45^\circ = \cos 45^\circ)$  with the gain setting. This adjustment should be tested by changing the direction of rotation and also by increasing the resolution.

In the **second step**, the transfer function in the TAN D/A converter is set to the value  $e_1/e_2$  (e= input signal). In the basic setting ( $e_1 = \sin, e_2 = \cos$ ), the PGA has a gain of one and an offset of zero. The tangent function is formed in the feedback loop.

This two-step adaptation procedure is performed accordingly in all segments. To activate converter adaptation, bit ADAP must be set and the entire storage area of the adaptation parameters written in one write cycle.

**Restrictions**: read access to the signal adaptation registers is not permitted. The internal address register must not point to the adaptation register during converter operation (addresses 16..127 are not permitted during operation).

The following diagram shows how the transfer function must be adapted in the feedback loop in the first segment should triangular signals be available at the input.

Fig. 16: transfer function in feedback loop (1st segment). The transfer function is more sharply curved for triangular input signals.

Rev D3, Page 13/21

#### **Period counter**

The 24-bit position counter can be read via the COUNT registers (addresses 1..3). Write access is not possible, yet the counter can be reset by CLC.

Under normal circumstances (SIC= 0), the counter is increased or decreased by an overflow of the 8-bit interpolation register NG (address 0), according to the direction of run. Together with register NG, the output value is 4 bytes.

The counter stimulus is monitored by the separate fourfold edge evaluation feature and guarantees that the count functions perform properly even when input frequencies are excessively high, provided the phase does not step by more than 90°. If this is the case, error flag STEPINP is set.

CBZ must be set should the counter be reset by the zero pulse. Counting is enabled by pin MFP (SLCNTEN= 1) or alternatively by register COUNTEN (SLCNTEN= 0).

For measurement applications, the position counter input can also be switched to the interpolated output pulse (SIC= 1).

#### Interrupt and error messages

The occurrence of an interrupt or error is indicated in the interrupt and error status register at address 6. Using registers LATINT and LATERR (address 11), the user can decide whether the information is to be displayed only as long as the interrupt or error persists or whether this information should be stored.

Pins MFP for interrupts (active high) and NER for errors (active low) are available for message outputs; authorization for signaling must be granted. Pin MFP must have output function (SLCNTEN= 0) to enable displaying.

#### **RPM/Speed acquisition**

The TACHO speed data register can be used to access a very simple RPM/speed log. The number of clock pulses between two consecutive output values is recorded here as a ones complement. The register is updated with each change in output value. No digital filtering is performed.

#### System clock

An internal oscillator is available as a clock generator. The frequency is determined by an external resistor.

In addition, register FREQ can be used to increase the clock rate tenfold. This is prudent with a high input frequency if merely the number of revolutions is to be determined.

Alternatively, the system clock can be fed in externally. The frequency should be between 0Hz and fmax and should not exceed the maximum low pulse duration (see characteristics), as otherwise the internal clock oscillator switches in.

Rev D3, Page 14/21

# PROGRAMMING

| Registe | r Configuration                                 |                                                 |

|---------|-------------------------------------------------|-------------------------------------------------|

| Adr     | read                                            | write                                           |

| 0-3     | Data Output Register                            | Target Position                                 |

| 4       | Incremental Signals                             | -                                               |

| 5       | Speed Data                                      | -                                               |

| 6       | Interrupt / Error Messages                      | -                                               |

| 7       | Rotation Direction, Resolution Setting          | Rotation Direction, Resolution Setting          |

| 8       | Data Shift, PGA Bypass, Converter Hysteresis    | Data Shift, PGA Bypass, Converter Hysteresis    |

| 9       | Operation Mode, Counter Depth, Z Index Position | Operation Mode, Counter Depth, Z Index Position |

| 10      | Counter Settings                                | Counter Settings                                |

| 11      | Interrupt / Error Message Enable                | Interrupt / Error Message Enable                |

| 12      | Input Amplifier Compensation                    | Input Amplifier Compensation                    |

| 13      | Clock Frequency Select                          | Clock Frequency Select                          |

| 16-23   | -                                               | Gain / Fullscale Calibration                    |

| 24-31   | -                                               | Offset Adjustment                               |

| 32-127  | -                                               | TAN Function Adaptation                         |

| Register Configuration |      |                                     |         |          |               |                       |                       |                       |                      |  |  |  |

|------------------------|------|-------------------------------------|---------|----------|---------------|-----------------------|-----------------------|-----------------------|----------------------|--|--|--|

|                        | Name |                                     |         |          |               |                       |                       |                       | Reset entry          |  |  |  |

| Adr                    | 7    | 6                                   | 5       | 4        | 3             | 2                     | 1                     | 0                     | 7:0                  |  |  |  |

| 0                      |      |                                     |         | NG(7:0)  | resp. TPOS(7  | 7:0)                  |                       |                       | 00                   |  |  |  |

| 3-1                    |      |                                     |         | COUNT(23 | 0) resp. TPO  | S(31:8)               |                       |                       | 00 00 00             |  |  |  |

| 4                      | AXB  | ROT                                 | Z4      | B4       | A4            | ZX                    | BX                    | AX                    | -                    |  |  |  |

| 5                      |      | TACHO(7:0)                          |         |          |               |                       |                       |                       |                      |  |  |  |

| 6                      |      | ERRV STEPINP MAXFREQ POSCOMP NGUPDT |         |          |               |                       |                       |                       |                      |  |  |  |

| 7                      | ROT  | ROT RES(6:0)                        |         |          |               |                       |                       |                       |                      |  |  |  |

| 8                      | NGLJ | ADAP                                |         |          | H             | YS(5:0)               |                       |                       | 30 (B0) <sup>1</sup> |  |  |  |

| 9                      | ACCI | MOD(1:0)                            | OUTS    | EL(1:0)  |               | ZCON                  | IF(3:0)               |                       | 00 (01) <sup>2</sup> |  |  |  |

| 10                     |      |                                     |         | CLC      | CBZ           | COUNTEN               | SLCNTEN               | SIC                   | 00                   |  |  |  |

| 11                     |      | LATERR                              | LATINT  | EN4      | EN3           | EN2                   | EN1                   | EN0                   | 05                   |  |  |  |

| 12                     |      | CZEI                                | RO(3:0) |          |               | CSIN                  | <b>I</b> (3:0)        |                       | FF                   |  |  |  |

| 13                     |      |                                     |         |          | FREQ          | reserved <sup>3</sup> | reserved <sup>3</sup> | reserved <sup>3</sup> | 08                   |  |  |  |

| 16-23                  |      | Gain / Fullscale Calibration        |         |          |               |                       |                       |                       |                      |  |  |  |

| 24-31                  |      |                                     |         | Offs     | et Adjustment |                       |                       |                       | FF                   |  |  |  |

| 32-127                 |      |                                     |         | TAN Fu   | nction Adapta | tion                  |                       |                       | FF                   |  |  |  |

<sup>1</sup> Synchronous-serial mode

<sup>2</sup> Incremental mode

<sup>3</sup> Register programming to 1 is not permitted

Rev D3, Page 15/21

| Data Out                                                    | Data Output Register   Interpolation (read only)   Adr: 0 |              |                |         |         |         |         |         |  |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------|--------------|----------------|---------|---------|---------|---------|---------|--|--|--|--|

| Bit                                                         | 7                                                         | 6            | 5              | 4       | 3       | 2       | 1       | 0       |  |  |  |  |

| Name                                                        | NG7                                                       | NG6          | NG5            | NG4     | NG3     | NG2     | NG1     | NG0     |  |  |  |  |

| Period Count 1.Byte (write only) Adr: 1                     |                                                           |              |                |         |         |         |         |         |  |  |  |  |

| Bit                                                         | 7                                                         | 6            | 5              | 4       | 3       | 2       | 1       | 0       |  |  |  |  |

| Name COUNT7 COUNT6 COUNT5 COUNT4 COUNT3 COUNT2 COUNT1 COUNT |                                                           |              |                |         |         |         |         |         |  |  |  |  |

|                                                             | Perio                                                     | d Count 2.By | /te (write onl | y)      |         |         |         | Adr: 2  |  |  |  |  |

| Bit                                                         | 7                                                         | 6            | 5              | 4       | 3       | 2       | 1       | 0       |  |  |  |  |

| Name                                                        | COUNT15                                                   | COUNT14      | COUNT13        | COUNT12 | COUNT11 | COUNT10 | COUNT9  | COUNT8  |  |  |  |  |

|                                                             | Perio                                                     | d Count 3. B | yte (write on  | ly)     | •       | •       | •       | Adr: 3  |  |  |  |  |

| Bit                                                         | 7                                                         | 6            | 5              | 4       | 3       | 2       | 1       | 0       |  |  |  |  |

| Name                                                        | COUNT23                                                   | COUNT22      | COUNT21        | COUNT20 | COUNT19 | COUNT18 | COUNT17 | COUNT16 |  |  |  |  |

|                                                             |                                                           |              |                |         |         |         |         |         |  |  |  |  |

|                                                             | 7.0)                                                      |              |                |         |         |         |         |         |  |  |  |  |

ADR 0, NG(7:0) ADR 3:1, COUNT(23:0)

| Target Po                   | Target Position 1. Byte (write only)Adr: 0 |                |        |        |        |        |        |        |  |  |  |  |  |

|-----------------------------|--------------------------------------------|----------------|--------|--------|--------|--------|--------|--------|--|--|--|--|--|

| Bit                         | 7                                          | 6              | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |  |

| Name                        | TPOS7                                      | TPOS6          | TPOS5  | TPOS4  | TPOS3  | TPOS2  | TPOS1  | TPOS0  |  |  |  |  |  |

| 2. Byte (write only) Adr: 1 |                                            |                |        |        |        |        |        |        |  |  |  |  |  |

| Bit                         | 7                                          | 6              | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |  |

| Name                        | TPOS15                                     | TPOS14         | TPOS13 | TPOS12 | TPOS11 | TPOS10 | TPOS9  | TPOS8  |  |  |  |  |  |

|                             | 3. By                                      | te (write only | )      |        |        |        |        | Adr: 2 |  |  |  |  |  |

| Bit                         | 7                                          | 6              | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |  |

| Name                        | TPOS23                                     | TPOS22         | TPOS21 | TPOS20 | TPOS19 | TPOS18 | TPOS17 | TPOS16 |  |  |  |  |  |

|                             | 4. By                                      | te (write only | )      |        |        |        |        | Adr: 3 |  |  |  |  |  |

| Bit                         | 7                                          | 6              | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |  |

| Name                        | TPOS31                                     | TPOS30         | TPOS29 | TPOS28 | TPOS27 | TPOS26 | TPOS25 | TPOS24 |  |  |  |  |  |

|                             | -                                          |                |        |        |        |        |        |        |  |  |  |  |  |

ADR 3:0, TPOS(31:0)

| Increment    | al Signals                                              | (read)          |                 |                   |                |                  |  | Adr: 4 |  |  |  |

|--------------|---------------------------------------------------------|-----------------|-----------------|-------------------|----------------|------------------|--|--------|--|--|--|

| Bit<br>Name  | 7<br>AXB                                                | 6<br>ROT        |                 |                   |                |                  |  |        |  |  |  |

| Bit 0, AX    | Bit 0, AX Incremental track A (with the set resolution) |                 |                 |                   |                |                  |  |        |  |  |  |

| Bit 1, BX    |                                                         | Incremental tra | ack B (with the | e set resolution) | )              |                  |  |        |  |  |  |

| Bit 2, ZX    |                                                         | Zero signal (ga | ted with AX, I  | 3X in accordance  | ce with ZCONF( | 2:0) definition) |  |        |  |  |  |

| Bit 3, A4    |                                                         | Incremental tra | ack A (with a r | esolution of 4)   |                |                  |  |        |  |  |  |

| Bit 4, B4    |                                                         | Incremental tra | ack B (with a r | esolution of 4)   |                |                  |  |        |  |  |  |

| Bit 5, Z4    |                                                         | Zero signal (ga | ted with A4, E  | 34 in accordanc   | e with ZCONF   | 3:0) definition) |  |        |  |  |  |

| Bit 6<br>ROT |                                                         |                 |                 |                   |                |                  |  |        |  |  |  |

| Bit 7, AXB   |                                                         |                 |                 |                   |                |                  |  |        |  |  |  |

## Rev D3, Page 16/21

| Speed Da      | ta (read only        | <u>()</u>                                            |                 |                 |                 |                     |                  | Adr: 5      |

|---------------|----------------------|------------------------------------------------------|-----------------|-----------------|-----------------|---------------------|------------------|-------------|

| Bit<br>Name   | 7<br>TACHO7          | 6<br>TACHO6                                          | 5<br>TACHO5     | 4<br>TACHO4     | 3<br>TACHO3     | 2<br>TACHO2         | 1<br>TACHO1      | 0<br>TACHO0 |

| Adr 5, TACH   | O(7:0)               |                                                      |                 |                 |                 |                     |                  |             |

| Interrupt /   | Error Mess           | ages (active                                         | e high, read    | l only)         |                 |                     |                  | Adr: 6      |

| Bit<br>Name   | 7                    | 6                                                    | •               | 4<br>ERRV       | 3<br>STEPINP    | 2<br>MAXFREQ        | 1<br>POSCOMP     | 0<br>NGUPDT |

| Ŭ             | is always set ev     |                                                      | sary interrupts | or errors are   | not enabled to  | be displayed.       |                  |             |

| Bit 0, NGUPI  | DT Change            | · · · · ·                                            | as changed (m   | essage is set   | over a clock cy | cle)                |                  |             |

| Target Po     | sition Chec          | k (Interrupt)                                        | U (             |                 |                 |                     |                  |             |

| Bit 1, POSCO  | OMP (                | Output value m                                       | atches target   | position (depth | n of comparison | in accordance w     | ith OUTSEL(1:0)  | definition) |

| Frequenc      | <b>y Error 1</b> (Er | ror)                                                 |                 |                 |                 |                     |                  |             |

| Bit 2, MAXFF  |                      | nput frequency                                       |                 |                 | ion. COUNT(23   | 3:0) valid, AX/BX i | invalid          |             |

| Frequenc      | y Error 2 (Er        | ror)                                                 |                 |                 |                 |                     |                  |             |

| Bit 3, STEPII | r                    | The input signa<br>neously. COUN<br>(monitoring pru- | T(23:0) invalio | ł               | -               | cycle, i.e. A4 and  | I B4 have change | d simulta-  |

| Undervolt     | age (Error)          |                                                      |                 |                 |                 |                     |                  |             |

| Bit 4, ERRV   |                      | Supply voltage                                       | too low         |                 |                 |                     |                  |             |

| Resolution Setting, Rotation Direction Adr: 7 |     |      |      |      |      |      |      |      |  |  |  |

|-----------------------------------------------|-----|------|------|------|------|------|------|------|--|--|--|

| Bit                                           | 7   | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

| Name                                          | ROT | RES6 | RES5 | RES4 | RES3 | RES2 | RES1 | RES0 |  |  |  |

| Resolution          | Setting                  |                                                                                                                                                                                                                   |

|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 40<br>RES(4:0)  | '00'h<br><br>'1F'h       | TAN D/A converter resolution per segment = 1<br><br>TAN D/A converter resolution per segment = 32                                                                                                                 |

| Bit 6,5<br>RES(6:5) | 0 0<br>0 1<br>1 0<br>1 1 | Resolution equals 8 times the TAN D/A converter resolution<br>Output value shifted 1 bit to the right (resolution halved)<br>Output value shifted 2 bits to the right<br>Output value shifted 3 bits to the right |

| Rotation Di         | rection                  |                                                                                                                                                                                                                   |