## iC-VRV

### BIDIRECTIONAL µP INTERFACE TO 24V

Rev A2, Page 1/12

### **FEATURES**

- ◆ 2 x 4 bidirectional input/output stages at 24 V

- ♦ Input/output mode programmable for each 4 bits

- Guaranteed low-side driving capability of 100 mAdc and 500 mApeak for pulse load

- Short-circuit-proof driver with high electric strength up to 48 V

- Low saturation voltage of 0.4 V at 10 mA and 1.5 V at 500 mA

- Programmable pull-down current sources

- Built-in free-wheeling diodes with externally accessible common cathode

- Flashing function for the outputs

- Programmable digital input filters with externally adjusted filtering times

- Bus capability via high-speed microprocessor interface

- ♦ Programmable interrupt output

- Shutdown at overtemperature and low voltage

### **APPLICATIONS**

Dual quad low-side driver as bidirectional μP interface with digital filtering in 24 V industrial applications

Rev A2, Page 2/12

### **DESCRIPTION**

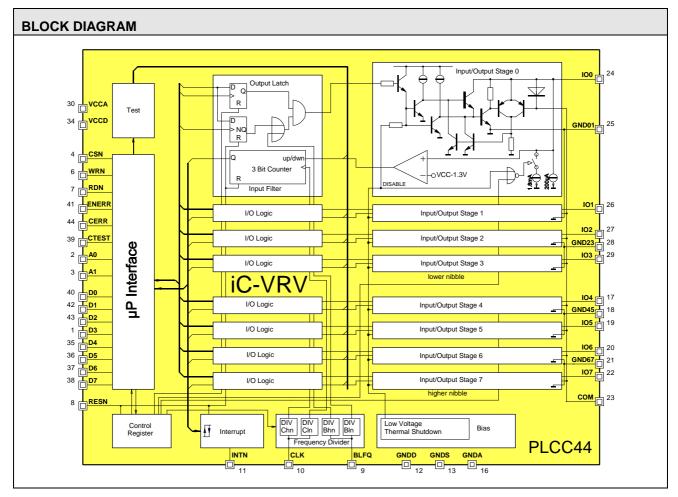

iC-VRV is an 8-fold low-side driver with integrated control logic which is divided internally into two mutually independent blocks (nibbles).

In the input mode, ports IO0 to IO7 can be used to record logical levels. In this process, a programmable pull-down current (200  $\mu$ A or 2 mA) sets a defined level and functions as the biasing current for switching contacts. The stages programmed as outputs can drive any desired loads (e. g. lamps, long cables, relays) at a continuous current of 100 mA or 500 mA in pulse operation. The free-wheeling currents created upon each stage turn-off are discharged through the integrated free-wheeling diodes to a voltage applied externally to the COM pin; a circuit with a Zener diode is also possible.

In the event of a short circuit, a protective circuit breaker ensures that the output stage affected does not just simply switch off but is instead clocked as a function of the load. As a result, the current assumes a low average value. The output stage is ready for operation immediately just as soon as the cause of the short circuit has been eliminated.

The shutdown at overtemperature protects the IC against thermal destruction by causing the output stages to turn off and the pull-down currents to be reduced from 2 mA to 200  $\mu$ A. This shutdown is also triggered in case of undervoltage at VCC.

Due to the microprocessor interface the iC-VRV can be operated directly on a bus system. The interface consists of the data bits D0 to D7 and the associated control signals A0, A1, CSN, WRN and RDN. The signal CLK clocks the implemented digital input filter and BLFQ clocks the programmed flashing function. In the event of a signal change of the I/O pins programmed as inputs, an interrupt signal can be generated at output INTN.

Activating the input RESN resets the initial condition.

Chip programming is conducted via four addresses at A0 and A1. During this programming, presettings for flashing frequencies, filtering times, interrupt control, pull-down currents and input/output mode, etc. are stored in two registers (CONTROL WORD1+2).

All inputs and outputs are protected with diodes against destruction due to ESD.

## iC-VRV

## BIDIRECTIONAL µP INTERFACE TO 24V

Rev A2, Page 3/12

### PACKAGES PLCC44 to JEDEC Standard

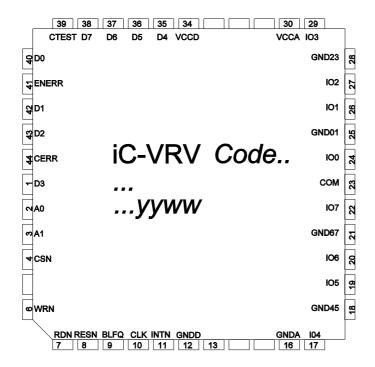

### **PIN CONFIGURATION PLCC44**

(top view)

### **PIN FUNCTIONS PLCC44**

| No. | Name  | Function | Description                         | No.    | Name  | Function | Description                       |

|-----|-------|----------|-------------------------------------|--------|-------|----------|-----------------------------------|

| 1   | D3    | В        | Bus Data Bit 3                      | 23     | COM   |          | Diodes, common cathode            |

| 2   | A0    | I        | Address                             | 24     | IO0   | В        | I/O Stage 0                       |

| 3   | A1    | 1        | Address                             | 25     | GND01 |          | Ground Stage 0+1                  |

| 4   | CSN   | 1        | Chip Select                         | 26     | IO1   | В        | I/O Stage 1                       |

| 5   | n.c.  |          | •                                   | 27     | 102   | В        | I/O Stage 2                       |

| 6   | WRN   | 1        | Write Enable                        | 28     | GND23 |          | Ground Stage 2+3                  |

| 7   | RDN   | 1        | Read Enable                         | 29     | 103   | В        | I/O Stage 3                       |

| 8   | RESN  | 1        | Reset                               | 30     | VCCA  |          | +5 V Supply (analog section)      |

| 9   | BLFQ  | i        | Clock, flashing function            | 31     | n.c.  |          | to the property (amount greening) |

| 10  | CLK   | 1        | Clock, filter function              | 32     | n.c.  |          |                                   |

| 11  | INTN  | 0        | Interrupt Report                    | 33     | n.c.  |          |                                   |

| 12  | GNDD  | •        | Digital Ground                      | 34     | VCCD  |          | +5 V Supply (digital section)     |

| 13  | n.c.  |          | - ·9·····                           | 35     | D4    | В        | Bus Data Bit 4                    |

| 14  | n.c.  |          |                                     | 36     | D5    | В        | Bus Data Bit 5                    |

| 15  | n.c.  |          |                                     | 37     | D6    | В        | Bus Data Bit 6                    |

| 16  | GNDA  |          | Analog Ground                       | 38     | D7    | В        | Bus Data Bit 7                    |

| 17  | 104   | В        | I/O Stage 4                         | 39(*)  | CTEST | _        | 240 2414 211 1                    |

| 18  | GND45 | _        | Ground Stage 4+5                    | 40     | D0    | В        | Bus Data Bit 0                    |

| 19  | 105   | В        | I/O Stage 5                         | 41(*)  | ENERR | _        | 240 2414 211 0                    |

| 20  | 106   | В        | I/O Stage 6                         | 42     | D1    | В        | Bus Data Bit 1                    |

| 21  | GND67 | _        | Ground Stage 6+7                    | 43     | D2    | В        | Bus Data Bit 2                    |

| 22  | 107   | В        | I/O Stage 7                         | 44(x)  | CERR  | -        | 240 2414 211 2                    |

|     |       | -        | • • • • • • • • • • • • • • • • • • | 1 1(X) | 0=    |          |                                   |

<sup>\*:</sup> pin needs external wiring to Ground

Function: I = Input, O = Output, B = bidirectional

x: pin should left open

Rev A2, Page 4/12

### **PROGRAMMING**

| Sele       | ction | of functions      | 1                 |                   |                        |                   |                   |                   |                        |  |  |

|------------|-------|-------------------|-------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------------|--|--|

|            |       | Data Word         | D7D0              |                   |                        |                   |                   |                   |                        |  |  |

|            |       | higher nib        | ble               |                   |                        | lower nibble      |                   |                   |                        |  |  |

|            |       | Selected I/       | O Stage fur       | nction:           |                        |                   |                   |                   |                        |  |  |

| Addr       | ess   | Input             |                   | Output            |                        | Input             |                   | Output            |                        |  |  |

| <b>A</b> 1 | A0    | Write             | Read              | Write             | Read                   | Write             | Read              | Write             | Read                   |  |  |

| 0          | 0     | Test Pattern      | IR Inputs         | Outputs           | Outputs                | Test Pattern      | IR Inputs         | Outputs           | Outputs                |  |  |

| 0          | 1     | IR Enable         | IR Enable         | Pulse Enable      | Pulse Enable           | IR Enable         | IR Enable         | Pulse Enable      | Pulse Enable           |  |  |

| 1          | 0     | Control<br>Word 2 | Inputs            | Control<br>Word 2 | Feedback<br>I/O Stages | Control<br>Word 2 | Inputs            | Control<br>Word 2 | Feedback<br>I/O Stages |  |  |

| 1          | 1     | Control<br>Word 1 | Control<br>Word 1 | Control<br>Word 1 | Control<br>Word 1      | Control<br>Word 1 | Control<br>Word 1 | Control<br>Word 1 | Control<br>Word 1      |  |  |

### Reading the inputs or the output feedback (IO7..0 to D7..0)

I/O stage with input function: A high level at IOx generates a high signal at Dx (selection of functions: read inputs) during the course of the digital hysteresis.

I/O stage with output function: A high level at IOx generates a low signal at Dx (selection of functions: read feedback of the outputs).

The inversion while reading back the outputs (I/O stage with output function) occurs so that the same signal is applied to Dx as was programmed for switching the output stage on or off, for example: switching on the final stage with Dx = high results in low level at IOx. After the digital hysteresis ends, Q becomes low, the microprocessor interface inverts this message and a high signal can be read back via Dx. The microprocessor can check the output state in this manner.

#### **Test**

The test circuit consists of registers which can be set via the microprocessor interface (test pattern). Its content is applied via constantly active OR gates to the counting direction inputs UP/DOWN (D7..0 to UP/DOWN7..0). In response to a reset (low signal at RESN) the registers are set to low; as a result, there is no effect on the UP/DOWN inputs.

In the test mode (control word 2, bit 2 and 6 at high) the comparators of the I/O stages are switched off and only the test registers continue to operate the UP/DOWN inputs. Any desired input signals can be entered to test all digital functions; the microprocessor can also conduct a system test in this manner.

### Interrupt enable

The interrupt generation can be activated separately for every I/O stage with input function. The interrupt enable is programmed via the data word DO..7 (function selection IR enable: 1 = stage relevant, 0 = stage not relevant). If a signal change is recognized for an I/O stage with input function - after the digital hysteresis due to change at Qx - and if this stage is enabled for interrupt generation, this is indicated with INTN = low. The interrupt message as well as the interrupt register which shows the stages with signal changes are reset via control word 2 (writing bit 0 = 1 is sufficient; bit 0 = 0 is set by the chip automatically).

Rev A2, Page 5/12

Signal changes which would be relevant for an interrupt generation could occur in the read-out phase following an interrupt message. These signal changes are lost when the interrupt register is deleted. As an alternative, the read-out of the interrupt register is possible (functional selection: read IR inputs). The registers can then be reset separately by blocking the IR enable for each reporting stage singly and then releasing it (functional selection: IR enable).

### Filter periods

The input comparator of each I/O stage switches the counting direction of a 3 bit counter. The counter output Q does not change until the final status is reached (to high for high level at IOx, to low for low level at IOx if constantly applied during the filter period).

The counter is clocked externally (pin CLK); the divisor for the clock frequency can be programmed separately for both nibbles. A low signal at reset input RESN resets the counters to the value 3. Due to the digital hysteresis, the change of an input signal is therefore not recognized until the selected filter period has elapsed.

### Pulse enable and pulse times

The flashing or pulsing function can be switched on separately for each I/O stage with output function. The programming of the divisors for the flashing frequency input BLFQ (control word 1, bits 0,1 and 4,5) is conducted for each nibble. The clock signal at BLFQ is transfered with the slope of CLK (synchronized). For this reason the clock frequency for CLK must be higher than the clock frequency for BLFQ, e. g. 2 MHz for CLK and 50 Hz for BLFQ.

| Control W   | Control Word 1 |          |          |              |          |          |          |          |

|-------------|----------------|----------|----------|--------------|----------|----------|----------|----------|

|             | higher nibble  |          |          | lower nibble |          |          |          |          |

| Bit<br>Name | 7<br>FH0       | 6<br>FH1 | 5<br>PH0 | 4<br>PH1     | 3<br>FL0 | 2<br>FL1 | 1<br>PL0 | 0<br>PL1 |

| Control          | Control Word 1 (lower nibble) |                                                           |                                                       |                         |                  |                                           |  |  |  |  |

|------------------|-------------------------------|-----------------------------------------------------------|-------------------------------------------------------|-------------------------|------------------|-------------------------------------------|--|--|--|--|

| Filtering        | Time                          |                                                           |                                                       | Flashing Pulse Duration |                  |                                           |  |  |  |  |

| Bit 3<br>FLO     | Bit 2<br>FL1                  |                                                           |                                                       | Bit 1<br>PLO            | Bit 0<br>PL1     |                                           |  |  |  |  |

| 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1              | 14.5 * CLK<br>896.5 * CLK<br>3584.5 * CLK<br>7168.5 * CLK | ± 1 * CLK<br>± 64 * CLK<br>± 256 * CLK<br>± 512 * CLK | 0<br>1<br>0<br>1        | 0<br>0<br>1<br>1 | BLFQ<br>BLFQ * 2<br>BLFQ * 4<br>BLFQ * 16 |  |  |  |  |

| Contro                                 | l Word 1         | (higher nibble)                                           |                                                       |              |                  |                                           |  |  |

|----------------------------------------|------------------|-----------------------------------------------------------|-------------------------------------------------------|--------------|------------------|-------------------------------------------|--|--|

| Filtering Time Flashing Pulse Duration |                  |                                                           |                                                       |              |                  |                                           |  |  |

| Bit 7<br>FHO                           | Bit 6<br>FH1     |                                                           |                                                       | Bit 5<br>PHO | Bit 4<br>PH1     |                                           |  |  |

| 0<br>1<br>0<br>1                       | 0<br>0<br>1<br>1 | 14.5 * CLK<br>896.5 * CLK<br>3584.5 * CLK<br>7168.5 * CLK | ± 1 * CLK<br>± 64 * CLK<br>± 256 * CLK<br>± 512 * CLK | 0<br>1<br>0  | 0<br>0<br>1<br>1 | BLFQ<br>BLFQ * 2<br>BLFQ * 4<br>BLFQ * 16 |  |  |

## iC-VRV

## BIDIRECTIONAL µP INTERFACE TO 24V

Rev A2, Page 6/12

| Control Word 2 |               |           |          |               |              |           |          |          |

|----------------|---------------|-----------|----------|---------------|--------------|-----------|----------|----------|

|                | higher nibble |           |          |               | lower nibble |           |          |          |

| Bit<br>Name    | 7<br>NIOH     | 6<br>TSTH | 5<br>IBH | 4<br>not used | 3<br>NIOL    | 2<br>TSTL | 1<br>IBL | 0<br>EOI |

| Control V       | Vord 2 (lo                                         | wer nibble)                                                                                                            |  |  |  |  |  |

|-----------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Interrupt       |                                                    |                                                                                                                        |  |  |  |  |  |

| Bit 0<br>(EOI)  | 0                                                  | Interrupt is not cancelled Clearing Interrupt                                                                          |  |  |  |  |  |

| Current S       | Current Sources at I/O Pins                        |                                                                                                                        |  |  |  |  |  |

| Bit 1<br>(IBL)  | Pull-Down Current 200 μA<br>Pull-Down Current 2 mA |                                                                                                                        |  |  |  |  |  |

| Test            |                                                    |                                                                                                                        |  |  |  |  |  |

| Bit 2<br>(TSTL) | 0                                                  | Feedback of I/O stages active (OR gated with test pattern) Test pattern activated, feedback of I/O stages switched off |  |  |  |  |  |

| Input/Outp      | Input/Output Mode                                  |                                                                                                                        |  |  |  |  |  |

| Bit 3<br>(NIOL) | Input Mode<br>Output Mode                          |                                                                                                                        |  |  |  |  |  |

| Control V                      | Vord 2 (hi                            | gher nibble)                                                                                                           |  |  |  |  |  |

|--------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit 4                          | -                                     | not used                                                                                                               |  |  |  |  |  |

| Current S                      | Current Source at I/O Pins            |                                                                                                                        |  |  |  |  |  |

| Bit 5<br>(IBH)                 | · · · · · · · · · · · · · · · · · · · |                                                                                                                        |  |  |  |  |  |

| Test                           |                                       |                                                                                                                        |  |  |  |  |  |

| Bit 6<br>(TSTH)                | 0                                     | Feedback of I/O stages active (OR gated with test pattern) Test pattern activated, feedback of I/O stages switched off |  |  |  |  |  |

| Input/Outp                     | Input/Output Mode                     |                                                                                                                        |  |  |  |  |  |

| Bit 7 0 Input Mode Output Mode |                                       |                                                                                                                        |  |  |  |  |  |

Rev A2, Page 7/12

### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed. Absolute Maximum Ratings are no Operating Conditions. Integrated circuits with system interfaces, e.g. via cable accessible pins (I/O pins, line drivers) are per principle endangered by injected interferences, which may compromise the function or durability. The robustness of the devices has to be verified by the user during system development with regards to applying standards and ensured where necessary by additional protective circuitry. By the manufacturer suggested protective circuitry is for information only and given without responsibility and has to be verified within the actual system with respect to actual interferences.

| Item | Symbol        | Parameter                                                                            | Conditions                           |                     | Fig. |       | •    | Unit |

|------|---------------|--------------------------------------------------------------------------------------|--------------------------------------|---------------------|------|-------|------|------|

|      |               |                                                                                      |                                      |                     |      | Min.  | Max. |      |

| G001 | VCCA<br>VCCD  | Supply Voltage                                                                       |                                      |                     |      | -0.3  | 6    | V    |

| G201 | V(COM)        | Voltage at COM                                                                       |                                      |                     |      | -0.3  | 49   | V    |

| G202 | Vact(IO)      | Voltage at IOx                                                                       | IOx= lo (* see belo                  | w)                  |      | -0.3  | 49   | V    |

| G203 | Idc(COM)      | Current in COM                                                                       |                                      |                     |      | -500  | 0    | mA   |

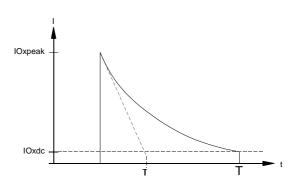

| G204 | lpk(COM)      | Peakcurrent in COM                                                                   | ⊺= 2ms, T≥ 2s                        |                     | 2    | -1000 | -    | mA   |

| G205 | Isc(COM)      | Free-Wheeling Current in COM                                                         |                                      |                     |      | -1.3  |      | Α    |

| G206 | Idc(COM)      | Current in IOx                                                                       |                                      |                     |      | -1    |      | mA   |

| G207 | lpk(IOx)      | Peakcurrent in IOx                                                                   | IOx= Io, T= 2ms, T                   | ≥ 2s                | 2    | -1    | 600  | mA   |

| G208 | lpsc<br>(lox) | Peakcurrent in IOx                                                                   | IOx= lo, Overload                    | current protection  |      | -1.3  |      | А    |

| G301 | V(IOx)        | Voltage at IO03, IO47                                                                | IBL= 0, IBH= 0<br>(current source 20 | 0μΑ)                |      | -0.3  | 49   | V    |

| G302 | V(IOx)        | Voltage at IO03, IO47                                                                | IBL= 1, IBH= 1                       |                     |      | -0.3  | 26   | V    |

|      |               |                                                                                      | (current source 2mA)                 | T= 2ms, T≥ 2s       |      | -0.3  | 49   | V    |

| G401 | lmx<br>(VCCD) | Current in VCCD, GNDD                                                                |                                      |                     |      | -50   | 50   | mA   |

| G402 | Ic()          | Current in Clamping Diodes at<br>CSN, WRN, RDN, A0, A1, D07,<br>RESN, CLK, BLFQ      | D07 set to inputs                    |                     |      | -20   | 20   | mA   |

| G402 | I()           | Current in D07,INTN                                                                  | D07 set to output                    | S                   |      |       | 25   | mA   |

| G404 | llu()         | Peakcurrent in CSN, WRN, RDN, A0, A1, D07, RESN, CLK, BLFQ, INTN (Latch-Up Strength) | pulse duration ≤ 10                  | Dμs                 |      | -100  | 100  | mA   |

| EG1  | Vd()          | ESD Susceptibility, all Inputs and Outputs                                           | HBM 100pF discha                     | arged through 1.5kΩ |      |       | 2    | kV   |

| TG1  | Tj            | Junction Temperature                                                                 |                                      |                     |      | -40   | 150  | °C   |

| TG2  | Ts            | Storage Temperature                                                                  |                                      |                     |      | -40   | 150  | °C   |

<sup>(\*)</sup> IOx= lo : pin set to output, active low,  $x \in 0..7$

### THERMAL DATA

Operating Conditions: VCC= VCCA= VCCD= 5V ±10%

| Item | Symbol | Parameter                           | Conditions                    | Fig. |      |      |      | Unit |

|------|--------|-------------------------------------|-------------------------------|------|------|------|------|------|

|      |        |                                     |                               |      | Min. | Тур. | Max. |      |

| T1   | Та     | Operating Ambient Temperature Range |                               |      | 0    |      | 70   | °C   |

| T2   | . ,    | Thermal Resistance Chip to Ambient  | PLCC44 surface mounted on PCB |      |      | 55   |      | K/W  |

Rev A2, Page 8/12

### **ELECTRICAL CHARACTERISTICS**

| ltem   | Symbol       | Parameter                                            | Conditions                                                             | Tj                   | Fig. |                  |      |                      | Unit           |

|--------|--------------|------------------------------------------------------|------------------------------------------------------------------------|----------------------|------|------------------|------|----------------------|----------------|

|        |              |                                                      |                                                                        | C                    |      | Min.             | Тур. | Max.                 |                |

| Total  | Device       |                                                      |                                                                        |                      |      |                  |      |                      |                |

| 001    | VCCA<br>VCCD | Permissible Supply Voltage Range                     |                                                                        |                      |      | 4.5              |      | 5.5                  | V              |

| 002    | I(VCCA)      | Supply Current in VCCA, power section                | IO07= lo, unloaded                                                     | 0<br>27<br>70<br>125 |      | 5<br>5<br>5<br>5 |      | 65<br>60<br>55<br>55 | mA<br>mA<br>mA |

| 003    | I(VCCD)      | Supply Current in VCCD, digital section              | all logic inputs lo= 0V or hi= VCC                                     |                      |      | 0                |      | 10                   | mA             |

| 004    | I(VCCD)      | Supply Current in VCCD, digital section              | all logic inputs lo= 0.8V                                              |                      |      |                  | 80   |                      | mA             |

| 005    | I(VCCD)      | Supply Current in VCCD, digital section              | all logic inputs lo= 2.0V                                              |                      |      |                  | 100  |                      | mA             |

| Bias,  | Thermal S    | hutdown and Low Voltage Dete                         | ction                                                                  |                      |      |                  |      |                      |                |

| 101    | VCCon        | Turn-on Threshold VCC                                |                                                                        |                      |      | 3.6              | 4    | 4.4                  | V              |

| 102    | VCCoff       | Undervoltage Threshold at VCC                        | decreasing Supply VCC                                                  |                      |      | 3.5              | 3.9  | 4.3                  | V              |

| 103    | VCChys       | Hysteresis                                           | VCChys= VCCon-VCCoff                                                   |                      |      | 40               | 100  | 250                  | mV             |

| 104    | Toff         | Thermal Shutdown Threshold                           |                                                                        |                      |      | 120              | 135  | 150                  | °C             |

| 105    | Thys         | Thermal Shutdown Hysteresis                          | Thys= Toff - Ton                                                       |                      |      | 4                | 8    | 12                   | °C             |

| I/O St | ages: Low    | -side Driver                                         |                                                                        |                      |      |                  |      |                      |                |

| 201    | IIk(COM)     | Leakage Current in COM                               | V(COM)= 25V, V(IOx)= 0V                                                |                      |      |                  |      | 100                  | μΑ             |

| 202    | Vf(COM)      | Forward Voltage of the Free-<br>Wheeling Diodes      | Vf()= V(IOx)-V(COM);<br>I(IOx¬COM)= 100mA,<br>IOx= hi or set to Inputs |                      |      | 0.5              |      | 1.5                  | V              |

| 203    | Vs(IO)       | Saturation Voltage lo at IOx                         | I(IOx)= 10mA, IO07= lo                                                 |                      | 1    |                  |      | 0.4                  | V              |

| 204    | Vs(IO)       | Saturation Voltage lo at IOx                         | I(IOx)= 100mA, IO07= Io                                                |                      | 1    |                  |      | 0.6                  | V              |

| 205    | Vs(IO)       | Saturation Voltage lo at IOx for pulse load          | I(IOx)= 500mA,<br>IO07= Io, ⊺= 2ms, T≥ 2s                              |                      | 1    |                  |      | 1.5                  | V              |

| 206    | loff(IO)     | Threshold Current in IOx for Overcurrent Cut-off     | IOx= Io,<br>V(IOx)= 025V                                               |                      |      | 0.5              |      | 1.3                  | Α              |

| 207    | Ion(IO)      | Free-Wheeling Current I(IOx~COM) for Cut-off release | IOx= Io,<br>V(IOx)= 025V                                               |                      |      | 0.1              |      | 20                   | mA             |

| 208    | f(IO)        | Cut-off Oscillation Frequency                        | depends on Load                                                        |                      |      | 0.1              |      | 20                   | MHz            |

| 209    | lav(IO)      | Mean Current in IOx during Cut-off                   | IOx= Io,<br>V(IOx)= 025V                                               |                      |      | 50               |      | 700                  | mA             |

Rev A2, Page 9/12

### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VCC= VCCA= VCCD= 5V ±10%, Tj= 0..125℃, unless otherwise noted

| ltem   | Symbol       | Parameter                                                                                        | Conditions                                                 | Tj | Fig. |      |      |      | Unit |

|--------|--------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|------|------|------|------|------|

|        |              |                                                                                                  |                                                            | °C |      | Min. | Тур. | Max. |      |

| I/O St | ages: Con    | nparator                                                                                         |                                                            |    |      |      | ,    |      |      |

| 301    | Idwn(IO)     | Pull-down Current in IOx                                                                         | V(IOx)= 348V, IBL= 0,<br>IBH= 0, IO07= hi or set to Inputs |    |      | 120  | 200  | 280  | μΑ   |

| 302    | Idwn(IO)     | Pull-down Current in IOx                                                                         | V(IOx)= 325V, IBL= 1,<br>IBH= 1, IO07= hi or set to Inputs |    |      | 1.4  | 2    | 2.6  | mA   |

| 303    | V0(IO)       | Open-Circuit Voltage at IOx                                                                      | IOx open,<br>IO07= hi or set to Inputs                     |    |      |      |      | 1    | V    |

| 304    | Vt()hi       | Threshold Voltage hi at IOx                                                                      |                                                            |    |      |      |      | 4.6  | V    |

| 305    | Vt()lo       | Threshold Voltage lo at IOx                                                                      |                                                            |    |      | 3    |      |      | V    |

| μP-In  | terface, I/C | D-Logic, Frequency Divider, Interr                                                               | upt                                                        |    |      |      |      |      |      |

| 401    | IIk(Dx)      | Leakage Current in Dx                                                                            | D07 set to Inputs                                          |    |      | -5   |      | 5    | μΑ   |

| 402    | llk(Dx)      | Leakage Current in Schmitt<br>Trigger Inputs CSN, WRN, RDN,<br>A0, A1, RESN, CLK, BLFQ           |                                                            |    |      | -1   |      | 1    | μΑ   |

| 403    | Vt()hi       | Threshold Voltage hi at Schmitt<br>Trigger Inputs CSN, WRN, RDN,<br>A0, A1, RESN, CLK, BLFQ, D07 | D07 set to Inputs                                          |    |      |      |      | 2.3  | V    |

| 404    | Vt()lo       | Threshold Voltage Io at Schmitt<br>Trigger Inputs CSN, WRN, RDN,<br>A0, A1, RESN, CLK, BLFQ, D07 | D07 set to Inputs                                          |    |      | 0.7  |      |      | V    |

| 405    | Vt()hys      | Hysteresis at Schmitt Trigger<br>Inputs CSN, WRN, RDN, A0, A1,<br>RESN, CLK, BLFQ, D07           | Vt()hys= Vt()hi-Vt()lo;<br>D07 set to Inputs               |    |      | 0.3  |      |      | V    |

| 406    | Vs()hi       | Saturation Voltage hi at INTN                                                                    | Vs()hi= VCCD-V(INTN);<br>INTN=hi, I(INTN)= -100μA          |    |      |      |      | 0.2  | V    |

| 407    | Vs()hi       | Saturation Voltage hi at INTN                                                                    | Vs()hi= VCCD-V(INTN);<br>INTN=hi, I(INTN)= -2mA            |    |      |      |      | 0.8  | V    |

| 408    | Vs()lo       | Saturation Voltage lo at INTN                                                                    | INTN= lo, l(INTN)= 100µA                                   |    |      |      |      | 0.2  | V    |

| 409    | Vs()lo       | Saturation Voltage lo at INTN                                                                    | INTN= Io, I(INTN)= 2mA                                     |    |      |      |      | 0.49 | V    |

| 410    | Vs(Dx)hi     | Saturation Voltage hi at Dx                                                                      | Vs(Dx)hi= VCCD-V(Dx);<br>Dx= hi, I(Dx)= -100μA             |    |      |      |      | 0.2  | V    |

| 411    | Vs(Dx)hi     | Saturation Voltage hi at Dx                                                                      | Vs(Dx)hi= VCCD-V(Dx);<br>Dx= hi, I(Dx)= -4mA               |    |      |      |      | 0.8  | V    |

| 412    | Vs(Dx)lo     | Saturation Voltage lo at Dx                                                                      | Dx= Io, I(Dx)= 100μA                                       |    |      |      |      | 0.2  | V    |

| 413    | Vs(Dx)lo     | Saturation Voltage lo at Dx                                                                      | Dx= lo, I(Dx)= 4mA                                         |    |      |      |      | 0.49 | V    |

| 414    | Vc()hi       | Clamp Voltage hi at<br>CSN, WRN, RDN, A0, A1, RESN,<br>CLK,BLFQ, D07, INTN, CERR                 | Vc()hi= V()-VCC,<br>I()= 20mA                              |    |      | 0.4  |      | 2.5  | V    |

| 415    | Vc()lo       | Clamp Voltage Io at<br>CSN, WRN, RDN, A0, A1, RESN,<br>CLK, BLFQ, D07, INTN, CERR                | I()= -20mA                                                 |    |      | -1.8 |      | -0.4 | V    |

Rev A2, Page 10/12

### **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VCC= VCCA= VCCD= 5V ±10%, Tj= 0..125℃, unless otherwise noted

| Item  | Symbol             | Parameter                                             | Conditions                 | Tj              | Fig. |      |      |      | Unit |

|-------|--------------------|-------------------------------------------------------|----------------------------|-----------------|------|------|------|------|------|

|       |                    |                                                       |                            | ${\mathfrak C}$ |      | Min. | Тур. | Max. |      |

| Switc | hing Char          | acteristics                                           |                            |                 |      |      |      |      |      |

| 501   | tc(CLK)            | Permissible Cycle Duration CLK                        |                            |                 |      | 400  |      |      | ns   |

| 502   | tw(CLK)            | Permissible Pulse Width lo at CLK                     |                            |                 |      | 200  |      |      | ns   |

| 503   | tc(BLFQ)           | Permissible Cycle Duration BLFQ                       |                            |                 |      | 100  |      |      | ms   |

| 504   | tw(BLFQ)           | Permissible Pulse Width lo at BLFQ                    |                            |                 |      | 50   |      |      | ms   |

| 505   | tphl()             | Propagation Delay until IOx= lo                       | Write Cycle, WRN: hi→lo    |                 |      |      |      | 2    | μs   |

| 506   | tplh()             | Propagation Delay until IOx= off                      | Write Cycle, WRN: hi→lo    |                 |      |      |      | 3    | μs   |

| 507   | tp()Ion            | Current Source Enable Time at IOx                     | Write Cycle,<br>WRN: hi→lo |                 |      |      |      | 5    | μs   |

| 508   | tp()loff           | Current Source Disable Time at IOx                    | Write Cycle,<br>WRN: hi→lo |                 |      |      |      | 5    | μs   |

| 509   | tp(IOx→<br>up/dwn) | Propagation Delay Input<br>IOx to Up/Dwn Filter Input |                            |                 |      |      |      | 5    | μs   |

### **ELECTRICAL CHARACTERISTICS: WAVEFORMS**

Figure 1: DC load Figure 2: Pulse load, Pulse duration 2 ms

Rev A2, Page 11/12

### OPERATING REQUIREMENTS: µP INTERFACE

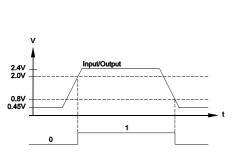

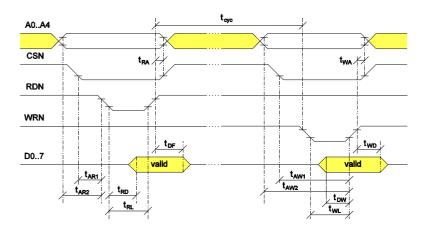

Operating Conditions: VCC= VCCA= VCCD=  $5V \pm 10\%$ , Ta=  $0..70^{\circ}$ C, CL()= 150pF, input levels lo= 0..0.45V, hi= 2.4V..VCC, see Fig. 3 for reference levels and waveforms

| Item | Symbol    | Parameter                                                 | Conditions | Fig. |      |      | Unit |

|------|-----------|-----------------------------------------------------------|------------|------|------|------|------|

|      |           |                                                           |            |      | Min. | Max. |      |

| Data | Word Rea  | d Timing                                                  |            |      |      |      |      |

| l1   | tar       | Setup Time:<br>CSN, A0, A1 set before RDN hi-lo           |            | 4    | 30   |      | ns   |

| 12   | tRA       | Hold Time:<br>CSN, A0, A1 stable after RDN lo⊸hi          |            | 4    | 10   |      | ns   |

| 13   | tRD       | Read Data Access Time:<br>Data valid after RDN hi→lo      |            | 4    |      | 120  | ns   |

| 14   | tDF       | Read Data Hold Time: Ports high impedance after RDN lo⊸hi |            | 4    |      | 65   | ns   |

| 15   | tRW       | Recovery Time between Read/Write Cycles                   |            | 4    | 165  |      | ns   |

| Data | Word Writ | te Timing                                                 |            |      |      |      |      |

| 16   | taw       | Setup Time:<br>CSN, A0, A1 set before WRN hi→lo           |            | 4    | 30   |      | ns   |

| 17   | tDW       | Write Data Setup Time:<br>Data valid before WRN lo-hi     |            | 4    | 100  |      | ns   |

| 18   | twa       | Hold Time:<br>CSN, A0, A1 stable after WRN lo→hi          |            | 4    | 10   |      | ns   |

| 19   | twD       | Write Data Hold Time:<br>Data valid after WRN lo-hi       |            | 4    | 10   |      | ns   |

Figure 3: Reference levels

Figure 4: Data word read/write timing

iC-Haus expressly reserves the right to change its products and/or specifications. An info letter gives details as to any amendments and additions made to the relevant current specifications on our internet website <a href="https://www.ichaus.com/infoletter">www.ichaus.com/infoletter</a>; this letter is generated automatically and shall be sent to registered users by email. Copying – even as an excerpt – is only permitted with iC-Haus approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification on this site and does not assume liability for any errors or omissions in the materials. The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

As a general rule our developments, IPs, principle circuitry and range of Integrated Circuits are suitable and specifically designed for appropriate use in technical applications, such as in devices, systems and any kind of technical equipment, in so far as they do not infringe existing patent rights. In principle the range of use is limitless in a technical sense and refers to the products listed in the inventory of goods compiled for the 2008 and following export trade statistics issued annually by the Bureau of Statistics in Wiesbaden, for example, or to any product in the product catalogue published for the 2007 and following exhibitions in Hanover (Hannover-Messe).

We understand suitable application of our published designs to be state-of-the-art technology which can no longer be classed as inventive under the stipulations of patent law. Our explicit application notes are to be treated only as mere examples of the many possible and extremely advantageous uses our products can be put to.

Rev A2, Page 12/12

### **ORDERING INFORMATION**

| Туре   | Package | Order designation |

|--------|---------|-------------------|

| iC-VRV | PLCC44  | iC-VRV PLCC44     |

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Tel +49 (6135) 9292-0

Am Kuemmerling 18 Fax +49 (6135) 9292-192

D-55294 Bodenheim Web: http://www.ichaus.com

GERMANY E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.de/support\_distributors.php