### iC-PN2612

### PHASED ARRAY NONIUS ENCODER

Rev C1, Page 1/9

#### **FEATURES**

- Compact, 3-channel optical nonius encoder with differential scanning and analog sine/cosine outputs: 511 CPR (N), 512 CPR (M), 496 CPR (S), size Ø 26 mm

- ♦ Phased-array design for excellent signal matching

- ♦ Reduced cross talk due to moderate track pitch

- ♦ Ultra low dark currents for operation up to high temperature

- ♦ Low noise amplifiers with high transimpedance gain

- ♦ Short-circuit-proof, low impedance voltage outputs for enhanced EMI tolerance

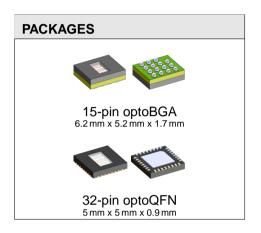

- Space saving optoQFN and optoBGA packages (RoHS compliant)

- ♦ Low power consumption from single 4.1 to 5.5 V supply

- ♦ Operational temperature range of -40 to +110 °C

- ♦ Suitable code disc: LSHC11S 26-512N (glass 1 mm) OD Ø 26 mm, ID Ø 11.6 mm, optical radius 10.905 mm

#### **APPLICATIONS**

♦ Absolute position encoders

### iC-PN2612

### PHASED ARRAY NONIUS ENCODER

Rev C1, Page 2/9

#### **DESCRIPTION**

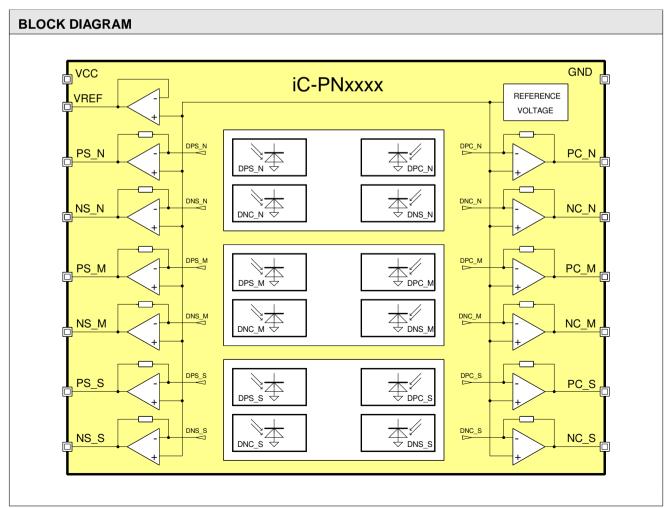

The optical encoder iC-PN2612 features monolithically integrated photosensors arranged as a phased-array.

The transimpedance gain of typically 1  $M\Omega$  generates output signals of a few hundred millivolts already from an illumination level of 3 mW/cm<sup>2</sup>. In most cases no additional measures must be considered to filter for noise and interferences.

Analog nonius encoders are the typical application for iC-PN2612. Its 3-track scanning features a phased-array of multiple photosensors each per track, generating positive and negative going sine signals, as well as positive and negative going cosine signals. An excellent matching and common mode behavior of the differential signal paths is obtained by a paired amplifier design, reducing the needs for external signal calibration to an absolute minimum.

**HD Phased Arrays** are designed for fidelity and robustness. Ultra-low signal distortion is obtained at increased tolerances for alignment and random code defects (e.g. due to dust).

For information on chip releases, refer to chapter Design Review.

#### PACKAGING INFORMATION INFORMATION

### PAD LAYOUT Chip release Z (2.88 mm x 3.37 mm)

### PAD FUNCTIONS No. Name Function

Refer to the description of pin functions.

Grey sections represent sensor layout areas; fill factors vary.

PAD LAYOUT Chip release Y1 (2.88 mm x 3.37 mm), HD Phased Array

PAD FUNCTIONS

No. Name Function

Rev C1, Page 3/9

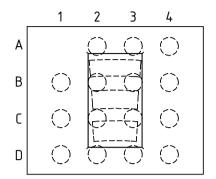

### PIN CONFIGURATION oBGA LSH2C (6.2 mm x 5.2 mm)

### PIN FUNCTIONS

#### No. Name Function

A2 VCC +4.1..5.5 V Supply Voltage A3 VREF Reference Voltage Output

A4 GND Ground

B1 PS N N-Track Sine +

B2 NS\_N N-Track Sine -

B3 NC\_N N-Track Cosine -

B4 PC\_N N-Track Cosine +

C1 PS\_M M-Track Sine +

C2 NS M M-Track Sine -

C3 NC M M-Track Cosine -

C4 PC\_M M-Track Cosine +

D1 PS S S-Track Sine +

D2 NS\_S S-Track Sine -

D3 NC\_S S-Track Cosine -

D4 PC\_S S-Track Cosine +

Note: All signal outputs are analog voltage outputs.

For dimensional specifications refer to the relevant package data sheet, available separately.

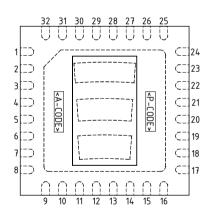

### PIN CONFIGURATION oQFN32-5x5 (5 mm x 5 mm)

#### **PIN FUNCTIONS**

#### No. Name Function

1 VCC +4.1..5.5 V Supply Voltage

2 VREF Reference Voltage Output

3 PS N N-Track Sine +

4 NS N N-Track Sine -

5 PS\_M M-Track Sine +

6 NS\_M M-Track Sine -

7 PS S S-Track Sine +

8 NS\_S S-Track Sine -

9..16 n.c.<sup>1)</sup>

17 NC\_S S-Track Cosine -

18 PC\_S S-Track Cosine +

19 NC\_M M-Track Cosine -

20 PC\_M M-Track Cosine +

21 NC\_N N-Track Cosine - 22 PC N N-Track Cosine +

24 GND Ground

25..32 n.c.1)

BP Backside paddle 2)

Note: All signal outputs are analog voltage outputs.

IC top marking: <P-CODE> = product code, <A-CODE> = assembly code (subject to changes);

<sup>1)</sup> Pin numbers marked n.c. are not connected.

<sup>2)</sup> Connecting the backside paddle is recommended by a single link to GND. A current flow across the paddle is not permissible.

Rev C1, Page 4/9

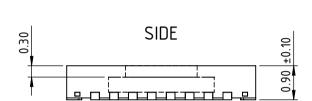

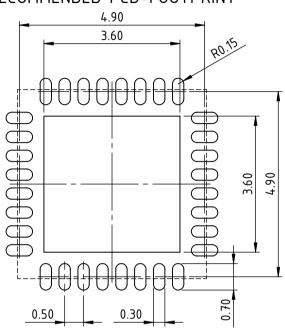

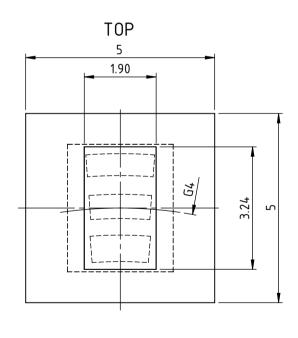

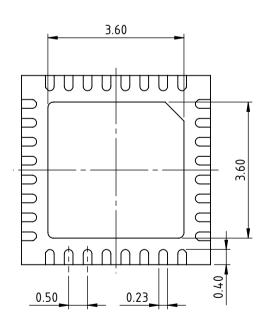

### **PACKAGE DIMENSIONS oQFN32-5x5**

### RECOMMENDED PCB-FOOTPRINT

**BOTTOM**

All dimensions given in mm. Tolerances of form and position according to JEDEC M0–220. Positional tolerance of sensor pattern:  $\pm70\mu m$  /  $\pm1^{\circ}$  (with respect to backside pad). G4: radius of chip center (refer to the relevant encoder disc and code description). Maximum molding excess  $+20\mu m$  /  $-75\mu m$  versus surface of glass/reticle.

drb\_pnxx-oqfn32-2\_pack\_1, 10:1

Rev C1, Page 5/9

### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| Item | Symbol | Parameter                       | Conditions                            |      |       | Unit |

|------|--------|---------------------------------|---------------------------------------|------|-------|------|

| No.  |        |                                 |                                       | Min. | Max.  |      |

| G001 | VCC    | Voltage at VCC                  |                                       | -0.3 | 6     | V    |

| G002 | I(VCC) | Current in VCC                  |                                       | -20  | 20    | mA   |

| G003 | V()    | Pin Voltage, all signal outputs |                                       | -0.3 | VCC + | V    |

|      |        |                                 |                                       |      | 0.3   |      |

| G004 | I()    | Pin Current, all signal outputs |                                       | -20  | 20    | mA   |

| G005 | Vd()   | ESD Susceptibility, all pins    | HBM, 100 pF discharged through 1.5 kΩ |      | 2     | kV   |

| G006 | Tj     | Junction Temperature            |                                       | -40  | 150   | °C   |

| G007 | Ts     | Chip Storage Temperature        |                                       | -40  | 150   | °C   |

### THERMAL DATA

Operating conditions: VCC = 4.1...5.5 V

| Item | Symbol | Parameter                           | Conditions                                                                                                          |            |      |            | Unit     |

|------|--------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------|------|------------|----------|

| No.  |        |                                     |                                                                                                                     | Min.       | Тур. | Max.       |          |

| T01  | Та     | Operating Ambient Temperature Range | package oQFN32-5x5<br>package oBGA LSH2C                                                                            | -40<br>-40 |      | 110<br>110 | °C<br>°C |

|      |        |                                     | (extended temperature range on request)                                                                             |            |      |            |          |

| T02  | Ts     | Storage Temperature Range           | package oQFN32-5x5<br>package oBGA LSH2C                                                                            | -40        |      | 110        | °C       |

| T03  | Tpk    | Soldering Peak Temperature          | package oQFN32-5x5                                                                                                  |            |      |            |          |

|      |        |                                     | tpk < 20 s, convection reflow<br>tpk < 20 s, vapor phase soldering                                                  |            |      | 245<br>230 | °C<br>°C |

|      |        |                                     | MSL 5A (max. floor live 24 h at 30 °C and 60 % RH);<br>Please refer to customer information file No. 7 for details. |            |      |            |          |

| T04  | Tpk    | Soldering Peak Temperature          | package oBGA LSH2C                                                                                                  |            |      |            |          |

|      |        |                                     | tpk < 20 s, convection reflow<br>tpk < 20 s, vapor phase soldering                                                  |            |      | 245<br>230 | °C<br>°C |

|      |        |                                     | TOL (time on label) 8 h;<br>Please refer to customer information file No. 7<br>for details.                         |            |      |            |          |

Rev C1, Page 6/9

### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VCC = 4.1...5.5 V, Tj = -40..125 °C, unless otherwise stated

| ltem<br>No. | Symbol       | Parameter                                                | Conditions                                                                                               | Min.         | Тур.         | Max.         | Unit                   |

|-------------|--------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------------------------|

| Total       | Device       |                                                          |                                                                                                          |              |              |              |                        |

| 001         | VCC          | Permissible Supply Voltage                               |                                                                                                          | 4.1          |              | 5.5          | V                      |

| 002         | I(VCC)       | Supply Current in VCC                                    | no load, photocurrents within linear op. range (no override)                                             |              | 9.5          | 15           | mA                     |

| 003         | Vc()hi       | Clamp-Voltage hi at all pins                             | I() = 4  mA                                                                                              |              |              | 11           | V                      |

| 004         | Vc()lo       | Clamp-Voltage lo at all pins                             | I() = -4  mA                                                                                             | -1.2         |              | -0.3         | V                      |

| Photo       | sensors      |                                                          |                                                                                                          |              |              |              |                        |

| 101         | $\lambda$ ar | Spectral Application Range                               | $Se(\lambda ar) = 0.25 \times S(\lambda pk)$                                                             | 400          |              | 950          | nm                     |

| 102         | $\lambda$ pk | Peak Sensitivity Wavelength                              |                                                                                                          |              | 680          |              | nm                     |

| 103         | Aph()        | Radiant Sensitive Area                                   | chip release PN2612_Z<br>chip release PN2612_Y1                                                          |              | 0.08<br>0.13 |              | mm²<br>mm²             |

| 104         | $S(\lambda)$ | Spectral Sensitivity                                     | $\begin{split} \lambda_{\text{LED}} &= 740\text{nm} \\ \lambda_{\text{LED}} &= 850\text{nm} \end{split}$ |              | 0.5<br>0.3   |              | A/W<br>A/W             |

| 106         | E()mxr       | Irradiance For Maximum Signal<br>Level                   | $\lambda_{\text{LED}}$ = 740 nm, Vout() not saturated; chip release PN2612_Z                             |              | 9.3          |              | mW/<br>cm <sup>2</sup> |

|             |              |                                                          | chip release PN2612_Y1                                                                                   |              | 4.4          |              | mW/<br>cm <sup>2</sup> |

| Photo       | current Am   | plifiers                                                 |                                                                                                          |              |              |              |                        |

| 201         | lph()        | Permissible Photocurrent Operating Range                 |                                                                                                          | 0            |              | 1120         | nA                     |

| 202         | η()r         | Photo Sensitivity<br>(light-to-voltage conversion ratio) | λ <sub>LED</sub> = 740 nm;<br>chip release PN2612_Z<br>chip release PN2612_Y1                            | 0.2          | 0.27<br>0.3  | 0.5          | V/µW<br>V/µW           |

| 203         | Z()          | Equivalent Transimpedance Gain                           | Z = Vout() / Iph()                                                                                       | 0.7          | 1.0          | 1.4          | ΜΩ                     |

| 204         | TCz          | Temperature Coefficient of Transimpedance Gain           |                                                                                                          |              | -0.12        |              | %/°C                   |

| 209         | ΔZ()pn       | Transimpedance Gain Matching                             | P channel vs. corresponding N channel                                                                    | -0.2         |              | 0.2          | %                      |

| 210         | △Vout()pn    | Signal Matching                                          | no illumination, any output vs. any output                                                               | -35          |              | 35           | mV                     |

| 211         | △Vout()pn    | Signal Matching                                          | no illumination, P output vs. corresponding N output                                                     | -2.5         |              | 2.5          | mV                     |

| 212         | fc()hi       | Cut-off Frequency (-3 dB)                                |                                                                                                          |              | 400          |              | kHz                    |

| 213         | VNoise()     | RMS Output Noise                                         | illuminated to 500 mV signal level above dark level, 500 kHz band width                                  |              | 0.5          |              | mV                     |

| Signa       | l Outputs    |                                                          |                                                                                                          |              |              |              |                        |

| 301         | Vout()mx     | Permissible Maximum Output<br>Voltage                    | illumination to E()mxr, linear gain;<br>VCC = 4.55.5 V<br>VCC = 4.1 V                                    | 2.45<br>2.05 | 2.72<br>2.3  | 3.02<br>2.6  | V                      |

| 302         | Vout()d      | Dark Signal Level                                        | no illumination, load 20 kΩ vs. +2 V                                                                     | 575          | 770          | 1000         | mV                     |

| 303         | Vout()acmx   | Maximum Signal Level                                     | Vout()acmx = Vout()mx - Vout()d;<br>VCC = 4.55.5 V<br>VCC = 4.1 V                                        | 1.48<br>1.18 | 1.96         | 2.35<br>2.35 | V                      |

| 304         | lsc()hi      | Short-Circuit Current hi                                 | load current to ground                                                                                   | 100          | 420          | 1000         | μA                     |

| 305         | lsc()lo      | Short-Circuit Current lo                                 | load current to IC                                                                                       | 250          | 480          | 700          | μA                     |

| 306         | Ri()         | Internal Output Resistance                               | f= 1 kHz                                                                                                 | 70           | 110          | 180          | Ω                      |

| 307         | ton()        | Power-On Settling Time                                   | $VCC = 0 V \rightarrow 5 V$                                                                              |              |              | 100          | μs                     |

| Refer       | ence Voltage | VREF                                                     |                                                                                                          |              |              |              |                        |

| 401         | VREF         | Reference Voltage                                        | I(VREF) = -100+300 μA                                                                                    | 575          | 770          | 1000         | mV                     |

| 402         | dVout()      | Load Balancing                                           | I(VREF) = -100+300 μA                                                                                    | -10          |              | +10          | mV                     |

| 403         | lsc()hi      | Short-Circuit Current hi                                 | load current to ground                                                                                   | 200          | 420          | 1400         | μA                     |

| 404         | lsc()lo      | Short-Circuit Current lo                                 | load current to IC                                                                                       | 0.5          | 4.5          | 10           | mA                     |

Rev C1, Page 7/9

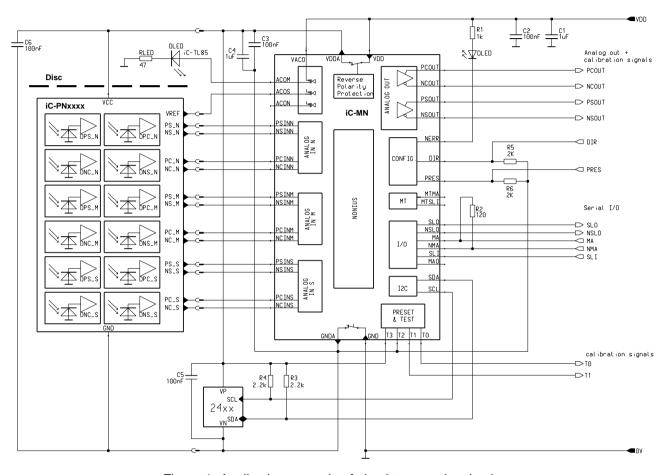

### **APPLICATION CIRCUITS**

Figure 1: Application example of absolute encoder circuit.

Rev C1, Page 8/9

### **DESIGN REVIEW: Notes On Chip Functions**

| iC-PN2612 2 | iC-PN2612 Z              |                                                                                                                                                                                                      |  |  |  |  |

|-------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.         | Function, Parameter/Code | Description and Application Hints                                                                                                                                                                    |  |  |  |  |

| 1           |                          | None at time of printing (datasheet release B2, 2011). Changes to Elec. Char. are documented by this datasheet release, including the extension of operating voltage down to 4.1 V (safe by design). |  |  |  |  |

Table 4: Notes on chip functions regarding iC-PN2612 chip release Z

| iC-PN2612 Y1 |                                                                |                                                                                                                                      |  |  |  |

|--------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No.          | No. Function, Parameter/Code Description and Application Hints |                                                                                                                                      |  |  |  |

| 1            | HD Phased Array                                                | Chip release utilizes a high density phased array layout.  Improvement of alignment marks: enlarged radial size, inner ring omitted. |  |  |  |

Table 5: Notes on chip functions regarding iC-PN2612 chip release Y1.

### **REVISION HISTORY**

| Rel | Rel.Date | Chapter | Modification | Page |

|-----|----------|---------|--------------|------|

| B2  | 11-07-14 |         |              |      |

| Rel | Rel.Date                                                                                                                                                                                                                                                                                                                         | Chapter                                | Modification                                                                                                      | Page |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|

| C1  | 14-09-05                                                                                                                                                                                                                                                                                                                         | FEATURES                               | Supply voltage extended to include 4.1 V                                                                          | 1    |

|     |                                                                                                                                                                                                                                                                                                                                  | DESCRIPTION                            | Description of HD Phased Array supplemented                                                                       | 2    |

|     |                                                                                                                                                                                                                                                                                                                                  | PACKAGING INFORMATION                  | Chip release Y1 supplemented, oQFN package drawings updated for top marking and tolerances                        | 2, 3 |

|     |                                                                                                                                                                                                                                                                                                                                  | THERMAL DATA                           | Package qualification pending removed                                                                             | 3    |

|     | ELECTRICAL CHARACTERISTICS Operating conditions: VCC supply voltage extended to include 4.1 Item 001: min. limit; item 101, condition: reference is λpk; Items 103, 106, 202: update of values for Z and Y1 chip releases Items 301, 303: conditions and limits for 4.1 V; Item 302, 401: min. limit; item 304, 403: max. limit; |                                        | Items 103, 106, 202: update of values for Z and Y1 chip releases Items 301, 303: conditions and limits for 4.1 V; | 6    |

|     |                                                                                                                                                                                                                                                                                                                                  | APPLICATION CIRCUITS                   | CIRCUITS Application example corrected                                                                            |      |

|     |                                                                                                                                                                                                                                                                                                                                  | DESIGN REVIEW: Notes On Chip Functions | Chapter supplemented                                                                                              | 8    |

|     |                                                                                                                                                                                                                                                                                                                                  | ORDERING INFORMATION                   | TION Update of P/O codes and items                                                                                |      |

iC-Haus expressly reserves the right to change its products and/or specifications. An info letter gives details as to any amendments and additions made to the relevant current specifications on our internet website www.ichaus.de/infoletter; this letter is generated automatically and shall be sent to registered users by email.

Copying - even as an excerpt - is only permitted with iC-Haus' approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification and does not assume liability for any errors or omissions in these materials.

The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

iC-Haus products are not designed for and must not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (Safety-Critical Applications) without iC-Haus' specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems. iC-Haus products are not designed nor intended for use in military or aerospace applications or environments or in automotive applications unless specifically designated for such use by iC-Haus.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

Rev C1, Page 9/9

### **ORDERING INFORMATION**

| Туре           | Package                                                                  | Options                                                                                  | Order Designation    |

|----------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------|

| iC-PN2612      | 32-pin optoQFN,<br>5 mm x 5 mm,<br>thickness 0.9 mm<br>RoHS compliant    |                                                                                          | iC-PN2612 oQFN32-5x5 |

|                | 15-pin optoBGA,<br>6.2 mm x 5.2 mm<br>thickness 1.7 mm<br>RoHS compliant |                                                                                          | iC-PN2612 oBGA LSH2C |

| Evaluation Kit | PCB (60 mm x 40 mm), assembled with optoQFN                              | with LED and code disc                                                                   | iC-PN2612 EVAL PNH1M |

|                | PCB (60 mm x 40 mm), assembled with optoBGA                              | with LED and code disc                                                                   | iC-PN2612 EVAL LSH2M |

| Code Disc      |                                                                          | 511/512/496 PPR<br>OD Ø 26 mm, ID Ø 11.6 mm,<br>optical radius 10.905 mm<br>(glass 1 mm) | LSHC11S 26-512N      |

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Tel.: +49 (0) 61 35 - 92 92 - 0

Am Kuemmerling 18 Fax: +49 (0) 61 35 - 92 92 - 192

D-55294 Bodenheim Web: http://www.ichaus.com

GERMANY E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.com/sales\_partners