## iC-HT

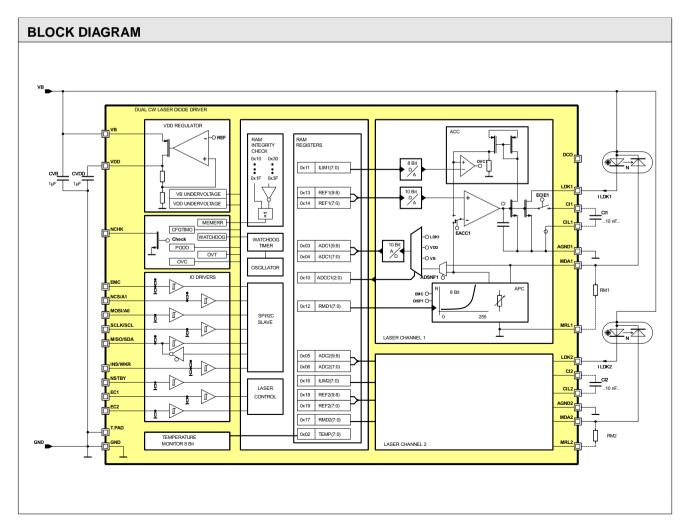

### **DUAL CW LASER DIODE DRIVER**

Rev B1, Page 1/45

#### **FEATURES**

- ♦ Dual channel CW operation with up to 750 mA per channel

- ♦ Up to 1500 mA with both channels combined

- ♦ 2.8 V to 11 V power supply

- ♦ Operation with or without µController

- ♦ Individual enable input per channel

- ♦ Control loop accuracy better than 1%

- ♦ Internal programmable logarithmic monitor resistor

- ♦ Operating point setup with 10 bit logarithmic resolution

- ♦ ACC or APC mode individually configurable for each channel

- ♦ A/D converters for analog monitoring

- ♦ Serial programming interface (SPI or I<sup>2</sup>C compliant)

- ♦ Configuration content verification and validation

- ♦ Programmable laser overcurrent protection

- ♦ Optimized for N-type laser diodes

- ♦ Low drop linear regulator for 3.3 V

- ♦ Low current standby mode

- ♦ Temperature monitor

- ♦ Temperature range -40 ... 85 °C

#### **APPLICATIONS**

- ♦ Laser diode and LED modules

- ♦ CW N-/M-type laser diode drivers

- ◆ Embedded laser diode controllers

- Structured-light 3D illuminations

- Multiple laser diode control

- ♦ Optical amplification/pumping

- ♦ Safety related laser controllers

#### **PACKAGES**

QFN28 5 mm x 5 mm

Copyright © 2015 iC-Haus http://www.ichaus.com

Rev B1, Page 2/45

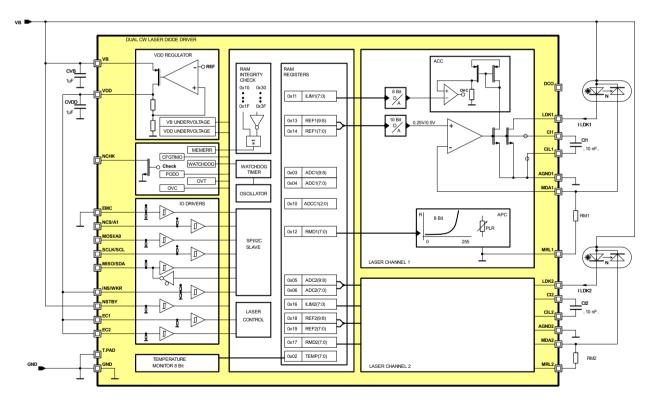

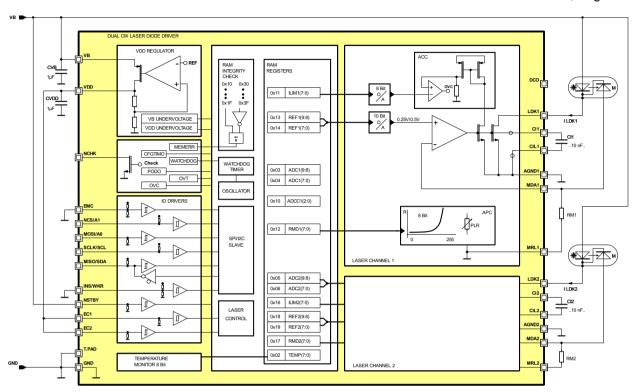

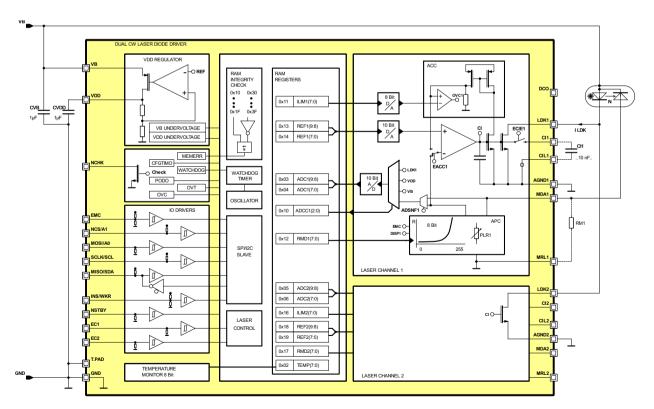

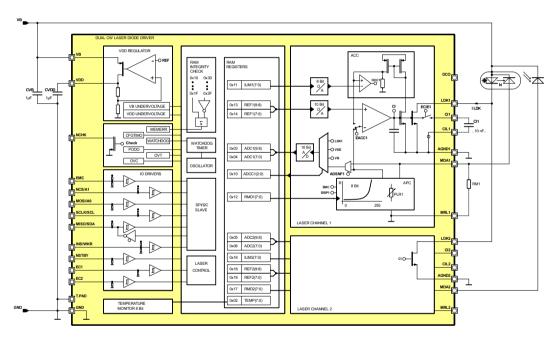

#### **DESCRIPTION**

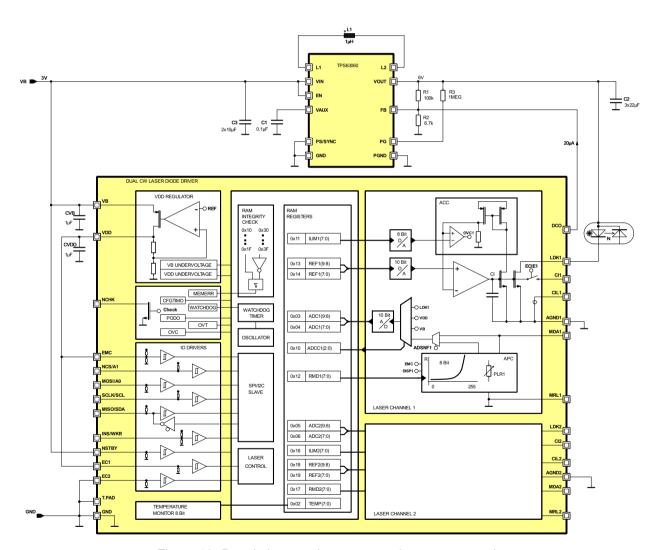

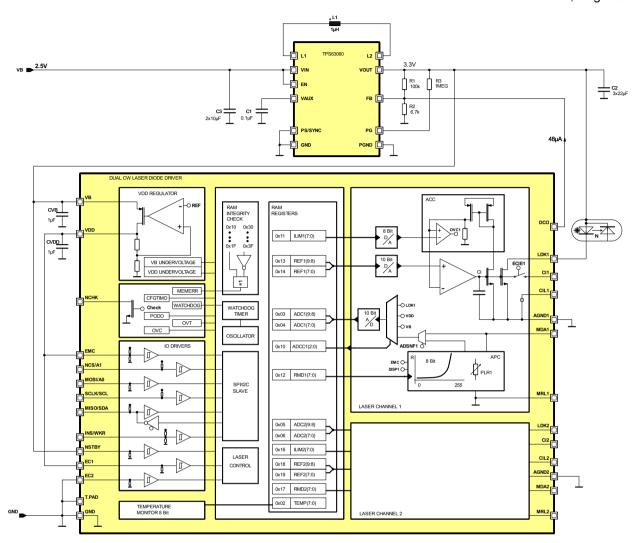

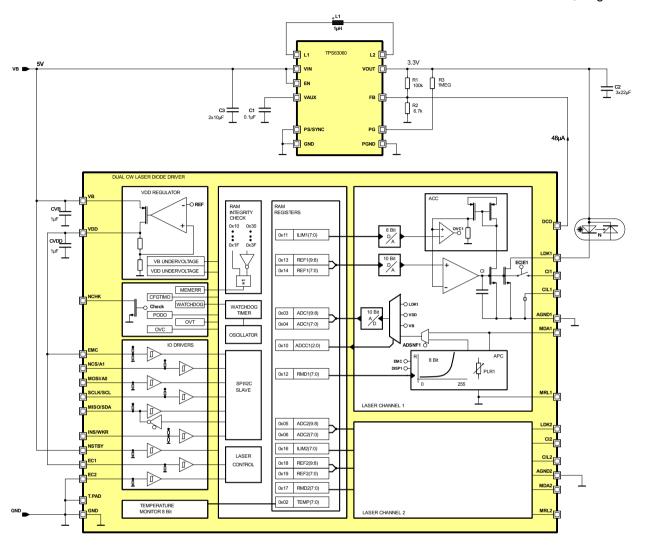

Dual CW laser diode driver iC-HT can operate two individual laser diodes with up to 750 mA laser current depending on the heat dissipation. Each channel can be enabled independently. The laser diode driver can be controlled by an external microcontroller (MCU mode) or operate stand alone with pin/resistor configuration (iC-WK mode). In MCU mode, both channels can be combined for driving up to 1500 mA.

Each channel can be operated individually either in automatic current control (ACC) or automatic power control (APC). All parameters including the internal reference voltages are set via serial communication (I<sup>2</sup>C or SPI). A 10 bit resolution D/A converter with logarithmic characteristic is used for setting the operating point. This allows an operating point resolution better than 1%.

In APC control, the monitor diode photocurrent is used to track the optically emitted power of the laser diode. The feedback for the laser diode driver is the voltage of the photocurrent at a monitor resistor. An 8 bit internal programmable logarithmic monitor resistor (PLR) or an external monitor resistor can be selected for closing the control loop. The PLR ranges from  $100\,\Omega$  to  $500\,\mathrm{k}\Omega$  with a step width less than 5%.

In ACC control, the laser diode current can be set directly. Two current ranges are selectable.

iC-HT allows disabling the laser channels when an overcurrent threshold has been exceeded. The over-

current threshold of each channel has 2 ranges and is programmable through an 8 bit linear D/A converter.

The temperature monitor measures the internal chip temperature. iC-HT disables the laser channels when overtemperature is detected.

A variety of voltages can be measured with a 10 bit A/D converter. The following voltages can be measured:

- V(LDKx)

- V(VDD)

- V(VB)

- V(MDAx)

- V(PLRx)

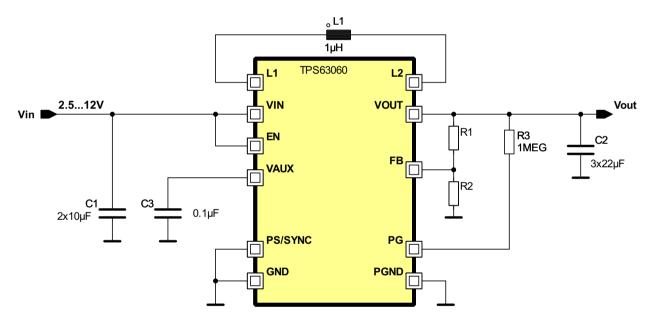

The DCO current output pin can control an external DC/DC converter. Controlling the DC/DC output voltage can optimize the power dissipation of the whole system e.g. to extend battery life.

iC-HT in standby mode has a very low current consumption ( $< 10 \,\mu\text{A}$ ) and does retain its configuration.

The device features for **safe operation**:

- · Configuration verification

- Tri-state configuration pins

- Write protection in operating mode

- · Safe default/startup state

Rev B1, Page 3/45

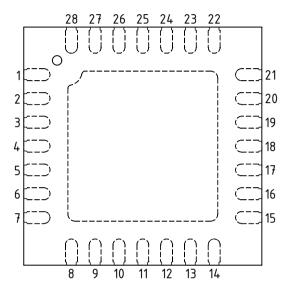

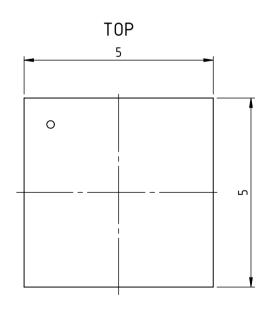

#### PACKAGING INFORMATION QFN28 5 mm x 5 mm to JEDEC

## PIN CONFIGURATION QFN28 5 mm x 5 mm (topview)

#### **PIN FUNCTIONS**

|     | Name     | Function                                         |

|-----|----------|--------------------------------------------------|

| NO. |          |                                                  |

| 1   | LDK1     | Laser Diode Cathode for channel 1                |

|     | LDK1     | Laser Diode Cathode for channel 1                |

|     | AGND1    | Analog Ground for channel 1                      |

|     | CI1      | Integration Capacitor for channel 1              |

| 5   | CIL1     | Integration Capacitor for channel 1,             |

|     |          | low side                                         |

|     | MDA1     | Monitor Diode Anode for channel 1                |

| 7   | MRL1     | Monitor Resistor for channel 1, low              |

|     |          | side                                             |

|     | EMC      | Enable Microcontroller input                     |

|     | SCLK/SCL |                                                  |

|     | MISO/SDA |                                                  |

| 11  | MOSI/A0  | SPI Master Out Slave In / I <sup>2</sup> C Ad-   |

|     |          | dress Bit 0                                      |

| 12  | NCS/A1   | Chip Select, active low / I <sup>2</sup> C Ad-   |

|     |          | dress bit 1                                      |

|     | EC1      | Enable Channel 1 input                           |

|     | EC2      | Enable Channel 2 input                           |

| 15  | MRL2     | Monitor Resistor for channel 2, low              |

|     |          | side                                             |

|     | MDA2     | Monitor Diode Anode for channel 2                |

| 17  | CIL2     | Integration Capacitor for channel 2,             |

|     |          | low side                                         |

|     | CI2      | Integration Capacitor for channel 2              |

|     | AGND2    | Analog Ground for channel 2                      |

|     | LDK2     | Laser Diode Cathode for channel 2                |

|     | LDK2     | Laser Diode Cathode for channel 2                |

|     | GND      | Ground                                           |

|     | DCO      | Digital Current Output                           |

| 24  | INS/WKR  | I <sup>2</sup> C or SPI selection input / Refer- |

|     |          | ence voltage selection in iC-WK                  |

| 0.5 | \        | mode                                             |

|     | VDD      | 3.3 V output supply                              |

|     | VB       | Power supply                                     |

|     | NCHK     | Error output, active low                         |

|     | NSTBY    | Standby input, active low                        |

| TP  |          | Thermal Pad (GND)                                |

The *Thermal Pad* is to be connected to a *Ground Plane* (GND, AGND1...2) on the PCB. Only pin 1 marking on top or bottom defines the package orientation (@ HT label and coding is subject to change).

Rev B1, Page 4/45

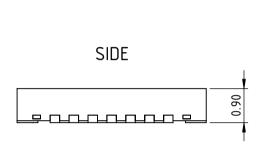

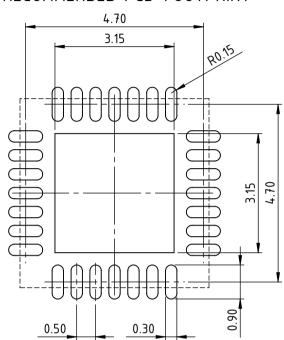

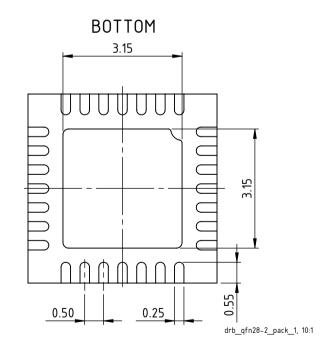

### **PACKAGE DIMENSIONS QFN28-5x5**

All dimensions given in mm.

This package falls within JEDEC MO-220-VHHD-1.

### RECOMMENDED PCB-FOOTPRINT

Rev B1, Page 5/45

### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply permissible operating conditions; functional operation is not guaranteed. Exceeding these ratings may damage the device.

| Item | Symbol  | Parameter                                                                                                                              | Conditions                           |      |      | Unit |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------|------|

| No.  |         |                                                                                                                                        |                                      | Min. | Max. |      |

| G001 | VB      | Voltage at VB                                                                                                                          |                                      | -0.3 | 11   | V    |

| G002 | I(VB)   | Current in VB                                                                                                                          |                                      | -20  | 50   | mA   |

| G003 | VDD     | Voltage at VDD                                                                                                                         |                                      | -0.3 | 5.5  | V    |

| G004 | I(VDD)  | Current in VDD                                                                                                                         |                                      | -20  | 1    | mA   |

| G005 | V()     | Voltage at CI1, CI2, EC1, EC2, MDA1, MDA2, EMC, SCLK/SCL, MISO/SDA, MOSI/A0, NCS/A1, DCO, INS/WKR, NCHK                                |                                      | -0.3 | 5.5  | V    |

| G006 | I()     | Current in CI1, CI2, EC1, EC2, MDA1, MDA2, EMC, SCLK/SCL, MISO/SDA, MOSI/A0, NCS/A1, DCO, INS/WKR, NCHK, NSTBY, CIL1, CIL2, MRL1, MRL2 |                                      | -20  | 20   | mA   |

| G007 | I(LDK)  | Current in LDK1, LDK2                                                                                                                  | DC current                           | -20  | 900  | mA   |

| G008 | V()     | Voltage at LDK1, LDK2, NSTBY                                                                                                           |                                      | -0.3 | 11   | V    |

| G009 | V()     | Voltage at AGND1, AGND2                                                                                                                |                                      | -0.3 | 1    | V    |

| G010 | I(AGND) | Current in AGND1, AGND2                                                                                                                | DC current                           | -900 | 1    | mA   |

| G011 | Vd()    | ESD Susceptibility at all pins                                                                                                         | HBM 100 pF discharged through 1.5 kΩ |      | 2    | kV   |

| G012 | Tj      | Operating Junction Temperature                                                                                                         |                                      | -40  | 125  | °C   |

| G013 | Ts      | Storage Temperature Range                                                                                                              |                                      | -40  | 150  | °C   |

### THERMAL DATA

Operating Conditions: VB = 2.8 ... 11 V (referenced to GND)

| Item | Symbol | Parameter                           | Conditions     |      |      |      | Unit |

|------|--------|-------------------------------------|----------------|------|------|------|------|

| No.  |        |                                     |                | Min. | Тур. | Max. |      |

| T01  | Та     | Operating Ambient Temperature Range |                | -40  |      | 85   | °C   |

| T02  | Rthja  | Thermal Resistance Chip/Ambient     | Mounted on PCB |      | 25   |      | K/W  |

| T03  | RthjTP | Thermal Resistance Chip/Thermal Pad |                |      | 4    |      | K/W  |

Rev B1, Page 6/45

### **ELECTRICAL CHARACTERISTICS**

| tem<br>No. | Symbol        | Parameter                                                                                                                                                                                | Conditions                                                                                                                                                 | Min.                         | Тур.                   | Max.                         | Unit           |

|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------|------------------------------|----------------|

|            | Device        |                                                                                                                                                                                          |                                                                                                                                                            | I                            | 71                     |                              |                |

| Functi     | onality and p | parameters beyond the operating on dividual application using FMEA r                                                                                                                     | conditions (with reference to independent vonethods.                                                                                                       | oltage supplie               | s, for ins             | stance) a                    | re to b        |

| 001        | VB            | Permissible Supply Voltage                                                                                                                                                               | Referenced to GND                                                                                                                                          | 2.8                          |                        | 11                           | V              |

| 002        | I(VB)         | Standby Current at VB                                                                                                                                                                    | V(NSTBY) ≤ 0.4 V                                                                                                                                           |                              |                        | 10                           | μA             |

| 003        | I(VB)         | Supply Current at VB                                                                                                                                                                     | No load, EC1, EC2, NSTBY = hi                                                                                                                              |                              |                        | 5                            | mA             |

| 004        | V(VB)on       | Turn-on threshold                                                                                                                                                                        | Increasing VB                                                                                                                                              | 1.7                          |                        | 2.7                          | V              |

| 005        | V(VB)off      | Turn-off threshold                                                                                                                                                                       | Decreasing VB                                                                                                                                              | 1.6                          |                        | 2.6                          | V              |

| 006        | V(VB)Hys      | Power-on hysteresis                                                                                                                                                                      |                                                                                                                                                            | 20                           |                        | 250                          | mV             |

| 007        | V(VDD)on      | Turn-on threshold                                                                                                                                                                        | Increasing VDD                                                                                                                                             | 1.7                          |                        | 2.4                          | V              |

| 800        | V(VDD)off     | Turn-off threshold                                                                                                                                                                       | Decreasing VDD                                                                                                                                             | 1.6                          |                        | 2.3                          | V              |

| 009        | V(VDD)Hys     | Power-on hysteresis                                                                                                                                                                      |                                                                                                                                                            | 20                           |                        | 250                          | mV             |

| 010        | V(VB)INITR    | RAM memory reset during<br>Stand-By                                                                                                                                                      | NSTBY = lo                                                                                                                                                 | 0.85                         |                        | 1.4                          | V              |

| 011        | Rgnd()        | Resistor to GND at MRL1, MRL2                                                                                                                                                            |                                                                                                                                                            |                              |                        | 20                           | Ω              |

| 012        | Ragnd()       | Resistor to AGNDx at CILx                                                                                                                                                                |                                                                                                                                                            |                              |                        | 20                           | Ω              |

| 013        | Vc()lo        | Clamp Voltage Io at VB,<br>VDD, NCHK, EMC, NCS/A1,<br>MISO/SDA, MOSI/A0,<br>SCLK/SCL, INS/WKR, NSTBY,<br>EC1, EC2, DC0, LDK1, LDK2,<br>CI1, CIL1, CI2, CIL2, AGND1,<br>AGND2, MDA1, MDA2 | I() = -10 mA                                                                                                                                               | -1.6                         |                        | -0.3                         | V              |

|            |               | c, Clx, MDAx                                                                                                                                                                             |                                                                                                                                                            | "                            |                        |                              |                |

| 101        | ` '           | Saturation Voltage lo at LDK                                                                                                                                                             | I(LDKx) = 750 mA                                                                                                                                           |                              |                        | 0.7                          | V              |

| 102        | V(LDKSAT)     | LDKx saturation detection threshold                                                                                                                                                      | RLDKSx = 00<br>RLDKSx = 01<br>RLDKSx = 10<br>RLDKSx = 11                                                                                                   | 0.35<br>0.55<br>0.85<br>1.05 | 0.5<br>0.7<br>1<br>1.2 | 0.65<br>0.85<br>1.15<br>1.35 | V<br>V<br>V    |

| 103        | Idc(LDK)      | Permissible DC Current at LDKx                                                                                                                                                           |                                                                                                                                                            |                              |                        | 750                          | mA             |

| 104        | lleak(LDK)    | LDKx leakage current                                                                                                                                                                     | V(LDKx) = 11 V                                                                                                                                             |                              |                        | 10                           | μA             |

| 105        | C(CI)         | Possible capacitor at CI1, CI2                                                                                                                                                           | ECIE = 0, EMC = hi                                                                                                                                         | 0                            |                        |                              | μF             |

| 106        | I(CI)         | Charge Current at CI1, CI2                                                                                                                                                               | V(CI) = 0 V, EC1, EC2 = hi, ECIEx = 1<br>COMP = 111                                                                                                        | -220                         |                        | -30                          | μA             |

| 107        | I(LDK)max     | Laser overcurrent shutdown threshold                                                                                                                                                     | V(LDKx) = 0.7 V VB - 1.5 V<br>ILIMx(7:0) = 0x00, RACCx = 0<br>ILIMx(7:0) = 0xFF, RACCx = 0<br>ILIMx(7:0) = 0x00, RACCx = 1<br>ILIMx(7:0) = 0xFF, RACCx = 1 | 0<br>750<br>0<br>80          |                        | 25<br>1400<br>3.2<br>175     | mA<br>mA<br>mA |

| 108        | △ I(LDK)      | Shutdown threshold resolution                                                                                                                                                            | RACCx = 0<br>RACCx = 1                                                                                                                                     | 2.8<br>0.3                   | 4<br>0.5               | 5.2<br>0.8                   | mA<br>mA       |

| 109        | tovc          | Time to overcurrent shutdown                                                                                                                                                             | Laser current decreased 10%                                                                                                                                | 1                            |                        | 5                            | μs             |

| 110        | V(MDA)        | Voltage at MDA1, MDA2                                                                                                                                                                    | Closed control loop<br>EC1, EC2 = hi<br>EMC = lo, INS/WKR = lo<br>EMC = lo, INS/WKR = hi                                                                   | 225<br>455                   | 250<br>500             | 275<br>545                   | mV<br>mV       |

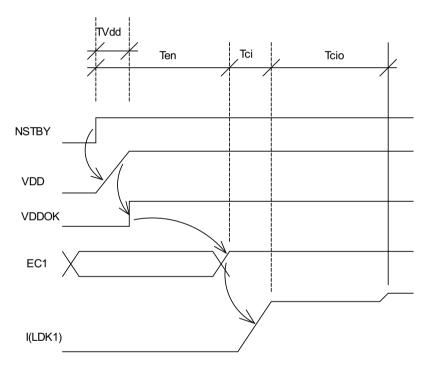

| 111        | Ten           | Time to laser enabled                                                                                                                                                                    | NSTBY Io $\rightarrow$ hi, no load at VDD, V(VDD) 0 to 90 %, CVDD = 1 $\mu$ F, EMC = Io                                                                    |                              |                        | 1.3                          | ms             |

| 112        | Tci           | Time to light                                                                                                                                                                            | NSTBY = hi, ECIE = 0, COMP = 010, light off to 80 % target value                                                                                           |                              |                        | 300                          | μs             |

| 113        | Tcio          | Time to target light                                                                                                                                                                     | Light from 80 % to 99 % target value                                                                                                                       |                              |                        | 4700                         | μs             |

Rev B1, Page 7/45

### **ELECTRICAL CHARACTERISTICS**

Operating Conditions:  $VB = 2.8 \dots 11 V$  (referenced to GND),  $Tj = -40 \dots 125 \,^{\circ}C$  unless otherwise stated

| ltem<br>No. | Symbol      | Parameter                                                                                 | Conditions                                                                   | Min.         | Тур.         | Max.         | Unit           |

|-------------|-------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------|--------------|--------------|----------------|

| 114         | Idc(LDK)    | LDKx ACC mode current                                                                     | EC1, EC2, EMC = hi, EACCx = 1,                                               | IVIII.       | ıyρ.         | IVIAA.       |                |

| 117         | IdC(LDIX)   | LDIX ACC Mode current                                                                     | V(LDKx) = 0.7 V VB - 1.5 V                                                   |              |              |              |                |

|             |             |                                                                                           | REFx(9:0) = 0x000, RACCx = 0                                                 | 50           | 82           | 120          | mA             |

|             |             |                                                                                           | REFx(9:0) = 0x3FF, $RACCx = 0$                                               | 650          | 750          | 1400         | mA             |

|             |             |                                                                                           | REFx(9:0) = 0x000, $RACCx = 1$                                               | 5            | 10           | 15           | mA             |

|             |             |                                                                                           | REFx(9:0) = 0x3FF, RACCx = 1                                                 | 70           | 113          | 160          | mA             |

| 115         | Tk          | Temperature coefficient ACC mode                                                          |                                                                              | -1500        | -500         | 0            | ppm/K          |

| Progra      | ammable Re  |                                                                                           |                                                                              |              |              |              |                |

| 201         | Rmda        | Resistor at MDAx pin                                                                      | RMDx(7:0) = 0xF0 0xFF, DISPx = 0<br>RMDx(7:0) = 0x00 0x0F, DISPx = 0         | 350<br>0.154 | 500<br>0.220 | 650<br>0.286 | kΩ<br>kΩ       |

| 202         | Tk          | Temperature coefficient                                                                   |                                                                              | -1500        | -500         | 0            | ppm/K          |

| 203         | ΔR          | Resistor increment                                                                        | $\Delta R = \frac{R(n+1) - R(n)}{R(n)}$                                      | 2            | 3.3          | 5            | %              |

| 204         | Ileak(MDA)  | MDAx leakage current                                                                      | DISPx = 1                                                                    | -1           |              | 1            | μA             |

| D/A C       | onverter    |                                                                                           | ı                                                                            |              |              |              |                |

| 301         | R(DAC)      | D/A Converter Resolution                                                                  |                                                                              |              |              | 10           | bit            |

| 302         | Δ٧          | Percentual voltage increments                                                             | $\Delta V = \frac{V(n+1) - V(n)}{V(n)}$                                      | 0.1          | 0.235        | 0.5          | %              |

| 303         | V(DAC)      | D/A Converter                                                                             | REFx(9:0) = 0x000 lowest value<br>REFx(9:0) = 0x3FF highest value            | 0.09<br>1.00 | 0.10<br>1.10 | 0.12<br>1.25 | V<br>V         |

| Check       | Output NCI  | HK                                                                                        |                                                                              |              |              |              | "              |

| 401         | Vs()lo      | Saturation Voltage lo at NCHK                                                             | I(NCHK) = 1.0 mA                                                             |              |              | 0.4          | V              |

| 402         | Isc()lo     | Short Circuit Current lo at NCHK                                                          | V(NCHK) = 0.4 3.3 V                                                          | 9            |              | 33           | mA             |

| 403         | llk()       | Leakage Current at NCHK                                                                   | NCHK = 1;<br>V(NCHK) = 05.5 V                                                | -1           |              | 1            | μA             |

| Series      | Regulator ( | Output VDD                                                                                | ı                                                                            |              |              |              | II.            |

| 501         | V(VDD)      | Regulated output voltage                                                                  | VB = 3.7 8 V, I(VDD) = -10 0 mA<br>NSTBY = hi                                | 3            |              | 3.5          | V              |

| 502         | V(VB,VDD)   | Voltage Drop between VB and VDD                                                           | VDD unregulated, I(VDD) = -10 0 mA<br>NSTBY = hi                             |              | 100          | 400          | mV             |

| 503         | C(VOUT)     | Capacitor at VDD                                                                          | Ri(C) < 1 Ω                                                                  | 1            |              | 3.3          | μF             |

| 504         | Tvdd        | Settling time VDD                                                                         | NSTBY Io $\rightarrow$ hi, no load at VDD, V(VDD) 0 to 90 % CVDD = 1 $\mu$ F |              |              | 1            | ms             |

| Digita      | l inputs    |                                                                                           |                                                                              |              |              |              |                |

| 601         | Vt()hi      | Input Threshold Voltage hi at                                                             |                                                                              |              |              | 2            | V              |

|             |             | EMC, NCS/A1, MISO/SDA,<br>MOSI/A0, SCLK/SCL, INS/WKR,<br>NSTBY, EC1, EC2                  |                                                                              |              |              |              |                |

| 602         | Vt()lo      | Input Threshold Voltage lo at                                                             | VB > 3 V                                                                     | 0.7          |              |              | V              |

|             |             | EMC, NCS/A1, MISO/SDA,<br>MOSI/A0, SCLK/SCL, INS/WKR,<br>NSTBY, EC1, EC2                  | VB = 2.8 V                                                                   | 0.6          |              |              | V              |

| 603         | Vt()hys     | Hysteresis at EMC, NCS/A1,<br>MISO/SDA, MOSI/A0,<br>SCLK/SCL, INS/WKR, NSTBY,<br>EC1, EC2 | Vt()hys = Vt()hi - Vt()lo                                                    | 100          |              |              | mV             |

| 604         | lpd()       | Pull-Down Current at MOSI/A0,<br>EC1, EC2                                                 | V() = 0.4 V VDD                                                              | 1            |              | 50           | μA             |

| 605         | lpd()       | Pull-Down Current at NSTBY                                                                | V() = 0.4 V VB                                                               | 1            |              | 50           | μA             |

| 606         | Rpu()       | Pull-Up Resistor at SCLK/SCL, NCS/A1                                                      |                                                                              | 80           | 150          | 260          | kΩ             |

| 607         | Rpu()       | Pull-Up Resistor at MISO/SDA                                                              | EMC = hi, INS/WKR = lo<br>EMC = hi, INS/WKR = hi                             | 8<br>53      | 20<br>100    | 50<br>174    | kΩ<br>kΩ       |

| 608         | Er()        | Safe enable threshold voltage at EMC, INS/WKR                                             | Rising Falling                                                               | 52<br>30     | 54<br>32     | 56<br>34     | % VDD<br>% VDD |

Rev B1, Page 8/45

### **ELECTRICAL CHARACTERISTICS**

Operating Conditions:  $VB = 2.8 \dots 11 V$  (referenced to GND),  $Tj = -40 \dots 125 \,^{\circ}C$  unless otherwise stated

| Item<br>No. | Symbol      | Parameter                            | Conditions                                                   | Min.     | Тур. | Max.      | Unit             |

|-------------|-------------|--------------------------------------|--------------------------------------------------------------|----------|------|-----------|------------------|

| 609         | Voc()       | Open Circuit Voltage at EMC, INS/WKR |                                                              | 39       | 41   | 43        | % VDD            |

| 610         | Ri()        | Internal Resistance at EMC, INS/WKR  |                                                              | 170      | 250  | 330       | kΩ               |

| 611         | Isc()lo     | Short Circuit current lo at MISO/SDA | INS/WKR = Io, V(MISO/SDA) = 5.5 V                            | -40      |      | -4        | mA               |

| 612         | Vs()lo      | Saturation Voltage lo at MISO/SDA    | INS/WKR = Io, I(MISO/SDA) = 2 mA                             |          |      | 0.4       | V                |

| A/D C       | onverter    |                                      |                                                              |          |      |           |                  |

| 701         | Ton         | Converter initialization time        | ADCCx(2) changes from 0 to 1<br>LDKx, VDD or VB measurements |          |      | 500       | μs               |

| 702         | Tconv       | Conversion time                      |                                                              |          |      | 140       | μs               |

| 703         | R(ADC)      | A/D Converter Resolution             |                                                              |          |      | 10        | bit              |

| 704         | RAC         | Relative Accuracy                    |                                                              | -1       |      | +1        | LSB              |

| 705         | VZS()       | Zero Scale Voltage                   | ADCx(9:0) = 000h                                             |          | 0    |           | V                |

| 706         | VFS()       | Full Scale Voltage                   | ADCx(9:0) = 3FFh                                             | 1.0      | 1.1  | 1.2       | V                |

| 707         | MDAM        | MDAx Measurement                     | MDAx = 0.5 V, ADCCx(2:0) = 100, ADSNFx = 0                   | 372      | 465  | 558       | LSB              |

| 708         | VDDM        | VDD Measurement                      | VDD = 3.3 V, ADCCx(2:0) = 110                                | 312      | 390  | 468       | LSB              |

| 709         | VBM         | VB Measurement                       | VB = 8 V, ADCCx(2:0) = 101                                   | 744      | 930  | 1023      | LSB              |

| 710         | LDKM        | LDKx Measurement                     | LDKx = 8 V, ADCCx(2:0) = 111                                 | 744      | 930  | 1023      | LSB              |

| Overt       | emperature  |                                      | , ,                                                          |          |      |           | Ш                |

| B01         | Toff        | Overtemperature Shutdown             | Rising temperature                                           | 130      |      | 170       | °C               |

| B02         | Ton         | Overtemperature Release              | Falling temperature                                          | 120      |      | 165       | °C               |

| B03         | Thys        | Hysteresis                           | Toff — Ton                                                   | 3        |      |           | °C               |

| Temp        | erature Mon | itor                                 |                                                              |          |      |           | Ш                |

| C01         | Trange      | Temperature Measurement Range        |                                                              | -40      |      | 125       | °C               |

| C02         | Tresol      | Temperature Measurement Resolution   |                                                              |          | 1    |           | °C               |

| C03         | Reading     | Temperature Value Ranges             | Tj = 125 °C<br>Tj = -40 °C                                   | 160<br>0 |      | 190<br>15 | digits<br>digits |

| DCO (       | Output      |                                      |                                                              |          |      |           |                  |

| D01         | Isc()hi     | DCO Output Current                   | V(VDD) = 33.5 V, V(DCO) < 1.4 V,<br>RDCO = 0x3F              | -175     | -130 | -85       | μA               |

| D02         | lleak       | Leakage Current at DCO               | RDCO = 0x00 or NSTBY = Io,<br>V(DCO) = 0 5.5 V               | -1       |      | 1         | μA               |

| D03         | I(DCO)LSB   | I(DCO) Resolution                    | V(DCO) < 1.4 V                                               | 1.3      | 2    | 2.7       | μΑ               |

| Oscill      | ator        |                                      | •                                                            |          |      |           |                  |

| E01         | Fosc        | Oscillator Frequency                 | NSTBY = hi                                                   | 100      | 200  | 400       | kHz              |

| E02         | T(cfgtimo)  | Configuration Mode Timeout           | MODE(1:0) = 10                                               | 40       | 82   | 164       | ms               |

| E03         | tWDT        | Watchdog Timeout                     | NSTBY = hi                                                   | 20       |      | 120       | μs               |

Rev B1, Page 9/45

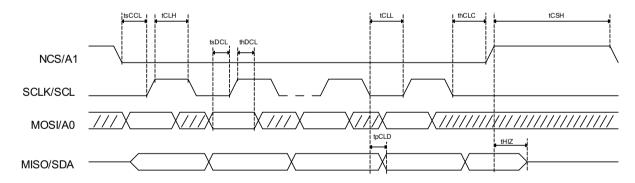

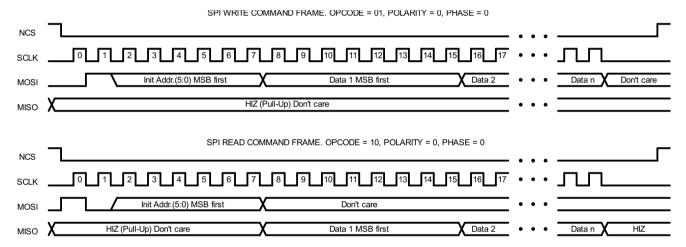

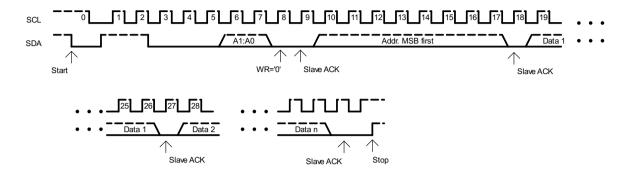

### **OPERATING REQUIREMENTS: SPI and I<sup>2</sup>C Interface**

Operating Conditions:  $VB = 2.8 \dots 11 V$ ,  $Tj = -40 \dots 125 °C$

| Item                 | Symbol      | Parameter                                                              | Conditions                                                     |      |      | Unit |

|----------------------|-------------|------------------------------------------------------------------------|----------------------------------------------------------------|------|------|------|

| No.                  |             |                                                                        |                                                                | Min. | Max. |      |

| SPI / I <sup>2</sup> | C Interface | Timing                                                                 |                                                                |      |      |      |

| 1001                 | tsCCL       | Setup Time: NCS/A1 hi $\rightarrow$ lo before SCLK lo $\rightarrow$ hi | INS/WKR = Io                                                   | 20   |      | ns   |

| 1002                 | tsDCL       | Setup Time:<br>MOSI/A0 stable before SCLK/SCL lo<br>→ hi               | INS/WKR = Io                                                   | 20   |      | ns   |

| 1003                 | thDCL       | Hold Time: MOSI/A0 stable after SCLK/SCL lo $\rightarrow$ hi           | INS/WKR = Io                                                   | 20   |      | ns   |

| 1004                 | tCLh        | Signal Duration SCLK/SCL hi                                            | INS/WKR = Io                                                   | 50   |      | ns   |

| 1005                 | tCLI        | Signal Duration SCLK/SCL lo                                            | INS/WKR = Io                                                   | 50   |      | ns   |

| 1006                 | thCLC       | Hold Time: NCS/A1 lo after SCLK/SCL hi $\rightarrow$ lo                | INS/WKR = Io                                                   | 20   |      | ns   |

| 1007                 | tCSh        | Signal Duration NCS/A1 hi                                              | INS/WKR = Io                                                   | 50   |      | ns   |

| 1008                 | tpCLD       | Propagation Delay: MISO/SDA stable after SCLK/SCL hi → lo              | INS/WKR = Io, V(VDD) > 3 V, Cload = 10 pF, no external pull-up | 0    | 30   | ns   |

| 1009                 | tHIZ        | MISO to HIZ delay                                                      | INS/WKR = Io                                                   | 0    | 25   | ns   |

| 1010                 | f(SCLK)     | SPI clock frequency                                                    |                                                                |      | 10   | MHz  |

| I011                 | f(SCL)      | I <sup>2</sup> C clock frequency                                       |                                                                |      | 400  | kHz  |

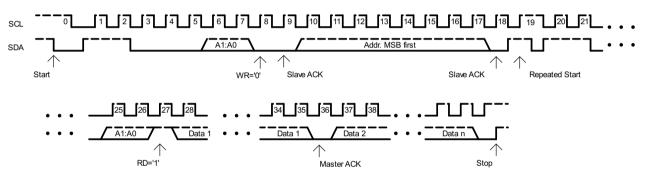

Figure 1: SPI interface timing

Rev B1, Page 10/45

#### **OPERATING AND STANDBY MODES**

iC-HT operating modes are selected by the pins EMC and INS. These pins are intended to be static and should not be changed during operation to avoid misconfiguration or unintended operation. It is recommended to tie the pins EMC and INS to VDD or GND. Floating pins EMC and INS/WKR are detected as faulty configuration and signaled at NCHK.

#### iC-WK mode

In iC-WK mode the iC-HT operates as an Automatic Power Control (APC) laser controller, similar to iC-Haus iC-WK/iC-WKL, iC-WKM and iC-WKN. iC-WK mode is set by pin configuration and the external monitor resistor. Pin EMC is set to lo and pin INS/WKR selects the reference voltage:

- INS/WKR = hi for 0.5 V reference voltage, similar to iC-WK, iC-WKL, iC-WKN.

- INS/WKR = lo for 0.25 V reference voltage, similar to iC-WM.

Floating pins EMC and INS/WKR are detected as faulty configuration and signaled at NCHK.

### **MCU** mode

In microcontroller unit (MCU) mode, iC-HT features two control modes: automatic power control (APC) and automatic current control (ACC). Pin EMC is set to hi and pin INS/WKR selects the serial communication interface protocol. Selection of the communication protocol is achieved through pin INS/WKR:

- INS/WKR = hi for I2C.

- INS/WKR = Io for SPI.

Floating pins EMC and INS/WKR are detected as faulty configuration and signaled at pin NCHK. Any input interface could be enabled if EMC or INS pins are open. Comunication with the chip might be possible but laser cannot be switched on. This situation is only signaled at pin NCHK, which would remain low as long as any of the EMC or INS pins are unconnected. MCU must monitor the status of the pin NCHK to get all the status information of the chip.

#### **Standby Mode**

iC-HT in standby mode has a very low current consumption (<10 μA) and does retain its configuration. Standby mode will not reset the internal RAM.

In order to exit standby mode, pin NSTBY must be set to hi (e.g. VB). VDD is switched off in standby mode and can not be used to exit standby mode.

VB, NSTBY and LDKx withstand voltages up to 11 V, whereas the remaining input pins operate up to 5.5 V and do have high impedance at standby mode.

Information on timing after waking up from standby mode can be found on page 36.

Rev B1, Page 11/45

#### LASER DIODE/LED TYPES AND OPERATION MODES

For APC operation a monitor diode is required. This operation is possible in microcontroller unit (MCU) mode and in the iC-WK mode.

iC-HT can operate in APC two types of laser diodes/LEDs with monitor diodes:

- N-Type laser diodes

- M-Type laser diodes

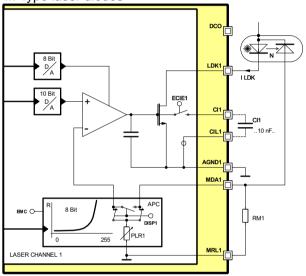

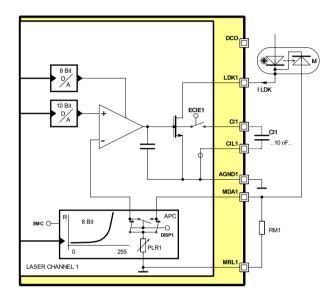

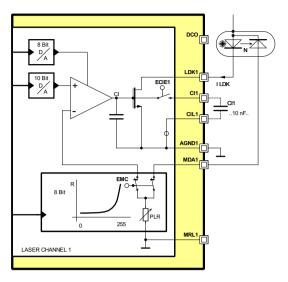

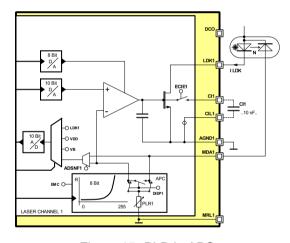

Figure 2: iC-HT with N-type laser diode

In automatic current control (ACC) operation there is no monitor diode and any diode can be operated in microcontroller unit (MCU) mode.

All operations are possible with laser diodes (LDs) or light emitting diodes (LEDs). In the following text we do not differ between laser diodes (LDs) and light emitting diodes (LEDs).

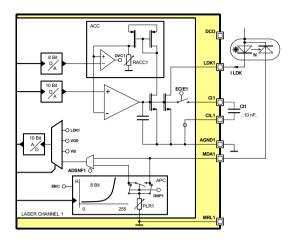

Figure 3: iC-HT with M-type laser diode

Rev B1, Page 12/45

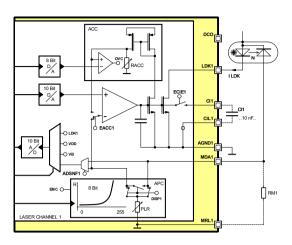

#### **iC-WK MODE**

Setting pin EMC = lo configures iC-HT for iC-WK mode. EMC pin must be set to GND.

In iC-WK mode both channels operate in APC mode. The internal programmable logarithmic monitor resistors are disabled, therefore connection of external resistors at pins MDAx is required.

The APC reference can be set to two different values by means of pin INS/WKR, as it is explained in table 5, and the overcurrent threshold is set to its maximum value of 750 mA (cf. *Electrical Characteristics No. 107*). In case of overcurrent, the respective channel is disabled. For re-enabling the channel, the corresponding ECx pin must be set lo and then back hi.

| Reference Voltage in iC-WK mode |                                  |                          |  |  |

|---------------------------------|----------------------------------|--------------------------|--|--|

| INS/WKR                         | /KR Reference similar to Voltage |                          |  |  |

| Lo                              | 0.25 V                           | iC-WKM                   |  |  |

| Hi                              | 0.5 V                            | iC-WK, iC-WKL,<br>iC-WKN |  |  |

Table 5: Reference selection (cf. *Electrical Characteristics No. 110*)

External CI capacitors must be added in this operation mode at pins CIx and CILx. Figure 4 shows an example in iC-WK mode using an N-type laser diode, where 0.5 V reference is selected. Figure 5 presents the same configuration with an M-type laser diode.

Figure 4: iC-HT in iC-WK mode with N-type laser diode

Rev B1, Page 13/45

Figure 5: iC-HT in iC-WK mode with M-type laser diode

In the configuration from figures 4 and 5 pin NSTBY is connected to VB. This is required to force iC-HT leaving standby mode and starting normal operation, as the pin includes an internal pull-down resistor.

### Laser channel enabling

Setting pins EC1, EC2 to hi enables the corresponding channels. In order to ensure safe operation of iC-HT, several events automatically disable both output channels:

- Pins INS/WKR or EMC left unconnected (IN-SOPEN, EMCOPEN), iC-HT enters error mode and the laser channels cannot be enabled.

- Supply power-down either at VB (PDOVB) or VDD (PDOVDD), the laser channels are unconditionally disabled during the power down event.

- Overcurrent (OVC) or overtemperature (OVT), laser channels are switched off. Cycling pins EC1, EC2 or a power-up is required to switch on the laser again.

Rev B1, Page 14/45

#### **MICROCONTROLLER MODE**

Setting pin EMC to hi configures iC-HT for microcontroller mode (MCU mode). EMC pin must be set using a pull-up resistor or directly short-circuited to VDD pin. Several parameters can be configured through a microcontroller via I<sup>2</sup>C or SPI communication. More information about the serial communication interface can be found on page 23.

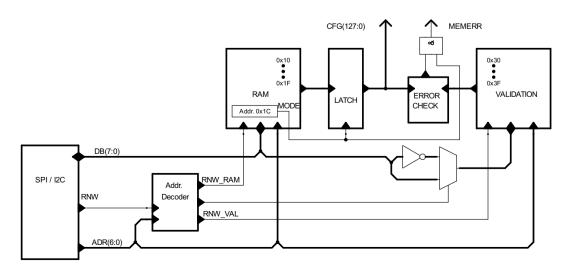

The configuration of the internal parameters of iC-HT must be done in configuration mode. In this mode, the configuration memory can be written and read back without changing the previous configuration state of iC-HT. Once the configuration is considered as valid, iC-HT can be switched to operation mode. These two modes are configured by the MODE register. If the time in configuration mode exceeds the Configuration Mode Timeout (cf. *Electrical Characteristics No. E02*), both channels will be switched off. More information on page 34.

Each individual channel can be enabled by setting pin ECx to hi. Setting register bits DISCx to 1 disables the corresponding channel. If either pin ECx is lo or register bits DISCx is 1, the corresponding channel is disabled.

| DISC1 | Addr. 0x10; bit 3                      | R/W 1 |  |

|-------|----------------------------------------|-------|--|

| 0     | Channel 1 can be enabled by pin EC1    |       |  |

| 1     | Channel 1 cannot be enabled by pin EC1 |       |  |

Table 6: Disable channel 1

| DISC2 | Addr. 0x15; bit 3                      | R/W 1 |  |

|-------|----------------------------------------|-------|--|

| 0     | Channel 2 can be enabled by pin EC2    |       |  |

| 1     | Channel 2 cannot be enabled by pin EC2 |       |  |

Table 7: Disable channel 2

Different voltages can be measured using a 10 bit A/D converter with two resolutions. The following internal voltages can be measured:

- V(LDKx) up to 8 V with 8.6 mV resolution

- V(VDD) up to 8 V with 8.6 mV resolution

- V(VB) up to 8 V with 8.6 mV resolution

- V(MDAx) up to 1 V with 1.075 mV resolution

- V(PLRx) up to 1 V with 1.075 mV resolution

The register bits ADCCx select the signal measured with the 10 bit A/D converter.

| ADCC1(2:0) | Addr. 0x10; bit 7:5 | R/W 000 |

|------------|---------------------|---------|

| 0xx        | Disabled            |         |

| 100        | V(MDA1), ADSNF1 = 0 |         |

| 100        | V(PLR1), ADSNF1 = 1 |         |

| 101        | V(VB)               |         |

| 110        | V(VDD)              |         |

| 111        | V(LDK1)             |         |

Table 8: ADC channel 1 source selection

| ADCC2(2:0) | Addr. 0x15; bit 7:5   | R/W 000 |

|------------|-----------------------|---------|

| 0xx        | Disabled              |         |

| 100        | V(MDA2), $ADSNF2 = 0$ |         |

| 100        | V(PLR2), ADSNF2 = 1   |         |

| 101        | V(VB)                 |         |

| 110        | V(VDD)                |         |

| 111        | V(LDK2)               |         |

Table 9: ADC channel 2 source selection

With ADCCx(2:0) = 100, the signal to the A/D converter is selected by register bit ADSNFx. With ADSNFx = 1 the measuring point to the A/D converter is the internal sense node of the internal programmable logarithmic monitor resistor (PLR). With ADSNFx = 0 the sensing point is connected directly to MDAx pin.

| ADSNF1 | Addr. 0x1A; bit 2                | R/W 0 |

|--------|----------------------------------|-------|

| 0      | ADC measurement pin MDA1 (force) |       |

| 1      | ADC measurement PLR1 (sense)     |       |

Table 10: ADC channel 1 sense/force selection

| ADSNF2 | Addr. 0x1A; bit 6                | R/W 0 |

|--------|----------------------------------|-------|

| 0      | ADC measurement pin MDA2 (force) |       |

| 1      | ADC measurement PLR2 (sense)     |       |

Table 11: ADC channel 2 sense/force selection

Rev B1, Page 15/45

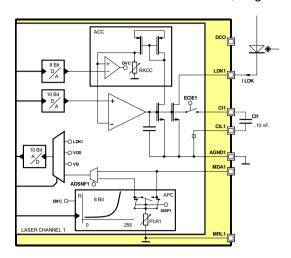

Figure 6: Channel 1 schematic

Two different control modes can be configured independent for each channel: automatic power control (APC) and automatic current control (ACC). In both modes a 10 bit logarithmic D/A converter sets the reference voltage and an 8 bit programmable D/A converter configures the overcurrent threshold.

#### **APC (Automatic Power Control) mode**

In APC mode the laser power is controlled. The monitor diode current is used as feedback in the laser power control loop. APC mode is selected by setting EACCx register bit to 0.

| EACC1 | Addr. 0x10; bit 0              | R/W 0 |

|-------|--------------------------------|-------|

| 0     | APC mode enabled for channel 1 |       |

| 1     | ACC mode enabled for channel 1 |       |

Table 12: APC/ACC in channel 1

| EACC2 | Addr. 0x15; bit 0              | R/W 0 |

|-------|--------------------------------|-------|

| 0     | APC mode enabled for channel 2 |       |

| 1     | ACC mode enabled for channel 2 |       |

Table 13: APC/ACC in channel 2

An example of APC with default configuration is shown in figure 7.

Figure 7: APC mode simplified

An internal 8 bit programmable logarithmic monitor resistor (PLR) can be used in APC mode. In APC mode it is also possible to use an external monitor resistor connected to pin MDAx. If register bit DISPx is 0, the PLR is present. If DISPx is 1, the PLR is disabled and an external monitor resistor must be used.

| DIS | P1 | Addr. 0x10; bit 2          | R/W 0 |

|-----|----|----------------------------|-------|

| 0   |    | PLR enabled for channel 1  |       |

| 1   |    | PLR disabled for channel 1 |       |

Table 14: Disable PLR channel 1

| DISP2 | Addr. 0x15; bit 2          | R/W 0 |

|-------|----------------------------|-------|

| 0     | PLR enabled for channel 2  |       |

| 1     | PLR disabled for channel 2 |       |

Table 15: Disable PLR channel 2

Both programmable logarithmic monitor resistors (PLR) feature a wide logarithmic resistor range from  $100\,\Omega$  to  $500\,k\Omega$ , in steps of typically 3.3%. This covers a wide range of monitor currents. More information about the PLR can be found on page 25.

For fine-tuning the optical power, the reference voltage can be set with a 10 bit logarithmic D/A converter, which is configurable through the register REFx. This converter has a voltage range that goes typically from 0.1 V to 1.1 V, allowing an operation resolution of typically 0.235%. More information on the logarithmic D/A converter can be found on page 26.

For calculating the minimum value of Imon, Vref(0x00, max value) (cf. *Electrical Characteristics No. 303*) and Rmda(RMDx = 0xFF, min value) (cf. *Electrical Characteristics No. 201*) are used.

## iC-HT

### **DUAL CW LASER DIODE DRIVER**

Rev B1, Page 16/45

$$Imon(min) = \frac{Vref(0x000, max)}{Rmda(RMDx = 0xFF, min)} = \frac{0.11}{350000} = 0.31 \ uA$$

It is not recommended to configure iC-HT to have such small Imon values, otherwise the leakage current at MDAx may have an influence (cf. *Electrical Characteristics No. 204*), especially at high temperatures. To avoid this, Imon should be much greater than the leakage current.

For calculating the maximum value of Imon, Vref(0x3FF, min value) (cf. *Electrical Characteristics No. 303*) and Rmda(RMDx = 0x00, max vaule) (cf. *Electrical Characteristics No. 201*) are used. The following formula can to be used for calculating Rmda(RMDx = 0x00, max value):

$$Rmd = Rmd_0(1 + \frac{\Delta Rmd(\%)}{100})^{n+1}$$

, n from 0 to 255

$$Rmda(RMDx = 0x00, max) = Rmd_0(1 + \frac{\Delta Rmd(\%)}{100})^{16}$$

$$286 = Rmd_0(1 + \frac{3.3}{100})^{16}$$

$Rmd_0 = 170\Omega$

Therefore:

$$Imon(max) = \frac{Vref(0x3FF, min)}{Rmd_0} = \frac{1.00}{170} = 5.88 \text{ mA}$$

Any other Imon value can be calculated using Rmd formula above. Due to its logarithmic characteristic, the steps between two consecutive values is kept within 3.3 % typical value.

The programmable overcurrent shutdown can be set to protect the laser by disabling the channel. The overcurrent threshold is configurable in two different ranges. The range is selected through register bit RACCx. If RACCx= 1, the overcurrent threshold is in the low range, up to  $90 \, \text{mA}$ . If RACCx= 0, the overcurrent threshold is in the high range, up to  $750 \, \text{mA}$  (cf. *Electrical Characteristics No. 107*).

| RACC1 | Addr. 0x1A; bit 0                | R/W 0 |

|-------|----------------------------------|-------|

| 0     | Current range high for channel 1 |       |

| 1     | Current range low for channel 1  |       |

Table 16: RACC1 current range configuration channel

| RACC2 | Addr. 0x1A; bit 4                | R/W 0 |

|-------|----------------------------------|-------|

| 0     | Current range high for channel 2 |       |

| 1     | Current range low for channel 2  |       |

Table 17: RACC2 current range configuration channel 2

In each range, the particular overcurrent threshold value can be set in register ILIMx. The regulator does not differ the two current ranges in APC.

| ILIM1 | Addr. 0x11; bit 7:0                                                                        | R/W 0xFF  |

|-------|--------------------------------------------------------------------------------------------|-----------|

| 0x0A  | Channel 1 overcurrent threshold set to current                                             | o minimum |

|       | Channel 1 overcurrent threshold set to $llim = (\Delta l(LDK) \cdot n)$ , n from 10 to 255 |           |

| 0xFF  | Channel 1 overcurrent threshold set to current                                             | o maximum |

Table 18: Overcurrent threshold configuration channel

1

| ILIM2 | Addr. 0x16; bit 7:0                                                                    | R/W 0xFF   |

|-------|----------------------------------------------------------------------------------------|------------|

| 0x0A  | Channel 2 overcurrent threshold set current                                            | to minimum |

|       | Channel 2 overcurrent threshold set $llim = (\Delta I(LDK) \cdot n)$ , n from 10 to 2: | t to<br>55 |

| 0xFF  | Channel 2 overcurrent threshold set current                                            | to maximum |

Table 19: Overcurrent threshold configuration channel

An overcurrent event can be simulated using SOVCx. If SOVCx=1, the corresponding overcurrent error bit OVCx will be set to 1, the error will be signaled at NCHK and the corresponding laser channel will be disabled. The overcurrent error will remain forced until SOVCx=0.

| SOVC1 | Addr. 0x1D; bit 5                               | R/W 0 |

|-------|-------------------------------------------------|-------|

| 0     | No Overcurrent event at channel 1 is simulated. |       |

| 1     | Overcurrent event at channel 1 simulated.       |       |

Table 20: Simulate overcurrent channel 1

| SOVC2 | Addr. 0x1D; bit 6                      | R/W 0      |

|-------|----------------------------------------|------------|

| 0     | No overcurrent event at channel 2 is s | simulated. |

| 1     | Overcurrent event at channel 2 simula  | ated.      |

Table 21: Simulate overcurrent channel 2

Rev B1, Page 17/45

### **ACC (Automatic Current Control) mode**

In this mode, the laser diode current is controlled and no monitor diode is required. ACC mode is selected setting EACCx register bit to 1.

| EACC1 | Addr. 0x10; bit 0              | R/W 0 |

|-------|--------------------------------|-------|

| 0     | APC mode enabled for channel 1 |       |

| 1     | ACC mode enabled for channel 1 |       |

Table 22: APC/ACC in channel 1

| EACC2 | Addr. 0x15; bit 0              | R/W 0 |

|-------|--------------------------------|-------|

| 0     | APC mode enabled for channel 2 |       |

| 1     | ACC mode enabled for channel 2 |       |

Table 23: APC/ACC in channel 2

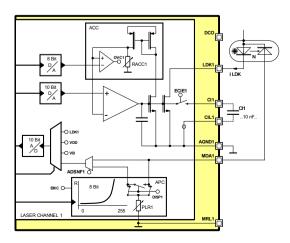

In ACC mode the internal programmable logarithmic monitor resistor (PLR) is not used. Instead the internal RACCx resistor is used to set the current. For fine-tuning the regulated current, the reference voltage can be set with a 10 bit logarithmic D/A converter, which is configurable through the register REFx. This converter has a voltage range that goes typically from 0.1 V to 1.1 V, allowing an operation resolution of typically 0.235%. More information on the logarithmic D/A converter can be found on page 26. Figure 8 shows an example of this configuration.

Two different current ranges can be set through register bit RACCx, with RACCx = 1 for up to 75 mA and with RACCx = 0 for up to 650 mA. The programmable overcurrent shutdown protects against over regulations during the laser power-on. Table 44 shows some typical current settings. For detailed limits, please refer to *Electrical Characteristics No. 114*

| ACC typical current settings |          |          |  |

|------------------------------|----------|----------|--|

| REFx                         | RACCx=0  | RACCx=1  |  |

| 0x000                        | 77.0 mA  | 9.06 mA  |  |

| 0x001                        | 77.2 mA  | 9.08 mA  |  |

| 0x010                        | 77.4 mA  | 9.10 mA  |  |

|                              |          |          |  |

| 0x200                        | 256.2 mA | 30.14 mA |  |

| 0x201                        | 256.8 mA | 30.21 mA |  |

| 0x202                        | 257.4 mA | 30.28 mA |  |

|                              |          |          |  |

| 0x3FD                        | 846.0 mA | 99.53 mA |  |

| 0x3FE                        | 848.0 mA | 99.77 mA |  |

| 0x3FF                        | 850.0 mA | 100 mA   |  |

Table 24: ACC typical current settings

Figure 8: ACC mode simplified

| RACC1 | Addr. 0x1A; bit 0                | R/W 0 |

|-------|----------------------------------|-------|

| 0     | Current range high for channel 1 |       |

| 1     | Current range low for channel 1  |       |

Table 25: RACC1 configuration

| RACC2 | Addr. 0x1A; bit 4                | R/W 0 |

|-------|----------------------------------|-------|

| 0     | Current range high for channel 2 |       |

| 1     | Current range low for channel 2  |       |

Table 26: RACC2 configuration

In each range, the particular overcurrent threshold value can be set in register ILIMx. The regulator does differ the two current ranges in ACC.

| ILIM1 | Addr. 0x11; bit 7:0                                                                        | R/W 0xFF  |

|-------|--------------------------------------------------------------------------------------------|-----------|

| 0x0A  | Channel 1 overcurrent threshold set t current                                              | o minimum |

|       | Channel 1 overcurrent threshold set to $llim = (\Delta I(LDK) \cdot n)$ , n from 10 to 255 |           |

| 0xFF  | Channel 1 overcurrent threshold set t current                                              | o maximum |

Table 27: Overcurrent threshold configuration channel 1

| ILIM2 | Addr. 0x16; bit 7:0                                                                          | R/W 0xFF  |

|-------|----------------------------------------------------------------------------------------------|-----------|

| 0x0A  | Channel 2 overcurrent threshold set t current                                                | o minimum |

|       | Channel 2 overcurrent threshold set term $Ilim = (\Delta I(LDK) \cdot n)$ , n from 10 to 255 |           |

| 0xFF  | Channel 2 overcurrent threshold set t current                                                | o maximum |

Table 28: Overcurrent threshold configuration channel 2

An overcurrent event can be simulated using bit SOVCx. If SOVCx=1, the corresponding overcurrent

Rev B1, Page 18/45

error bit OVCx will be set to 1, the error will be signaled through NCHK and the corresponding laser channel will be disabled. The overcurrent error will remain forced until SOVCx = 0.

| SOVC1 | Addr. 0x1D; bit 5                        | R/W 0    |

|-------|------------------------------------------|----------|

| 0     | No overcurrent event at channel 1 is sim | nulated. |

| 1     | Overcurrent event at channel 1 simulate  | d.       |

Table 29: Simulate overcurrent channel 1

| SOVC2 | Addr. 0x1D; bit 6                               | R/W 0 |

|-------|-------------------------------------------------|-------|

| 0     | No overcurrent event at channel 2 is simulated. |       |

| 1     | Overcurrent event at channel 2 simulated.       |       |

Table 30: Simulate overcurrent channel 2

An external capacitor can be added in ACC mode in order to avoid oscillations as it is shown in figure 8. The external Clx must be enabled setting the ECIEx bit (Tables 93 and 106).

In ACC mode, the MDAx pin can be monitored through a 10 bit A/D converter. This can be used for measuring the laser light power, if a photodiode is connected to pin MDAx, as it is shown in figure 9. This allows adjusting the voltage reference in order to set the laser current and obtain the desired laser light power.

The internal programmable logarithmic monitor Resistor (PLR), if enabled (DISPx = 0), gives feedback for the current control through the 10 bit A/D converter. Register bit ADSNFx must be set to 1 in order to measure the internal sense node. An external monitor resistor can be used to measure the optical power, achieved by setting DISPx to 1. Therefore register bit ADSNFx must be set to 0 in order to measure directly at pin MDAx.

Figure 9: ACC with monitor photodiode

ACC mode permits to combine both channels in one iC-HT (see chapter COMBINING BOTH CHANNELS) and several iC-HT in parallel. When both channels are combined the programmable overcurrent shutdown is by channel. Another option is to connect the LDK together when both channels are configured in ACC mode and the channel 1 with high current range configuration and the channel 2 with low current range configuration. With this pre-sets there is a granularity about 0.2% using the channel 1 steps regulation and about 0.03% using the channel 2 in the regulation.

#### The Regulator

In MCU mode the control can be carried out without the need of external capacitor. This allows a fast response of the regulator. The speed of the regulator's response and stability can be configured using three bits (COMPx), providing a compensation factor.

| COMP1 | Addr. 0x13; bit 6:4 R                                                          | /W 011   |

|-------|--------------------------------------------------------------------------------|----------|

| 000   | Minimum compensation for the channel 1 re slower response of regulator         | gulator, |

|       |                                                                                |          |

| 111   | Maximum compensation for the channel 1 regulator, faster response of regulator |          |

Table 31: Regulator delay compensation channel 1

| COMP2 | Addr. 0x18; bit 6:4                                                          | R/W 011          |

|-------|------------------------------------------------------------------------------|------------------|

| 000   | Minimum compensation for the char slower response of regulator               | nel 2 regulator, |

|       |                                                                              |                  |

| 111   | Maximum compensation for the char<br>regulator, faster response of regulator |                  |

Table 32: Regulator delay compensation channel 2

Alternatively it is possible to use external capacitors connected to pins CIx and CILx. In this case, register bit ECIEx should be set to 1 and COMPx to its highest value, "111".

| ECIE1 | Addr. 0x10; bit 1                      | R/W 0      |

|-------|----------------------------------------|------------|

| 0     | External CI capacitor for channel 1 di | sconnected |

| 1     | External CI capacitor for channel 1 co | onnected   |

Table 33: Enable external capacitor channel 1

|   | ECIE2 | Addr. 0x15; bit 1                                | R/W 0 |  |  |

|---|-------|--------------------------------------------------|-------|--|--|

| ĺ | 0     | External CI capacitor for channel 2 disconnected |       |  |  |

|   | 1     | External CI capacitor for channel 2 connected    |       |  |  |

Table 34: Enable external capacitor channel 2

The regulator is offset compensated in order to prevent optical power drifts. Offset compensation can be disabled by setting register bit EOCx to 0.

Rev B1, Page 19/45

| EOC1 | Addr. 0x10; bit 4                  | R/W 1          |

|------|------------------------------------|----------------|

| 0    | Channel 1 regulator offset compens | ation disabled |

| 1    | Channel 1 regulator offset compens | ation enabled  |

Table 35: Enable offset compensation channel 1

| EOC2 | Addr. 0x15; bit 4                     | R/W 1       |

|------|---------------------------------------|-------------|

| 0    | Channel 2 regulator offset compensati | on disabled |

| 1    | Channel 2 regulator offset compensati | on enabled  |

Table 36: Enable offset compensation channel 2

An internal oscillator is used for the offset compensation. A watchdog timer (WDT) is included in order to monitor proper function of the oscillator. If an error is detected by the WDT, the laser channels are disabled, OSCERR error bit is set in STATUSO register and the error event is signaled at pin NCHK. This error signaling can be suppressed using the mask register bit MOSCERR (set to 1).

| MOSCERR | Addr. 0x1D; bit 0                                   | R/W 0   |

|---------|-----------------------------------------------------|---------|

| 0       | Oscillator error (watchdog) will be signaled NCHK   | l at    |

| 1       | Oscillator error (watchdog) will not be signal NCHK | aled at |

Table 37: Oscillator error mask

iC-HT monitors the saturation voltage of the regulator's output transistor at pin LDKx. The LDK saturation threshold can be configured through register bits RLDKSx.

| RLDKS1 | Addr. 0x13; bit 3:2                    | R/W 00 |

|--------|----------------------------------------|--------|

| 00     | V(LDK1) < 0.5 V sets the LDKSAT1 alarm |        |

| 01     | V(LDK1) < 0.8 V sets the LDKSAT1 alarm |        |

| 10     | V(LDK1) < 1.0 V sets the LDKSAT1 alarm | n bit  |

| 11     | V(LDK1) < 1.2 V sets the LDKSAT1 alarm | n bit  |

Table 38: LDK saturation threshold selection channel 1

| RLDKS2 | Addr. 0x18; bit 3:2                    | R/W 00 |

|--------|----------------------------------------|--------|

| 00     | V(LDK2) < 0.5 V sets the LDKSAT2 alarm |        |

| 01     | V(LDK2) < 0.8 V sets the LDKSAT2 alarm | bit    |

| 10     | V(LDK2) < 1.0 V sets the LDKSAT2 alarm | bit    |

| 11     | V(LDK2) < 1.2 V sets the LDKSAT2 alarm | bit    |

Table 39: LDK saturation threshold selection channel

If the LDKx voltage falls below the LDK saturation threshold the LDKSATx error bit in STATUS1 register will be set and it will be signaled through output pin NCHK. Setting the mask register bit MLDKSATx to 1 suppresses the signaling at NCHK.

| MLDKSAT1 Addr. 0x1D; bit 2 |                                            | R/W 1 |  |  |

|----------------------------|--------------------------------------------|-------|--|--|

| 0                          | LDKSAT1 event will be signaled at NCHK     |       |  |  |

| 1                          | LDKSAT1 event will not be signaled at NCHK |       |  |  |

Table 40: LDK saturation mask channel 1

| MLDKSAT2                                 | Addr. 0x1D; bit 3                          | R/W 1 |

|------------------------------------------|--------------------------------------------|-------|

| 0 LDKSAT2 event will be signaled at NCHK |                                            |       |

| 1                                        | LDKSAT2 event will not be signaled at NCHK |       |

Table 41: LDK saturation mask channel 2

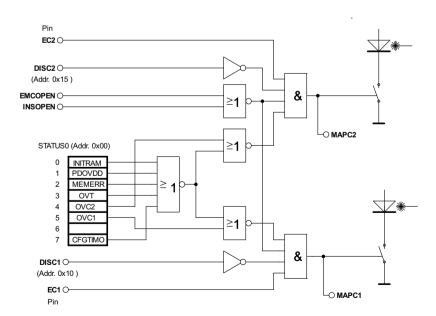

#### Laser channel enabling and error handling

With pin INS/WKR or EMC unconnected, a corresponding error signal will be generated (INSOPEN, EMCOPEN) and will disable the laser channels. Any input interface could be enabled if EMC or INS pins are open. Comunication with the chip might be possible but laser cannot be switched on. This situation is only signaled at the MCU interruption pin NCHK, which would remain low as long as any of the EMC or INS pins are unconnected. MCU must monitor the status of the NCHK pin to get all the status information of the chip

Setting DISC1 and DISC2 to 1(default) disables the corresponding channel.

The errors in STATUS0 and STATUS1 registers disable the laser channels. Every change in the STATUS registers is signaled at pin NCHK, unless the error event is masked by the corresponding error mask bit.

Rev B1, Page 20/45

| Register | Address | Bits | Default | Description                                       |

|----------|---------|------|---------|---------------------------------------------------|

| INITRAM  | 0x00    | 0    | R/O     | RAM initialized.                                  |

| PDOVDD   | 0x00    | 1    | R/O     | Power down event at VDD                           |

| MEMERR   | 0x00    | 2    | R/O     | RAM memory validation error                       |

| OVT      | 0x00    | 3    | R/O     | Overtemperature event                             |

| OVC2     | 0x00    | 4    | R/O     | Overcurrent at channel 2                          |

| OVC1     | 0x00    | 5    | R/O     | Overcurrent at channel 1                          |

| OSCERR   | 0x00    | 6    | R/O     | Oscillator error (watchdog set)                   |