# **S-19519 Series**

www.ablic.com

# AUTOMOTIVE, 125°C OPERATION, 36 V INPUT, 500 mA, BUILT-IN WINDOW WATCHDOG TIMER VOLTAGE REGULATOR WITH RESET FUNCTION

© ABLIC Inc., 2020-2021 Rev.2.0\_00

The S-19519 Series, developed by using high-withstand voltage CMOS technology, is a low dropout positive voltage regulator with the window watchdog timer and the reset function, which has high-withstand voltage. The monitoring time of watchdog timer can be adjusted by an external capacitor. Moreover, a voltage detection circuit which monitors the output voltage is also prepared.

ABLIC Inc. offers a "thermal simulation service" which supports the thermal design in conditions when our power management ICs are in use by customers. Our thermal simulation service will contribute to reducing the risk in the thermal design at customers' development stage.

ABLIC Inc. also offers FIT rate calculated based on actual customer usage conditions in order to support customer functional safety design.

Contact our sales representatives for details.

Caution This product can be used in vehicle equipment and in-vehicle equipment. Before using the product for these purposes, it is imperative to contact our sales representatives.

#### ■ Features

### Regulator block

Output voltage: 3.3 V, 5.0 VInput voltage: 3.0 V to 36.0 V

• Output voltage accuracy:  $\pm 2.0\%$  (T<sub>i</sub> = -40°C to +150°C)

Dropout voltage: 100 mV typ. (5.0 V output product, l<sub>OUT</sub> = 100 mA)

Output current: Possible to output 500 mA (V<sub>IN</sub> = V<sub>OUT(S)</sub> + 1.0 V)\*1

Input and output capacitors: A ceramic capacitor of 1.0 μF or more can be used.

Built-in overcurrent protection circuit: Limits overcurrent of output transistor.

Built-in thermal shutdown circuit: Detection temperature 170°C typ.

Built-in ON / OFF circuit:

Ensures long battery life.

#### **Detector block**

• Detection voltage: 2.6 V to 4.7 V, selectable in 0.1 V step

• Detection voltage accuracy:  $\pm 2.0\%$  (T<sub>j</sub> = -40°C to +150°C)

• Hysteresis width: 0.12 V min.

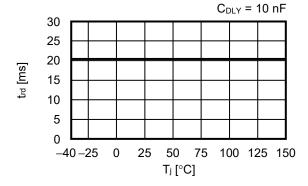

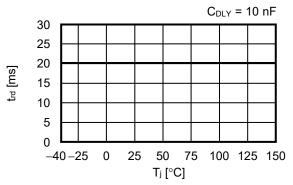

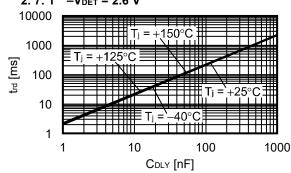

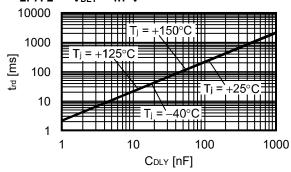

• Release delay time is adjustable\*2: 20 ms typ. (C<sub>DLY</sub> = 10 nF)

### Watchdog timer block

Watchdog activation current:

Watchdog trigger time is adjustable\*2:

46 ms typ. (CDLY = 10 nF)

• Product type is selectable: S-19519A Series

(TO-252-9S package product, HSOP-8A package product)

S-19519B Series (HTSSOP-16 package product)

• Autonomous watchdog operation function: Watchdog timer operates due to detection of load current.

Watchdog mode:

Window mode

#### Overall

• Current consumption: 3.2 μA typ. (During regulator operation, during watchdog timer deactivation)

0.1 μA typ. (During regulator stop)

• Operation temperature range: Ta = -40°C to +125°C

• Lead-free (Sn 100%), halogen-free

- Withstand 45 V load dump

- AEC-Q100 qualified\*3

- \*1. Please make sure that the loss of the IC will not exceed the power dissipation when the output current is large.

- \*2. The release delay time and the watchdog trigger time can be adjusted by connecting C<sub>DLY</sub> to the DLY pin.

- \*3. Contact our sales representatives for details.

### Applications

• Constant-voltage power supply for automotive electric component, monitoring of microcontroller

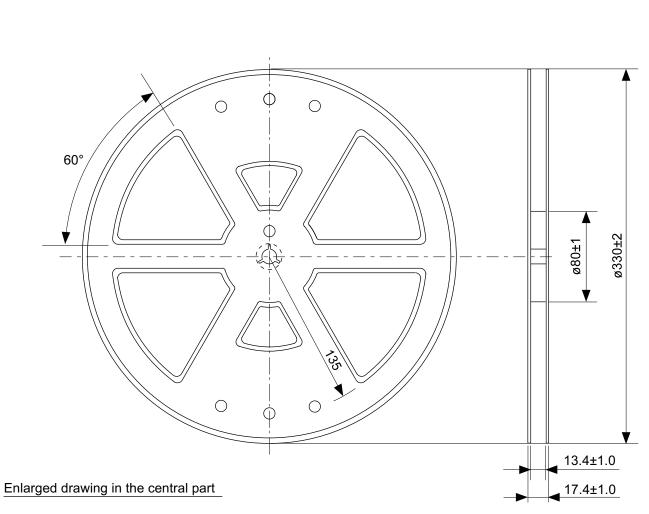

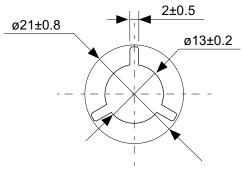

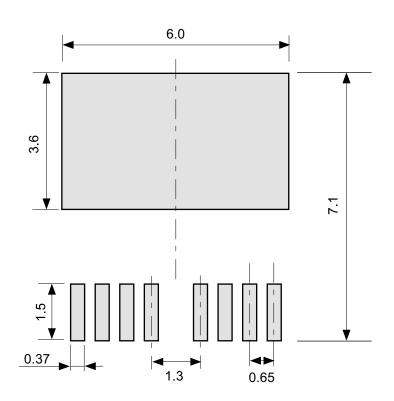

### ■ Packages

- TO-252-9S

- HSOP-8A

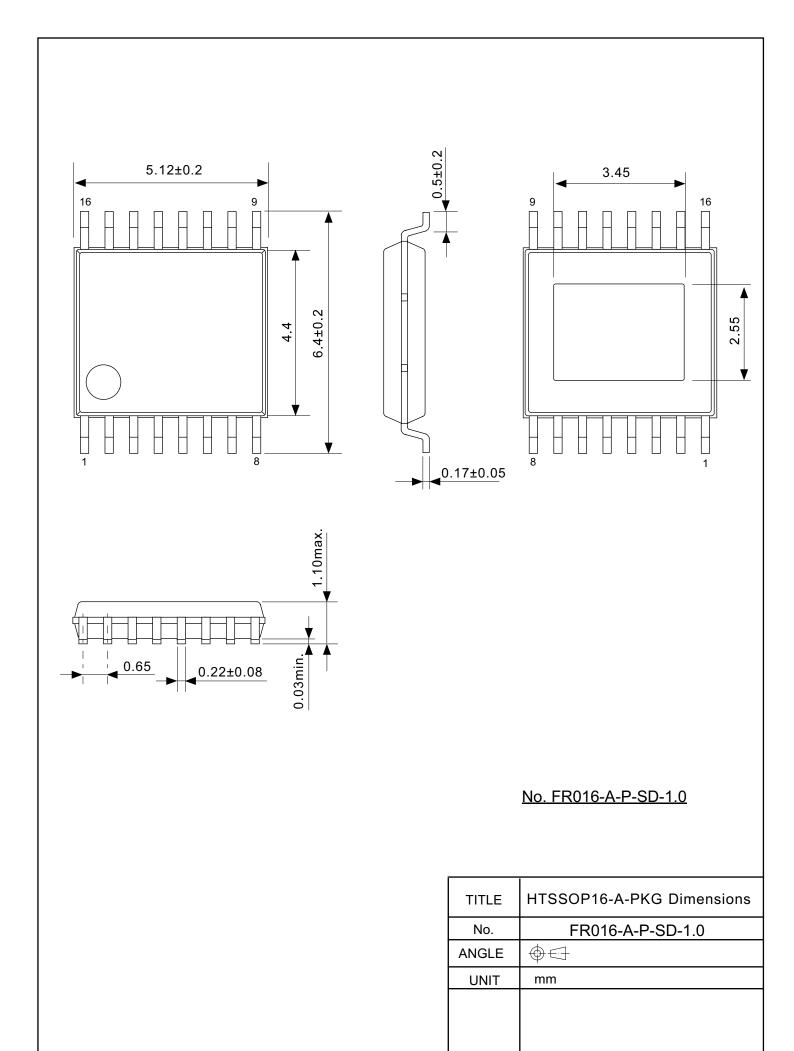

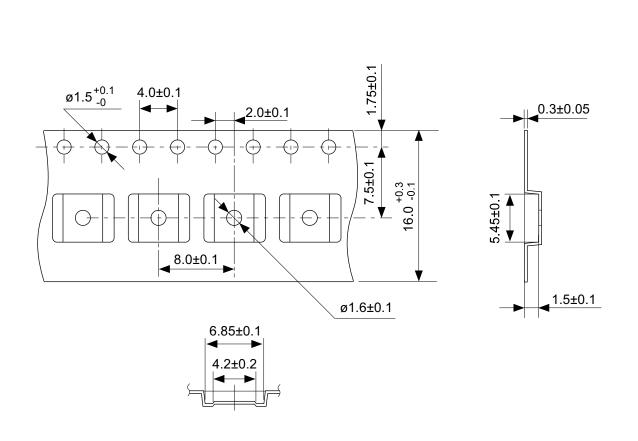

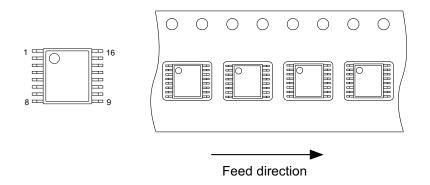

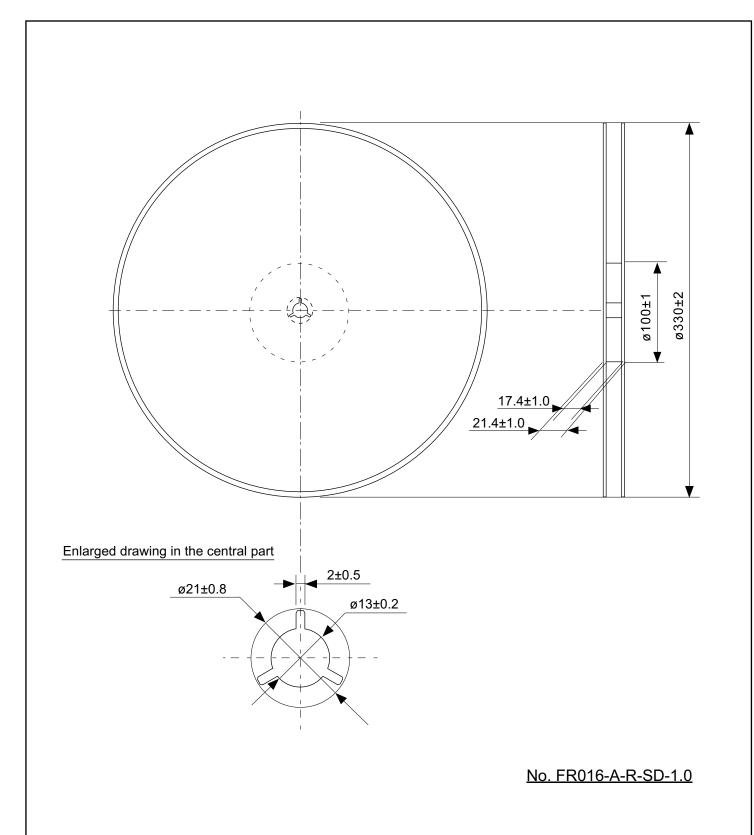

- HTSSOP-16

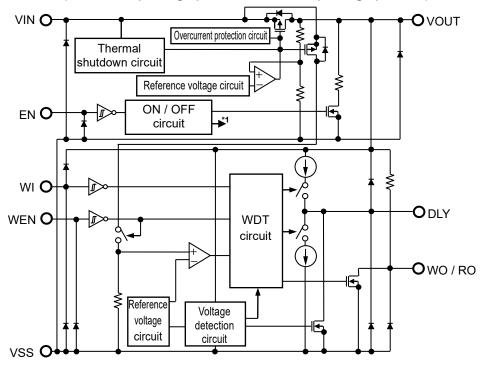

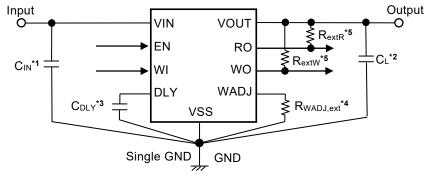

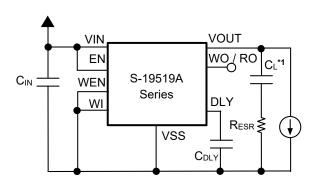

# ■ Block Diagrams

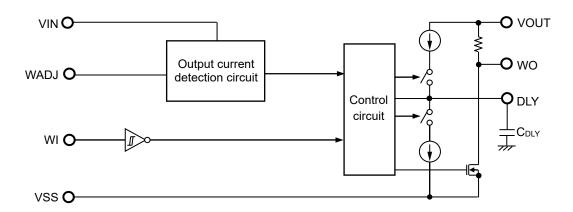

1. S-19519A Series (TO-252-9S package product, HSOP-8A package product)

\*1. The ON / OFF circuit controls the internal circuit and the output transistor.

Figure 1

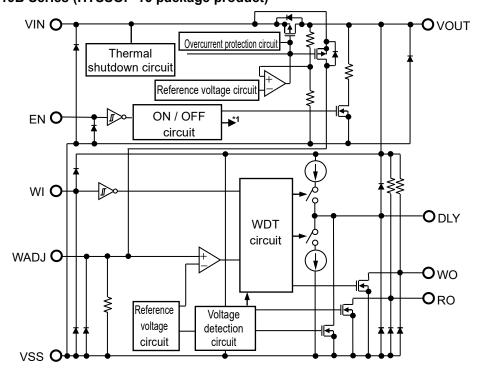

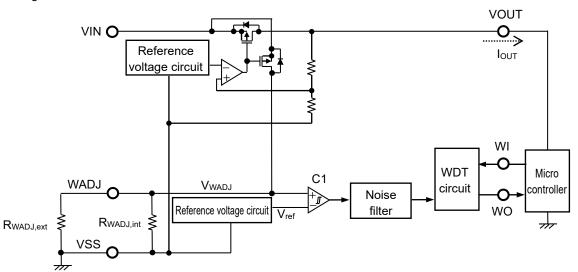

# 2. S-19519B Series (HTSSOP-16 package product)

\*1. The ON / OFF circuit controls the internal circuit and the output transistor.

Figure 2

# ■ AEC-Q100 Qualified

This IC supports AEC-Q100 for the operation temperature grade 1. Contact our sales representatives for details of AEC-Q100 reliability specification.

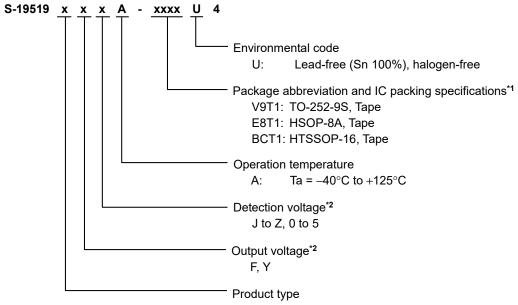

#### ■ Product Name Structure

#### 1. Product name

- A: S-19519A Series

- (TO-252-9S package product, HSOP-8A package product)

- B: S-19519B Series

- (HTSSOP-16 package product)

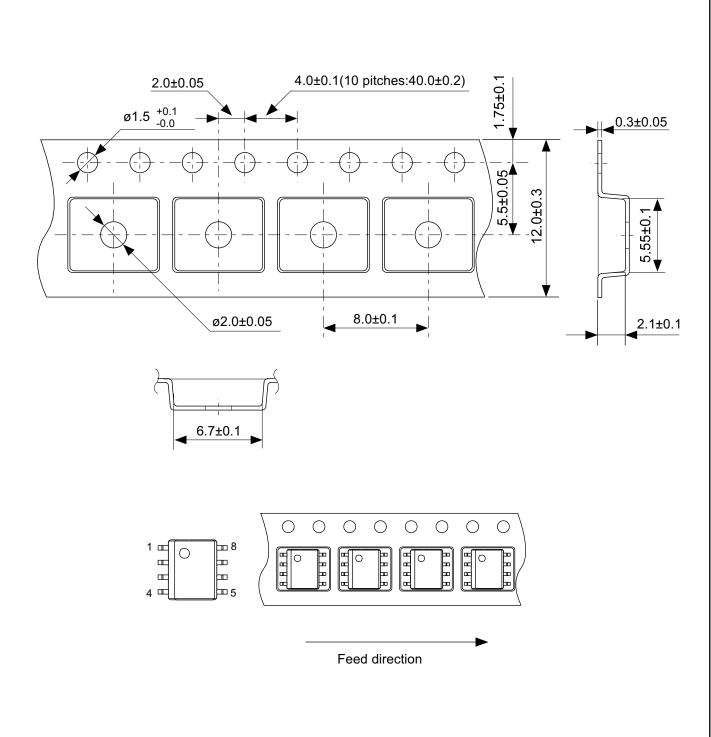

- \*1. Refer to the tape drawing.

- \*2. Refer to "2. Product option list".

# 2. Product option list

Table 1 Output Voltage

| Set Output<br>Voltage | Symbol |

|-----------------------|--------|

| 5.0 V                 | F      |

| 3.3 V                 | Υ      |

Table 2 Detection Voltage

| Set Detection<br>Voltage | Symbol |   |

|--------------------------|--------|---|

| 4.7 V                    | J      |   |

| 4.6 V                    | K      |   |

| 4.5 V                    | L      |   |

| 4.4 V                    | M      |   |

| 4.3 V                    | N      |   |

| 4.2 V                    | Р      |   |

| 4.1 V                    | Q      |   |

| 4.0 V                    | R      |   |

| 3.9 V                    | S      |   |

| 3.8 V                    | Т      |   |

| 3.7 V                    | U      |   |

|                          |        | _ |

| Set Detection<br>Voltage | Symbol |

|--------------------------|--------|

| 3.6 V                    | V      |

| 3.5 V                    | W      |

| 3.4 V                    | Х      |

| 3.3 V                    | Υ      |

| 3.2 V                    | Z      |

| 3.1 V                    | 0      |

| 3.0 V                    | 1      |

| 2.9 V                    | 2      |

| 2.8 V                    | 3      |

| 2.7 V                    | 4      |

| 26 V                     | 5      |

**Remark** Set output voltage ≥ Set detection voltage + 0.3 V

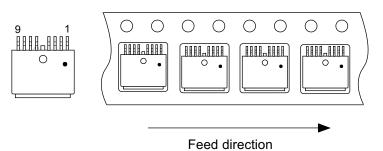

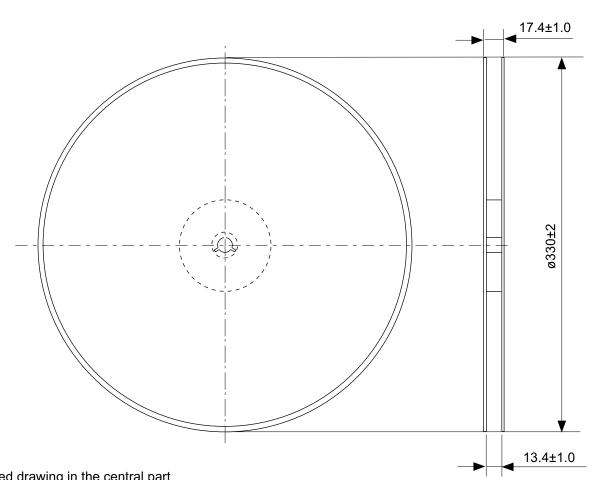

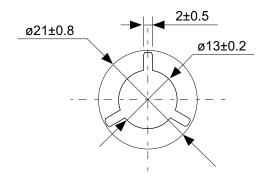

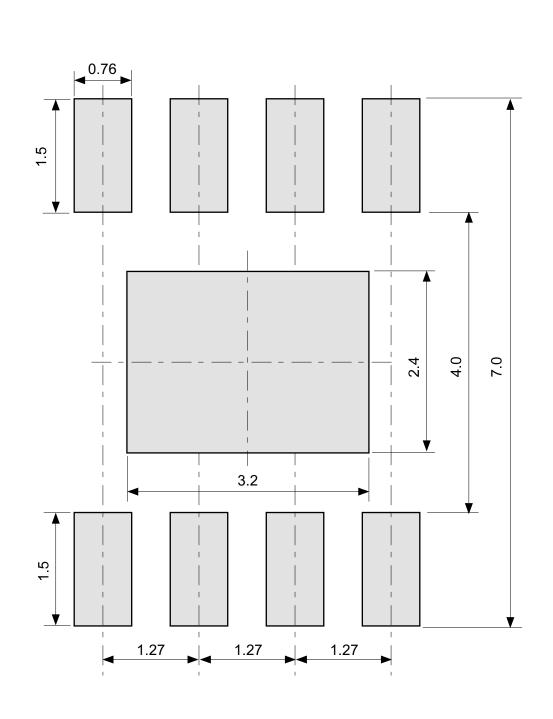

### 3. Packages

**Table 3 Package Drawing Codes**

| Package Name | Dimension Tape |              | Reel         | Land         |

|--------------|----------------|--------------|--------------|--------------|

| TO-252-9S    | VA009-A-P-SD   | VA009-A-C-SD | VA009-A-R-SD | VA009-A-L-SD |

| HSOP-8A      | FH008-A-P-SD   | FH008-A-C-SD | FH008-A-R-SD | FH008-A-L-SD |

| HTSSOP-16    | FR016-A-P-SD   | FR016-A-C-SD | FR016-A-R-SD | FR016-A-L-SD |

### 4. Product name list

# 4. 1 S-19519A Series (TO-252-9S package product, HSOP-8A package product)

Table 4

| Output Voltage (Vоит) | Detection Voltage (-VDET) | TO-252-9S          | HSOP-8A            |

|-----------------------|---------------------------|--------------------|--------------------|

| 3.3 V ± 2.0%          | 2.8 V ± 2.0%              | S-19519AY3A-V9T1U4 | S-19519AY3A-E8T1U4 |

| 3.3 V ± 2.0%          | 2.9 V ± 2.0%              | S-19519AY2A-V9T1U4 | S-19519AY2A-E8T1U4 |

| 3.3 V ± 2.0%          | 3.0 V ± 2.0%              | S-19519AY1A-V9T1U4 | S-19519AY1A-E8T1U4 |

| 5.0 V ± 2.0%          | 4.2 V ± 2.0%              | S-19519AFPA-V9T1U4 | S-19519AFPA-E8T1U4 |

| 5.0 V ± 2.0%          | 4.6 V ± 2.0%              | S-19519AFKA-V9T1U4 | S-19519AFKA-E8T1U4 |

| 5.0 V ± 2.0%          | 4.7 V ± 2.0%              | S-19519AFJA-V9T1U4 | S-19519AFJA-E8T1U4 |

**Remark** Please contact our sales representatives for products other than the above.

### 4. 2 S-19519B Series (HTSSOP-16 package product)

Table 5

| Output Voltage (Vоит) | Detection Voltage (-V <sub>DET</sub> ) | HTSSOP-16          |

|-----------------------|----------------------------------------|--------------------|

| $3.3~V \pm 2.0\%$     | 2.8 V ± 2.0%                           | S-19519BY3A-BCT1U4 |

| $3.3~V\pm2.0\%$       | 2.9 V ± 2.0%                           | S-19519BY2A-BCT1U4 |

| $3.3~V\pm2.0\%$       | 3.0 V ± 2.0%                           | S-19519BY1A-BCT1U4 |

| 5.0 V ± 2.0%          | 4.2 V ± 2.0%                           | S-19519BFPA-BCT1U4 |

| 5.0 V ± 2.0%          | 4.6 V ± 2.0%                           | S-19519BFKA-BCT1U4 |

| 5.0 V ± 2.0%          | 4.7 V ± 2.0%                           | S-19519BFJA-BCT1U4 |

**Remark** Please contact our sales representatives for products other than the above.

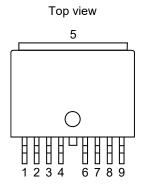

# ■ Pin Configurations

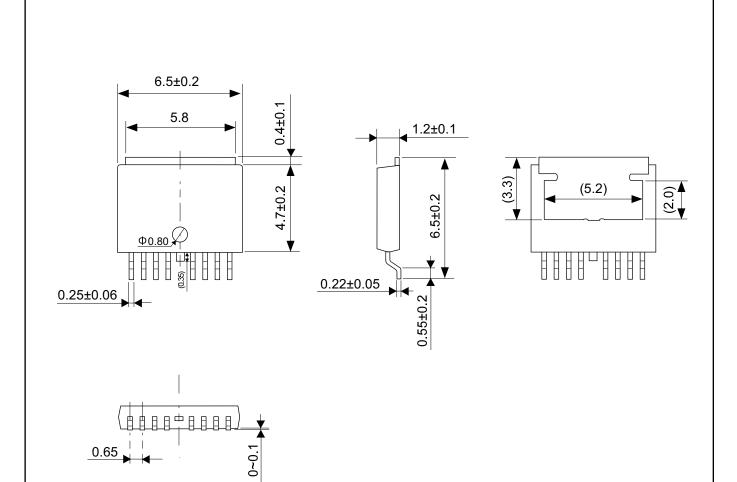

### 1. TO-252-9S

Figure 3

Pin No. Description Symbol 1 **VOUT** Voltage output pin (Regulator block) 2 WEN Watchdog enable pin Connection pin for release delay time and 3 DLY monitoring time adjustment capacitor NC\*1 4 No connection 5 VSS GND pin Watchdog output pin WO 6 WO / RO\*2 RO Reset output pin 7 WI Watchdog input pin 8 ΕN Enable pin

Voltage input pin (Regulator block)

Table 6 S-19519A Series

- **\*1.** The NC pin is electrically open.

- The NC pin can be connected to the VIN pin or the VSS pin.

- \*2. The WO / RO pin combines the watchdog output pin and the reset output pin.

9

VIN

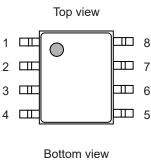

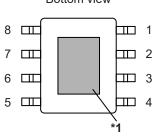

### 2. HSOP-8A

Table 7 S-19519A Series

| 14510 7 6 100 104 601100 |            |                                                                                |                                      |  |  |  |  |

|--------------------------|------------|--------------------------------------------------------------------------------|--------------------------------------|--|--|--|--|

| Pin No.                  | Symbol     | Description                                                                    |                                      |  |  |  |  |

| 1                        | VOUT       | Voltage output p                                                               | Voltage output pin (Regulator block) |  |  |  |  |

| 2                        | WEN        | Watchdog enab                                                                  | le pin                               |  |  |  |  |

| 3                        | VSS        | GND pin                                                                        |                                      |  |  |  |  |

| 4                        | DLY        | Connection pin for release delay time and monitoring time adjustment capacitor |                                      |  |  |  |  |

| F                        | NAC / DO*2 | WO                                                                             | Watchdog output pin                  |  |  |  |  |

| 5                        | WO / RO*2  | RO Reset output pin                                                            |                                      |  |  |  |  |

| 6                        | WI         | Watchdog input pin                                                             |                                      |  |  |  |  |

| 7                        | EN         | Enable pin                                                                     |                                      |  |  |  |  |

| 8                        | VIN        | Voltage input pir                                                              | n (Regulator block)                  |  |  |  |  |

Figure 4

- **\*1.** Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2. The WO / RO pin combines the watchdog output pin and the reset output pin.

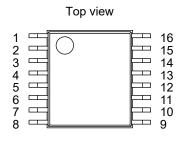

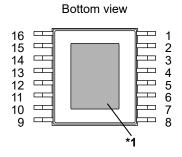

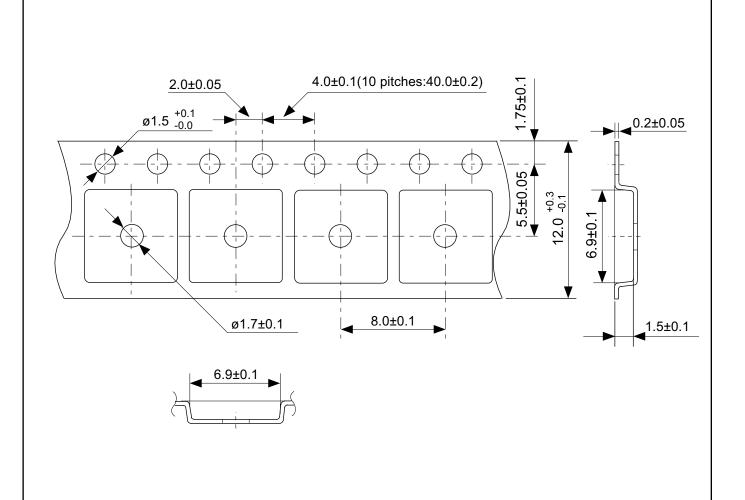

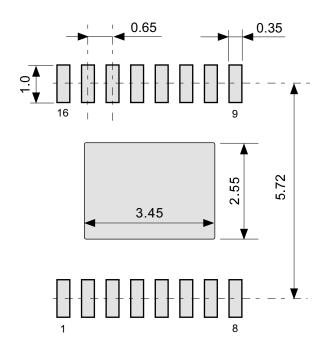

#### 3. HTSSOP-16

Figure 5

Table 8 S-19519B Series

| Pin No. | Symbol | Description                               |  |  |  |

|---------|--------|-------------------------------------------|--|--|--|

| 1       | VOUT   | Voltage output pin (Regulator block)      |  |  |  |

| 2       | VOUT   | Voltage output pin (Regulator block)      |  |  |  |

| 3       | NC*2   | No connection                             |  |  |  |

| 4       | MADI   | Connection pin for watchdog activation    |  |  |  |

| 4       | WADJ   | threshold current adjustment resistor     |  |  |  |

| 5       | NC*2   | No connection                             |  |  |  |

| 6       | VSS    | GND pin                                   |  |  |  |

| 7       | NC*2   | No connection                             |  |  |  |

| 0 51.7  |        | Connection pin for release delay time and |  |  |  |

| 8       | DLY    | monitoring time adjustment capacitor      |  |  |  |

| 9       | RO     | Reset output pin                          |  |  |  |

| 10      | WO     | Watchdog output pin                       |  |  |  |

| 11      | NC*2   | No connection                             |  |  |  |

| 12      | WI     | Watchdog input pin                        |  |  |  |

| 13      | NC*2   | No connection                             |  |  |  |

| 14      | EN     | Enable pin                                |  |  |  |

| 15      | VIN    | Voltage input pin (Regulator block)       |  |  |  |

| 16      | VIN    | Voltage input pin (Regulator block)       |  |  |  |

- **\*1.** Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2. The NC pin is electrically open.

The NC pin can be connected to the VIN pin or the VSS pin.

# ■ Absolute Maximum Ratings

Table 9

$(T_j = -40^{\circ}C \text{ to } +150^{\circ}C \text{ unless otherwise specified})$

| Item                             | Symbol               | Absolute Maximum Rating                                  | Unit |

|----------------------------------|----------------------|----------------------------------------------------------|------|

| VIN pin voltage                  | V <sub>IN</sub>      | $V_{SS} - 0.3$ to $V_{SS} + 45.0$                        | V    |

| EN pin voltage                   | V <sub>EN</sub>      | $V_{SS} - 0.3 \text{ to } V_{SS} + 45.0$                 | V    |

| VOUT pin voltage                 | Vouт                 | $V_{SS} - 0.3 \text{ to } V_{IN} + 0.3 \le V_{SS} + 7.0$ | V    |

| DLY pin voltage                  | V <sub>DLY</sub>     | $V_{SS} - 0.3$ to $V_{OUT} + 0.3 \le V_{SS} + 7.0$       | V    |

| RO pin voltage                   | V <sub>RO</sub>      | $V_{SS} - 0.3$ to $V_{OUT} + 0.3 \le V_{SS} + 7.0$       | V    |

| WADJ pin voltage                 | V <sub>WADJ</sub>    | $V_{SS} - 0.3 \text{ to } V_{IN} + 0.3 \le V_{SS} + 7.0$ | V    |

| WEN pin voltage V <sub>WEN</sub> |                      | $V_{SS} - 0.3$ to $V_{SS} + 7.0$                         | V    |

| WI pin voltage                   | Vwi                  | $V_{SS} - 0.3$ to $V_{OUT} + 0.3 \le V_{SS} + 7.0$       | V    |

| WO pin voltage                   | Vwo                  | $V_{SS} - 0.3$ to $V_{OUT} + 0.3 \le V_{SS} + 7.0$       | V    |

| WO / RO pin voltage              | V <sub>WO / RO</sub> | $V_{SS} - 0.3$ to $V_{OUT} + 0.3 \le V_{SS} + 7.0$       | V    |

|                                  | Гоит                 | 650                                                      | mA   |

| 0.44                             | I <sub>RO</sub>      | 30                                                       | mA   |

| Output current                   | Iwo                  | 30                                                       | mA   |

|                                  | I <sub>WO / RO</sub> | 30                                                       | mA   |

| Junction temperature             | Tj                   | -40 to +150                                              | °C   |

| Operation ambient temperature    | T <sub>opr</sub>     | -40 to +125                                              | °C   |

| Storage temperature              | T <sub>stg</sub>     | -40 to +150                                              | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

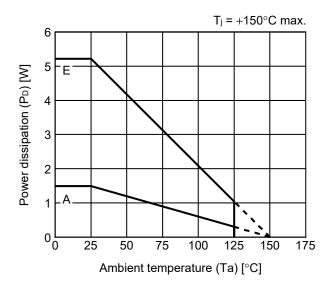

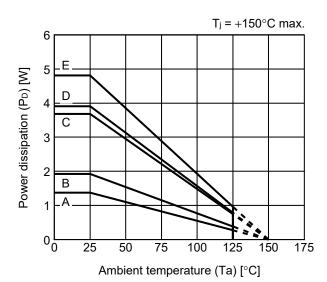

### **■** Thermal Resistance Value

Table 10

| Item                                         | Symbol        | Cond      | dition  | Min. | Тур. | Max. | Unit |

|----------------------------------------------|---------------|-----------|---------|------|------|------|------|

|                                              |               |           | Board A | _    | 84   | _    | °C/W |

|                                              |               |           | Board B | 1    | _    | _    | °C/W |

|                                              |               | TO-252-9S | Board C | 1    | _    | _    | °C/W |

|                                              |               |           | Board D | 1    | _    | _    | °C/W |

|                                              |               |           | Board E | -    | 24   | _    | °C/W |

|                                              | $\theta_{JA}$ | HSOP-8A   | Board A | _    | 105  | -    | °C/W |

|                                              |               |           | Board B | _    | _    | _    | °C/W |

| Junction-to-ambient thermal resistance*1, *2 |               |           | Board C | _    | _    | _    | °C/W |

|                                              |               |           | Board D | 1    | _    | _    | °C/W |

|                                              |               |           | Board E | 1    | 31   | _    | °C/W |

|                                              |               | HTSSOP-16 | Board A | _    | 91   | _    | °C/W |

|                                              |               |           | Board B | _    | 65   | _    | °C/W |

|                                              |               |           | Board C | _    | 34   | _    | °C/W |

|                                              |               |           | Board D | ı    | 32   | _    | °C/W |

|                                              |               |           | Board E | _    | 26   | _    | °C/W |

<sup>\*1.</sup> Test environment: compliance with JEDEC STANDARD JESD51-2A

Remark Refer to "■ Power Dissipation" and "Test Board" for details.

<sup>\*2.</sup> Measurement values when this IC is mounted on each board

# **■** Recommended Operation Conditions

Table 11

| Item                                                            | Symbol            | Cond                                     | ition                    | Min.                      | Тур. | Max.     | Unit |

|-----------------------------------------------------------------|-------------------|------------------------------------------|--------------------------|---------------------------|------|----------|------|

|                                                                 |                   | _                                        |                          | 3.0                       | _    | 36.0     | V    |

| VIN pin voltage                                                 | Vin               | Autonomous watchdog operation function*1 |                          | V <sub>OUT(S)</sub> + 1.0 | -    | 36.0     | V    |

| EN pin voltage                                                  | V <sub>EN</sub>   | _                                        |                          | 0                         | _    | $V_{IN}$ | V    |

| WEN pin voltage                                                 | V <sub>WEN</sub>  | S-19519A Series                          | S                        | 0                         | _    | Vout     | V    |

| WI pin voltage                                                  | V <sub>WI</sub>   | _                                        |                          | 0                         | _    | Vout     | V    |

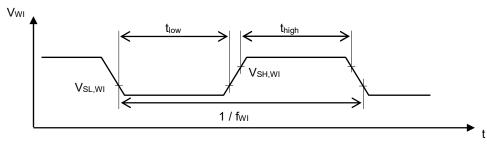

| Watchdog input "H" time*2                                       | thigh             | _                                        |                          | 5.0                       | _    | ı        | μs   |

| Watchdog input "L" time*2                                       | t <sub>low</sub>  | _                                        |                          | 5.0                       | _    | -        | μs   |

| Watchdog input frequency*2                                      | fwı               | Duty ratio 50%                           |                          | _                         | _    | 0.2      | MHz  |

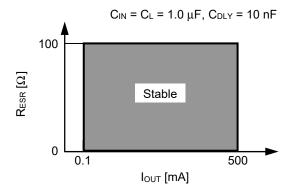

| Input capacitance                                               | CIN               | _                                        |                          | 1.0                       | _    | -        | μF   |

| Output capacitance                                              | CL                | _                                        |                          | 1.0                       | _    | -        | μF   |

| Equivalent series resistance                                    | Resr              | Output capacitor                         | r (C <sub>L</sub> )      | _                         | _    | 100      | Ω    |

| Release delay time and monitoring time adjustment capacitance*3 | C <sub>DLY</sub>  | _                                        |                          | 1                         | 10   | ı        | nF   |

| Watchdog activation threshold current adjustment resistance*4   | RWADJ,ext         | S-19519B Series                          | •                        | 10                        | 1    | 1        | kΩ   |

|                                                                 | R <sub>extW</sub> | S-19519B Series                          | Connected to WO pin      | 3                         | 1    | -        | kΩ   |

| External pull-up resistance for output pin                      | D -               | S-19519A Series                          | Connected to WO / RO pin | 3                         | _    | _        | kΩ   |

|                                                                 | R <sub>extR</sub> | S-19519B Series                          | Connected to RO pin      | 3                         | _    | -        | kΩ   |

- \*1. Refer to "3. Watchdog timer block" in "■ Operation" for the autonomous watchdog operation function.

- \*2. When inputting a rising edge that satisfies the condition of **Figure 6** to the WI pin, the watchdog timer detects a trigger.

- The signal input from the monitored object by the watchdog timer should satisfy the condition of Figure 6.

- \*3. Refer to "2. Release delay time and monitoring time adjustment capacitor (C<sub>DLY</sub>)" in "■ Selection of External Parts" for the details.

- \*4. Refer to "3. Watchdog activation threshold current adjustment resistor (R<sub>WADJ,ext</sub>)" in "■ Selection of External Parts" for the details.

Figure 6

Caution Generally a series regulator may cause oscillation, depending on the selection of external parts. Confirm that no oscillation occurs in the actual application using capacitors that meet the above C<sub>IN</sub>, C<sub>L</sub>, and R<sub>ESR</sub>.

### **■** Electrical Characteristics

### 1. Regulator block

Table 12

( $V_{IN}$  = 13.5 V,  $T_j$  = -40°C to +150°C unless otherwise specified)

| Item                                   | Symbol                                                                       | Cond                                                                                                | lition                       | Min.                       | Тур.                | Max.                       | Unit | Test<br>Circuit |

|----------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------|----------------------------|---------------------|----------------------------|------|-----------------|

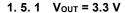

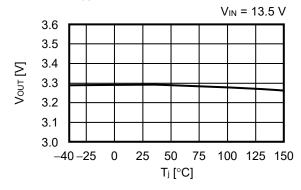

| Output voltage*1                       | V <sub>OUT(E)</sub>                                                          | $V_{OUT(S)} + 1.0 \text{ V} \le V_{IN} \le 18.0 \text{ V},$<br>1 mA \le I <sub>OUT</sub> \le 100 mA |                              | V <sub>OUT(S)</sub> - 2.0% | V <sub>OUT(S)</sub> | V <sub>OUT(S)</sub> + 2.0% | ٧    | 1               |

| Output current*2                       | Гоит                                                                         | $V_{IN} \ge V_{OUT(S)} + 1.0$                                                                       | V                            | 500* <sup>7</sup>          | ı                   | _                          | mA   | 2               |

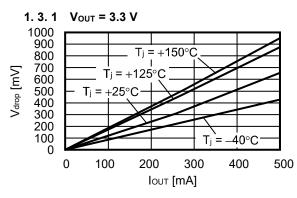

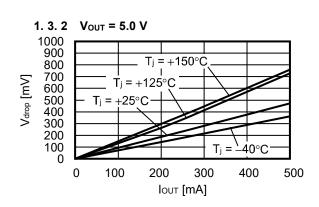

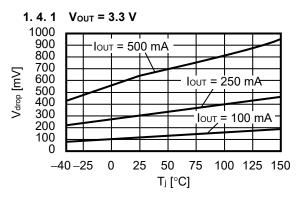

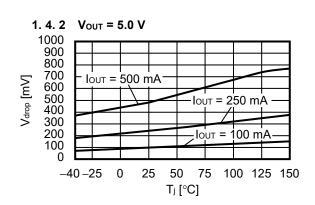

|                                        |                                                                              | - 100 m A                                                                                           | V <sub>OUT(S)</sub> = 3.3 V  | _                          | 120                 | 240                        | mV   | 1               |

| Decrease valle as *3                   |                                                                              | I <sub>OUT</sub> = 100 mA                                                                           | V <sub>OUT(S)</sub> = 5.0 V  | _                          | 100                 | 200                        | mV   | 1               |

| Dropout voltage*3                      | V <sub>drop</sub>                                                            | I - 500 A                                                                                           | V <sub>OUT(S)</sub> = 3.3 V  | _                          | 650                 | 1200                       | mV   | 1               |

|                                        |                                                                              | I <sub>ОUТ</sub> = 500 mA                                                                           | $V_{OUT(S)} = 5.0 \text{ V}$ | _                          | 510                 | 1000                       | mV   | 1               |

| Line regulation*4                      | $\frac{\Delta V_{\text{OUT1}}}{\Delta V_{\text{IN}} \bullet V_{\text{OUT}}}$ | $V_{OUT(S)} + 1.0 \text{ V} \le V_{IN} \le 36.0 \text{ V},$ $I_{OUT} = 1 \text{ mA}$                |                              | _                          | 0.01                | 0.02                       | %/V  | 1               |

| Load regulation*5                      | $\Delta V_{	ext{OUT2}}$                                                      | $V_{IN} = V_{OUT(S)} + 1.0 \text{ V},$<br>1 mA \leq I <sub>OUT</sub> \leq 250 mA, Ta = +25°C        |                              | _                          | 10                  | 50                         | mV   | 1               |

| Input voltage                          | Vin                                                                          | _                                                                                                   |                              | 3.0                        | _                   | 36.0                       | V    | _               |

| EN pin input voltage "H"               | V <sub>SH,EN</sub>                                                           | _                                                                                                   |                              | 2                          | ı                   | _                          | V    | 4               |

| EN pin input voltage "L"               | V <sub>SL,EN</sub>                                                           | _                                                                                                   | -                            | _                          | 1                   | 0.8                        | ٧    | 4               |

| EN pin input current "H"               | Ish,en                                                                       | V <sub>EN</sub> = V <sub>IN</sub>                                                                   |                              | _                          | 1                   | 1                          | μΑ   | 4               |

| EN pin input current "L"               | I <sub>SL,EN</sub>                                                           | $V_{EN} = 0 V$                                                                                      |                              | _                          | 1                   | 0.1                        | μΑ   | 4               |

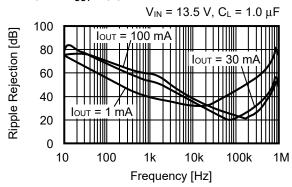

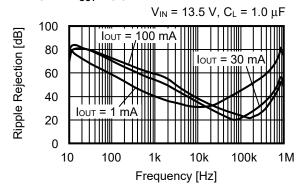

| Ripple rejection                       | RR                                                                           | V <sub>IN</sub> = 13.5 V,<br>I <sub>OUT</sub> = 30 mA,                                              | V <sub>OUT(S)</sub> = 3.3 V  | _                          | 65                  | -                          | dB   | 3               |

| ,                                      | ' '                                                                          | f = 100  Hz,<br>$\Delta V_{rip} = 1.0 \text{ V}_{p-p}$                                              | V <sub>OUT(S)</sub> = 5.0 V  | _                          | 60                  | _                          | dB   | 3               |

| Limit current*6                        | I <sub>LIM</sub>                                                             | $V_{IN} = V_{OUT(S)} + 1.0$                                                                         | V, Ta = +25°C                | 490                        | 700                 | 960                        | mA   | 2               |

| Short-circuit current                  | Ishort                                                                       | $V_{IN} = 13.5 \text{ V}, V_{OUT} = 0 \text{ V},$ $Ta = +25^{\circ}C$                               |                              | 75                         | 160                 | 245                        | mA   | 2               |

| Thermal shutdown detection temperature | T <sub>SD</sub>                                                              | Junction temperature                                                                                |                              | _                          | 170                 | -                          | °C   | _               |

| Thermal shutdown release temperature   | T <sub>SR</sub>                                                              | Junction temperat                                                                                   | ure                          | _                          | 135                 | _                          | °C   | _               |

<sup>\*1.</sup> The accuracy is guaranteed when the input voltage, output current, and temperature satisfy the conditions listed above.

$V_{OUT(S)}$ : Set output voltage  $V_{OUT(E)}$ : Actual output voltage

$V_{drop}$ :  $V_{IN1} - (V_{OUT3} \times 0.98)$

$V_{OUT3}$ : Output voltage when  $V_{IN} = V_{OUT(S)} + 1.0 \text{ V}$

- **\*4.** The dependency of the output voltage against the input voltage. The value shows how much the output voltage changes due to a change in the input voltage while keeping output current constant.

- \*5. The dependency of the output voltage against the output current. The value shows how much the output voltage changes due to a change in the output current while keeping input voltage constant.

- \*6. The current limited by overcurrent protection circuit.

- \*7. Due to limitation of the power dissipation, this value may not be satisfied. Attention should be paid to the power dissipation when the output current is large.

This specification is guaranteed by design.

<sup>\*2.</sup> The output current when increasing the output current gradually until the output voltage has reached the value of 95% of V<sub>OUT(E)</sub>.

<sup>\*3.</sup> The difference between input voltage (V<sub>IN1</sub>) and the output voltage when decreasing input voltage (V<sub>IN</sub>) gradually until the output voltage has dropped out to the value of 98% of output voltage (V<sub>OUT3</sub>).

#### 2. Detector block

Table 13

$(T_i = -40^{\circ}C \text{ to } +150^{\circ}C \text{ unless otherwise specified})$

|                          |                   |                                                                                                   | (1 <sub>1</sub> = -40 (        | 7 10 1 100           | o arriodo o                 | CITOT WIOO C | poomoa          |

|--------------------------|-------------------|---------------------------------------------------------------------------------------------------|--------------------------------|----------------------|-----------------------------|--------------|-----------------|

| Item                     | Symbol            | Condition                                                                                         | Min.                           | Тур.                 | Max.                        | Unit         | Test<br>Circuit |

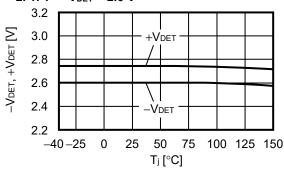

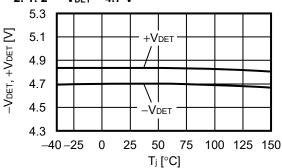

| Detection voltage*1      | -V <sub>DET</sub> | -                                                                                                 | -V <sub>DET(S)</sub><br>- 2.0% | -V <sub>DET(S)</sub> | -V <sub>DET(S)</sub> + 2.0% | V            | 5               |

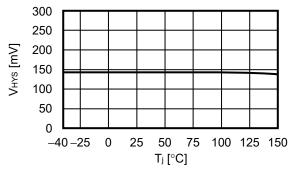

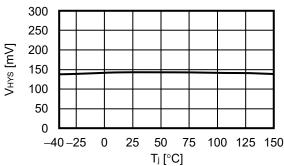

| Hysteresis width*2       | V <sub>HYS</sub>  | _                                                                                                 | 120                            | 150                  | 180                         | mV           | 5               |

| Reset output voltage "H" | V <sub>ROH</sub>  | -                                                                                                 | V <sub>OUT(S)</sub> × 0.9      | 1                    | -                           | <b>V</b>     | 5               |

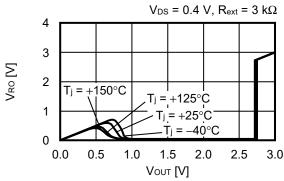

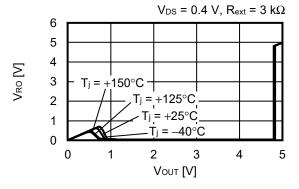

| Reset output voltage "L" | V <sub>ROL</sub>  | $V_{OUT} \ge 1.0 \text{ V}, \text{ R}_{\text{extR}} \ge 3 \text{ k}\Omega,$ Connected to VOUT pin | -                              | 0.2                  | 0.4                         | ٧            | 5               |

| Reset pull-up resistance | R <sub>RO</sub>   | VOUT pin internal resistance, $V_{OUT} \ge +V_{DET}$                                              | 20                             | 30                   | 45                          | kΩ           | -               |

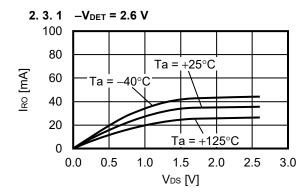

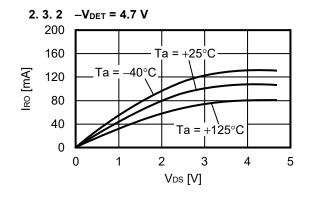

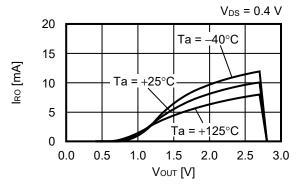

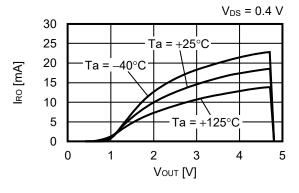

| Reset output current     | I <sub>RO</sub>   | $V_{RO} = 0.4 \text{ V}, V_{OUT} = -V_{DET(S)} \times 0.95$                                       | 3.0                            | I                    | _                           | mA           | 6               |

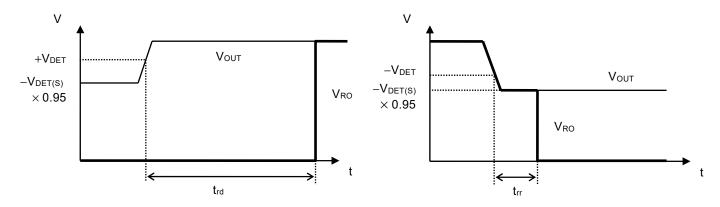

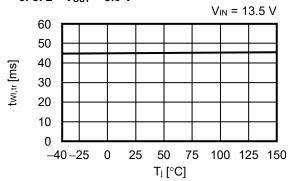

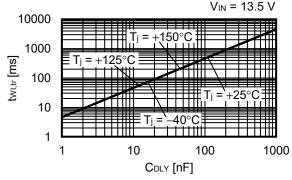

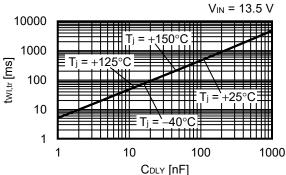

| Release delay time*3     | t <sub>rd</sub>   | C <sub>DLY</sub> = 10 nF                                                                          | 16                             | 20                   | 24                          | ms           | 5               |

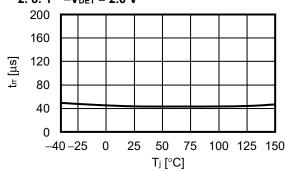

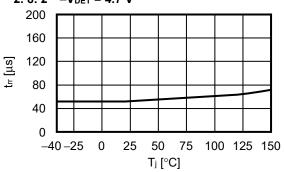

| Reset reaction time*4    | trr               | _                                                                                                 | _                              | _                    | 200                         | μs           | 5               |

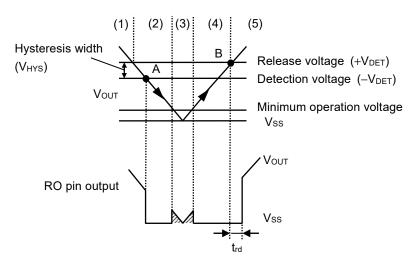

- \*1. The VOUT pin voltage at which the output of the RO pin switches from "H" to "L".

- -V<sub>DET(S)</sub>: Set detection voltage

- -V<sub>DET</sub>: Actual detection voltage

- \*2. The voltage difference between the detection voltage ( $-V_{DET}$ ) and the release voltage ( $+V_{DET}$ ). The relation between the actual output voltage ( $V_{OUT(E)}$ ) of the regulator block and the actual release voltage ( $+V_{DET} = -V_{DET} + V_{HYS}$ ) of the detector block is as follows.

$$V_{\text{OUT(E)}} > +V_{\text{DET}}$$

- \*3. The time from when V<sub>OUT</sub> exceeds +V<sub>DET</sub> to when the RO pin output inverts (Refer to Figure 7). This value changes according to the release delay time and monitoring time adjustment capacitor (C<sub>DLY</sub>).

- The time period from when  $V_{\text{OUT}}$  changes to  $+V_{\text{DET}} \rightarrow V_{\text{DET}(S)}$  to when  $V_{\text{RO}}$  reaches  $V_{\text{OUT}}$  / 2.

- \*4. The time from when V<sub>OUT</sub> falls below –V<sub>DET</sub> to when the RO pin output inverts (Refer to **Figure 8**). The time period from when V<sub>OUT</sub> changes to V<sub>OUT</sub>(S) → –V<sub>DET</sub> to when V<sub>RO</sub> reaches V<sub>OUT</sub> / 2.

Figure 7 Release Delay Time

Figure 8 Reset Reaction Time

### 3. Watchdog timer block

### 3. 1 S-19519A Series (TO-252-9S package product, HSOP-8A package product)

Table 14

( $V_{IN}$  = 13.5 V,  $T_j$  = -40°C to +150°C unless otherwise specified)

| Item                                    | Symbol                 | Condition                             | Min.                      | Тур. | Max.                    | Unit | Test<br>Circuit |

|-----------------------------------------|------------------------|---------------------------------------|---------------------------|------|-------------------------|------|-----------------|

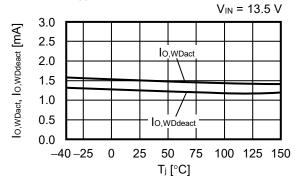

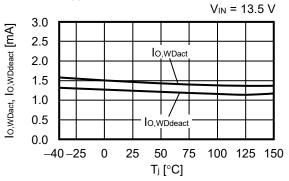

| Watchdog activation threshold current   | I <sub>O,WDact</sub>   | -                                     | 1.1                       | 1.5  | 1.9                     | mA   | 9               |

| Watchdog deactivation threshold current | I <sub>O,WDdeact</sub> | _                                     | 0.85                      | 1.25 | ı                       | mA   | 9               |

| WI pin input voltage "H"                | V <sub>SH,WI</sub>     | -                                     | V <sub>OUT(S)</sub> × 0.7 | -    | -                       | ٧    | 7               |

| WI pin input voltage "L"                | V <sub>SL,WI</sub>     | -                                     | _                         | ı    | $V_{OUT(S)} \times 0.3$ | ٧    | 7               |

| WI pin input current "H"                | I <sub>SH,WI</sub>     | V <sub>WI</sub> = V <sub>OUT(S)</sub> | _                         | _    | 1                       | μΑ   | 7               |

| WI pin input current "L"                | I <sub>SL,WI</sub>     | V <sub>WI</sub> = 0 V                 | _                         | Ì    | 0.1                     | μΑ   | 7               |

| WEN pin input voltage "H"               | V <sub>SH,WEN</sub>    | _                                     | 2                         | İ    | 1                       | V    | 8               |

| WEN pin input voltage "L"               | V <sub>SL,WEN</sub>    | _                                     | _                         | _    | 0.8                     | V    | 8               |

| WEN pin input curernt "H"               | I <sub>SH,WEN</sub>    | $V_{WEN} = V_{OUT(S)}$                | -                         | -    | 1                       | μΑ   | 8               |

| WEN pin input current "L"               | I <sub>SL,WEN</sub>    | V <sub>WEN</sub> = 0 V                | _                         | _    | 0.1                     | μΑ   | 8               |

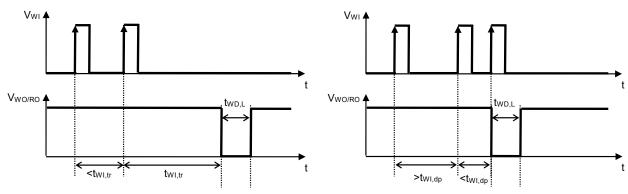

| Watchdog output "L" time*1              | t <sub>WD,L</sub>      | C <sub>DLY</sub> = 10 nF              | 9.2                       | 11.5 | 13.8                    | ms   | 9               |

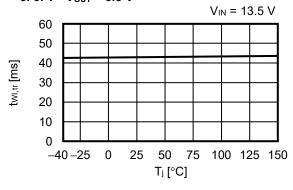

| Watchdog trigger time*2                 | t <sub>WI,tr</sub>     | C <sub>DLY</sub> = 10 nF              | 39.1                      | 46   | 52.9                    | ms   | 9               |

| Watchdog double-pulse detection time*3  | t <sub>WI,dp</sub>     | C <sub>DLY</sub> = 10 nF              | 9.2                       | 11.5 | 13.8                    | ms   | 9               |

<sup>\*1.</sup> The time when the WO / RO pin continues "L" after the watchdog timer detects a time-out or double-pulse (Refer to Figure 9). This value changes according to C<sub>DLY</sub>.

<sup>\*3.</sup> The time from when the watchdog timer initiates the detection of a trigger signal to when a trigger is detected again before twi,dp elapses and the WO / RO pin output changes to "L" (Refer to **Figure 10**). This value changes according to CDLY.

Figure 9 Watchdog Trigger Time

Figure 10 Watchdog Double-pulse Detection Time

<sup>\*2.</sup> The time from when the watchdog timer initiates the detection of a trigger signal to when a time-out is detected and the WO / RO pin output changes to "L" (Refer to **Figure 9**). This value changes according to C<sub>DLY</sub>.

### 3. 2 S-19519B Series (HTSSOP-16 package product)

#### Table 15

$(V_{IN} = 13.5 \text{ V}, T_j = -40^{\circ}\text{C to } +150^{\circ}\text{C unless otherwise specified})$

| Item                                    | Symbol                 | Condition                                                      | Min.                         | Тур. | Max.                      | Unit | Test<br>Circuit |

|-----------------------------------------|------------------------|----------------------------------------------------------------|------------------------------|------|---------------------------|------|-----------------|

| Watchdog activation threshold current   | I <sub>O,WDact</sub>   | WADJ pin is open                                               | 1.1                          | 1.5  | 1.9                       | mA   | 7               |

| Watchdog deactivation threshold current | I <sub>O,WDdeact</sub> | WADJ pin is open                                               | 0.85                         | 1.25 | _                         | mA   | 7               |

| Watchdog activation hysteresis current  | I <sub>O,WDhys</sub>   | WADJ pin is open                                               | 0.1                          | 0.25 | 0.4                       | mA   | 7               |

| Watchdog activation threshold voltage   | VwADJ,th               | -                                                              | 1.2                          | 1.25 | 1.33                      | V    | 8               |

| WADJ pin current ratio                  | IOUT<br>IWADJ          | V <sub>WADJ</sub> = 0 V, I <sub>OUT</sub> = 10 mA              | -                            | 1700 | -                         | -    | 8               |

| WADJ pin internal resistance            | R <sub>WADJ,int</sub>  | _                                                              | 1000                         | 1400 | 1800                      | kΩ   | _               |

| WI pin input voltage "H"                | V <sub>SH,WI</sub>     | _                                                              | V <sub>OUT(S)</sub> × 0.7    | -    | -                         | V    | 11              |

| WI pin input voltage "L"                | V <sub>SL,WI</sub>     | -                                                              | _                            | -    | V <sub>OUT(S)</sub> × 0.3 | V    | 11              |

| WI pin input current "H"                | I <sub>SH,WI</sub>     | V <sub>WI</sub> = V <sub>OUT(S)</sub>                          | =                            | _    | 1                         | μΑ   | 11              |

| WI pin input current "L"                | I <sub>SL,WI</sub>     | V <sub>WI</sub> = 0 V                                          | 1                            | _    | 0.1                       | μΑ   | 11              |

| Watchdog output voltage "H"             | V <sub>WOH</sub>       | -                                                              | V <sub>OUT(S)</sub><br>× 0.9 | -    | ı                         | ٧    | 7               |

| Watchdog output voltage "L"             | V <sub>WOL</sub>       | $R_{\text{extW}} \ge 3 \text{ k}\Omega,$ Connected to VOUT pin | -                            | 0.2  | 0.4                       | ٧    | 7               |

| Watchdog pull-up resistance             | Rwo                    | VOUT pin internal resistance, Vouт ≥ +VDET                     | 20                           | 30   | 45                        | kΩ   | _               |

| Watchdog output current                 | Iwo                    | $V_{WO} = 0.4 \text{ V},$ $V_{OUT} = -V_{DET(S)} \times 0.95$  | 3.0                          | _    | _                         | mA   | 12              |

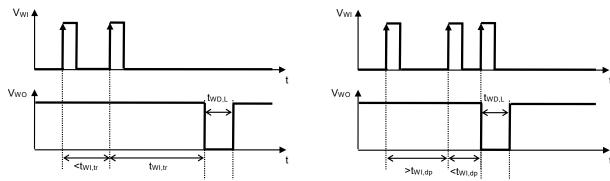

| Watchdog output "L" time*1              | t <sub>WD,L</sub>      | C <sub>DLY</sub> = 10 nF                                       | 9.2                          | 11.5 | 13.8                      | ms   | 9               |

| Watchdog trigger time*2                 | t <sub>WI,tr</sub>     | C <sub>DLY</sub> = 10 nF                                       | 39.1                         | 46   | 52.9                      | ms   | 9               |

| Watchdog double-pulse detection time*3  | t <sub>WI,dp</sub>     | C <sub>DLY</sub> = 10 nF                                       | 9.2                          | 11.5 | 13.8                      | ms   | 9               |

- \*1. The time when the WO pin continues "L" after the watchdog timer detects a time-out or double-pulse (Refer to Figure 11). This value changes according to C<sub>DLY</sub>.

- \*2. The time from when the watchdog timer initiates the detection of a trigger signal to when a time-out is detected and the WO pin output changes to "L" (Refer to Figure 11). This value changes according to C<sub>DLY</sub>.

- \*3. The time from when the watchdog timer initiates the detection of a trigger signal to when a trigger is detected again before twi,dp elapses and the WO pin output changes to "L" (Refer to Figure 12. This value changes according to CDLY.

Figure 11 Watchdog Trigger Time

Figure 12 Watchdog Double-pulse Detection Time

### 4. Overall

Table 16

( $V_{IN}$  = 13.5 V,  $T_j$  = -40°C to +150°C unless otherwise specified)

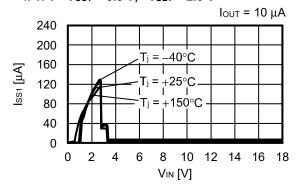

| Item                                 | Symbol           | Condition                                                                                                                                      | Min. | Тур. | Max. | Unit | Test<br>Circuit |

|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-----------------|

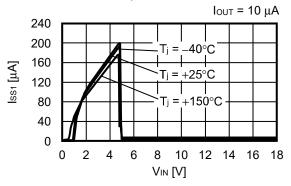

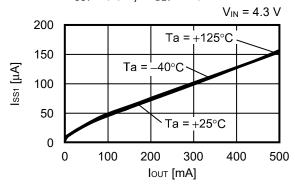

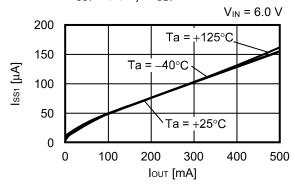

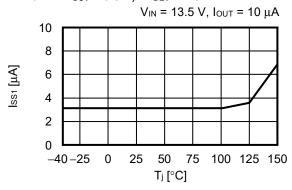

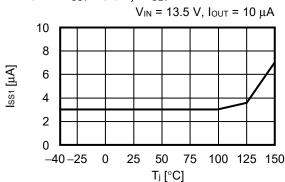

|                                      |                  | V <sub>EN</sub> = V <sub>IN</sub> , I <sub>OUT</sub> ≤ 10 μA,<br>during watchdog timer deactivation                                            | _    | 3.2  | 9.8  | μΑ   | 9               |

| Current consumption                  | Iss <sub>1</sub> | S-19519A Series,<br>$V_{EN} = V_{IN}, I_{OUT} \le 2.5 \text{ mA},$<br>during watchdog timer activation,<br>WO / RO pin = "H"                   | -    | 8.4  | 18   | μА   | 9               |

| during operation                     |                  | S-19519B Series, $V_{EN} = V_{IN}, \ I_{OUT} \leq 2.5 \ mA,$ during watchdog timer activation, WADJ pin is connected to VOUT pin, WO pin = "H" | -    | 8.4  | 18   | μА   | 9               |

| Current consumption during power-off | Iss2             | V <sub>EN</sub> = 0 V, I <sub>OUT</sub> = 0 mA                                                                                                 | _    | 0.1  | 4.0  | μΑ   | 10              |

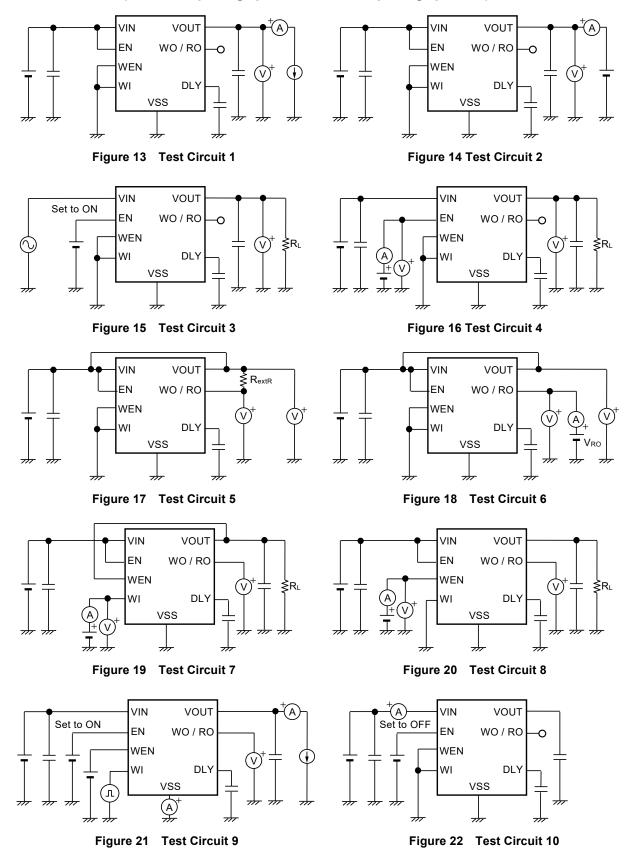

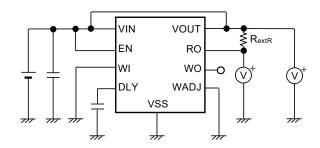

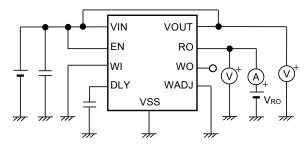

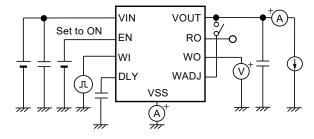

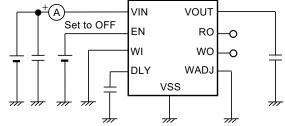

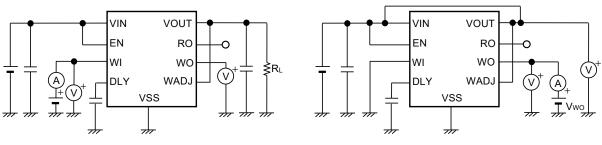

### **■ Test Circuits**

### 1. S-19519A Series (TO-252-9S package product, HSOP-8A package product)

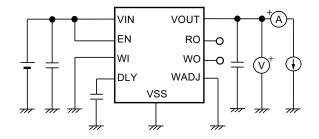

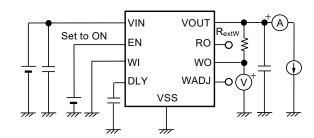

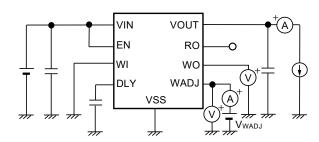

# 2. S-19519B Series (HTSSOP-16 package product)

Figure 23 Test Circuit 1

Figure 24 Test Circuit 2

VIN VOUT Set to ON ΕN RO WI WO 0 DLY WADJ VSS

Figure 25 Test Circuit 3

Figure 26 Test Circuit 4

Figure 27 Test Circuit 5

Figure 28 Test Circuit 6

Figure 29 Test Circuit 7

Figure 30 Test Circuit 8

Figure 31 Test Circuit 9

Figure 32 Test Circuit 10

Figure 33 Test Circuit 11

Figure 34 Test Circuit 12

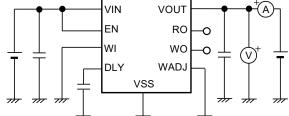

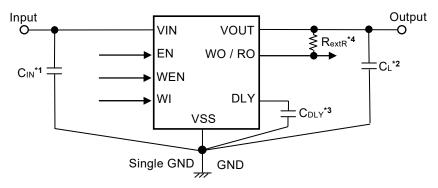

### ■ Standard Circuits

### 1. S-19519A Series (TO-252-9S package product, HSOP-8A package product)

Figure 35

- \*1. C<sub>IN</sub> is a capacitor for stabilizing the input.

- \*2. C<sub>L</sub> is a capacitor for stabilizing the output.

- \*3. CDLY is the release delay time and monitoring time adjustment capacitor.

- **\*4.** Connection of the external pull-up resistor is not absolutely essential since the S-19519 Series has a built-in pull-up resistor.

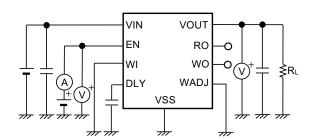

### 2. S-19519B Series (HTSSOP-16 package product)

Figure 36

- \*1. C<sub>IN</sub> is a capacitor for stabilizing the input.

- \*2. C<sub>L</sub> is a capacitor for stabilizing the output.

- \*3. C<sub>DLY</sub> is the release delay time and monitoring time adjustment capacitor.

- **\*4.** R<sub>WADJ,ext</sub> is the watchdog activation threshold current adjustment resistor.

- \*5. R<sub>extR</sub> and R<sub>extW</sub> are the external pull-up resistors for the reset output pin and the watchdog output pin, respectively. Connection of the external pull-up resistor is not absolutely essential since the S-19519 Series has a built-in pull-up resistor.

Caution The above connection diagram and constants will not guarantee successful operation. Perform thorough evaluation using an actual application to set the constants.

### ■ Selection of External Parts

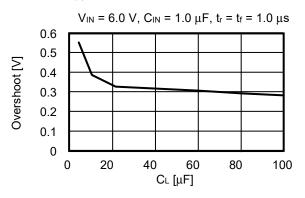

### 1. Input and output capacitors (CIN, CL)

The S-19519 Series requires  $C_L$  between the VOUT pin and the VSS pin for phase compensation. Operation is stabilized by a ceramic capacitor with an output capacitance of 1.0  $\mu F$  or more over the entire temperature range. When using an OS capacitor, a tantalum capacitor, or an aluminum electrolytic capacitor, the capacitance must be 1.0  $\mu F$  or more, and the ESR must be 100  $\Omega$  or less.

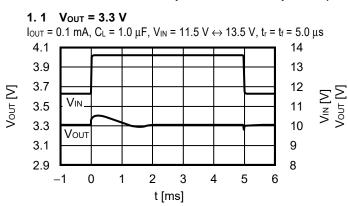

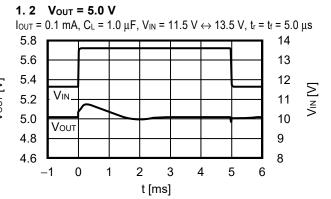

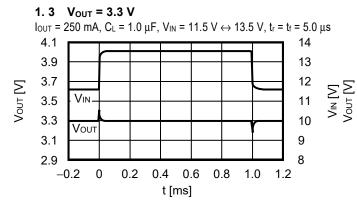

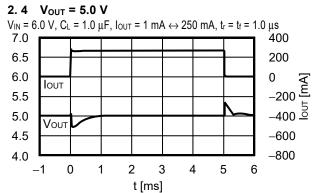

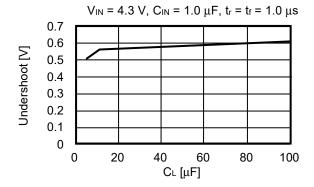

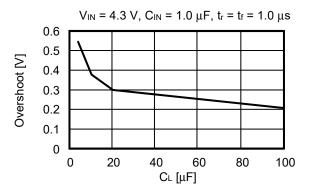

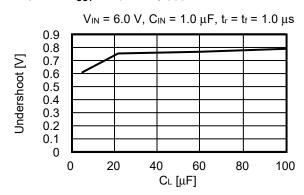

The values of output overshoot and undershoot, which are transient response characteristics, vary depending on the value of the output capacitor.

The required value of capacitance for the input capacitor differs depending on the application.

Caution Define the capacitance of C<sub>IN</sub> and C<sub>L</sub> by sufficient evaluation including the temperature characteristics under the actual usage conditions.

### 2. Release delay time and monitoring time adjustment capacitor (CDLY)

In the S-19519 Series, the release delay time and monitoring time adjustment capacitor ( $C_{DLY}$ ) is necessary between the DLY pin and the VSS pin to adjust the release delay time ( $t_{rd}$ ) of the detector and the monitoring time of the watchdog timer.

The set release delay time  $(t_{rd(S)})$ , the set watchdog trigger time  $(t_{Wl,tr(S)})$ , the set watchdog output "L" time  $(t_{WD,L(S)})$  and the set watchdog double-pulse detection time  $(t_{Wl,dp(S)})$  are calculated by using following equations, respectively. The release delay time  $(t_{rd})$ , the watchdog trigger time  $(t_{Wl,tr})$ , the watchdog output "L" time  $(t_{WD,L})$  and the watchdog double-pulse detection time  $(t_{Wl,dp})$  at the time of the condition of  $C_{DLY} = 10$  nF are shown in "**Electrical Characteristics**".

$$\begin{split} t_{rd(S)}\left[ms\right] &= t_{rd}\left[ms\right] \times \frac{C_{DLY}\left[nF\right]}{10\left[nF\right]} \\ t_{WI,tr(S)}\left[ms\right] &= t_{WI,tr}\left[ms\right] \times \frac{C_{DLY}\left[nF\right]}{10\left[nF\right]} \\ t_{WD,L(S)}\left[ms\right] &= t_{WD,L}\left[ms\right] \times \frac{C_{DLY}\left[nF\right]}{10\left[nF\right]} \\ t_{WI,dp(S)}\left[ms\right] &= t_{WI,dp}\left[ms\right] \times \frac{C_{DLY}\left[nF\right]}{10\left[nF\right]} \end{split}$$

- Caution 1. The above equations will not guarantee successful operation. Perform thorough evaluation including the temperature characteristics using an actual application to set the constants.

- 2. Mounted board layout should be made in such a way that no current flows into or flows from the DLY pin since the impedance of the DLY pin is high, otherwise correct delay time and monitoring time may not be provided.

- Select C<sub>DLY</sub> whose leakage current can be ignored against the built-in constant current (0.6 μA typ.).

The leakage current may cause deviation in delay time and monitoring time. When the leakage current is larger than the built-in constant current, no release takes place.

- 4. Deviations of C<sub>DLY</sub> are not included in the equations mentioned above. Be sure to determine the constants considering the deviation of C<sub>DLY</sub> to be used.

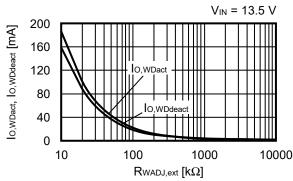

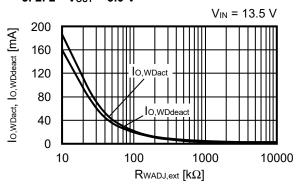

# 3. Watchdog activation threshold current adjustment resistor (Rwaddl,ext)

In the S-19519B Series, the watchdog activation threshold current adjustment resistor (Rwaddlext) can be connected between the WADJ pin and the VSS pin to adjust the watchdog timer activation threshold current.

The set watchdog activation threshold current  $(I_{O,WDact(S)})$ , the set watchdog deactivation threshold current  $(I_{O,WDdeact(S)})$  and the set watchdog activation hysteresis current  $(I_{O,WDhys(s)})$  are calculated by using following equations, respectively.

The watchdog activation threshold current (Io,wDact), the watchdog deactivation threshold current (Io,wDdeact) and the watchdog activation hysteresis current (Io,wDhys) when the WADJ pin is open are shown in "■ Electrical Characteristics".

$$\begin{split} &I_{\text{O,WDact(S)}}\left[mA\right] = I_{\text{O,WDact}}\left[mA\right] \times \left(1 + \frac{R_{\text{WADJ,int}}\left[k\Omega\right]}{R_{\text{WADJ,ext}}\left[k\Omega\right]}\right) \\ &I_{\text{O,WDdeact(S)}}\left[mA\right] = I_{\text{O,WDdeact}}\left[mA\right] \times \left(1 + \frac{R_{\text{WADJ,int}}\left[k\Omega\right]}{R_{\text{WADJ,ext}}\left[k\Omega\right]}\right) \end{split}$$

$I_{O,WDhys(S)}$  [mA] =  $I_{O,WDact(S)}$  [mA] -  $I_{O,WDdeact(S)}$  [mA]

Caution 1. The above equations will not guarantee successful operation. Perform thorough evaluation including the temperature characteristics using an actual application to set the constants.

- 2. Mounted board layout should be made in such a way that no current flows into or flows from the WADJ pin since the impedance of the WADJ pin is high, otherwise correct Io,wDact and Io,wDdeact may not be provided.

- 3. Refer to "3. 2. 2 Autonomous watchdog operation function (Output current detection circuit)" in "■ Operation" for the details.

# ■ Operation

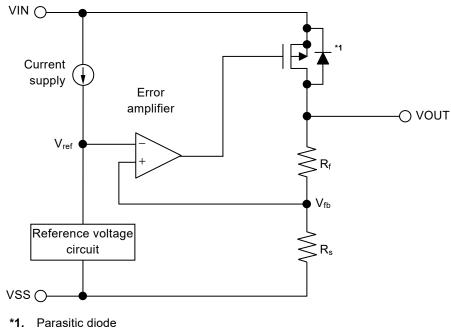

### 1. Regulator block

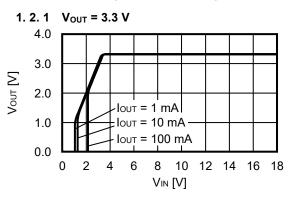

#### 1.1 Basic operation

Figure 37 shows the block diagram of the regulator in the S-19519 Series.

The error amplifier compares the reference voltage ( $V_{ref}$ ) with feedback voltage ( $V_{fb}$ ), which is the output voltage resistance-divided by feedback resistors ( $R_s$  and  $R_f$ ). It supplies the gate voltage necessary to maintain the constant output voltage which is not influenced by the input voltage and temperature change, to the output transistor.

Figure 37

## 1. 2 Output transistor

In the S-19519 Series, a low on-resistance P-channel MOS FET is used as the output transistor.

Be sure that  $V_{\text{OUT}}$  does not exceed  $V_{\text{IN}} + 0.3$  V to prevent the voltage regulator from being damaged due to reverse current flowing from the VOUT pin through a parasitic diode to the VIN pin, when the potential of  $V_{\text{OUT}}$  became higher than  $V_{\text{IN}}$ .

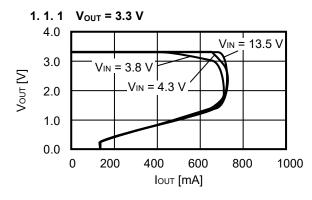

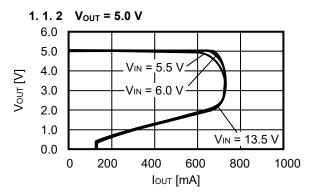

#### 1. 3 Overcurrent protection circuit

The S-19519 Series includes an overcurrent protection circuit which having the characteristics shown in "1. 1 Output voltage vs. Output current (When load current increases) (Ta = +25°C)" of "1. Regulator block" in "■ Characteristics (Typical Data)", in order to limit an excessive output current and overcurrent of the output transistor due to short-circuiting between the VOUT pin and the VSS pin. The current when the output pin is short-circuited (I<sub>short</sub>) is internally set at 160 mA typ., and the load current when short-circuiting is limited based on this value. The output voltage restarts regulating if the output transistor is released from overcurrent status.

Caution This overcurrent protection circuit does not work as for thermal protection. If this IC long keeps short circuiting, pay attention to the conditions of input voltage and load current so that, under the usage conditions including short circuit, the loss of the IC will not exceed power dissipation.

#### 1. 4 Thermal shutdown circuit

The S-19519 Series has a thermal shutdown circuit to limit self-heating. When the junction temperature rises to 170°C typ., the thermal shutdown circuit operates to stop regulating. After that, when the junction temperature drops to 135°C typ., the thermal shutdown circuit is released to restart regulating.

Due to self-heating of the S-19519 Series, if the thermal shutdown circuit starts operating, it stops regulating so that the output voltage drops. For this reason, self-heating is limited and the IC's temperature drops.

When the temperature drops, the thermal shutdown circuit is released to restart regulating, thus self-heating is generated again due to rising of the output voltage. Repeating this procedure makes the waveform of the VOUT pin output into a pulse-like form. This phenomenon continues unless decreasing either or both of the input voltage and the output current in order to reduce the internal power consumption, or decreasing the ambient temperature. Note that the product may suffer physical damage such as deterioration if the above phenomenon occurs continuously.

Table 17

| Thermal Shutdown Circuit | VOUT Pin Voltage      |

|--------------------------|-----------------------|

| Detect: 170°C typ.*1     | V <sub>SS</sub> level |

| Release: 135°C typ.*1    | Set value             |

<sup>\*1.</sup> Junction temperature

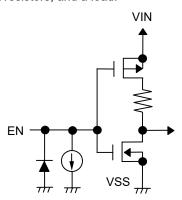

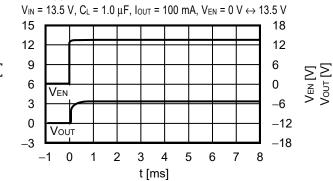

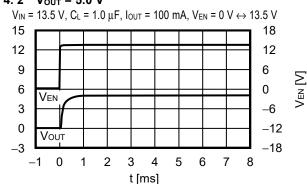

#### 1. 5 ON / OFF circuit

The ON / OFF circuit controls the internal circuit and the output transistor in order to start and stop the regulator. When the EN pin is set to "L" (OFF), the internal circuit stops operating and the output transistor between the VIN pin and the VOUT pin is turned off, reducing current consumption significantly.

The internal equivalent circuit related to the EN pin is configured as shown in **Figure 38**. Since the EN pin is internally pulled down by the constant current source, the EN pin is set to "L" if it is used in the floating status, and the output transistor is turned off. However, in order that the EN pin becomes OFF certainly, connect the EN pin to GND so that "L" is certainly input to the EN pin, since the impedance of the EN pin becomes high when using the EN pin in the floating status.

When not using the EN pin, connect it to the VIN pin. Note that the current consumption increases when an intermediate voltage is applied to the EN pin.

| Ta | bl | le | 1 | 8 |

|----|----|----|---|---|

|----|----|----|---|---|

| EN Pin   | Internal Circuit | VOUT Pin Voltage                  | Current Consumption |

|----------|------------------|-----------------------------------|---------------------|

| "H": ON  | Operate          | Constant value*1                  | Iss <sub>1</sub>    |

| "L": OFF | Stop             | Pulled down to V <sub>SS</sub> *2 | I <sub>SS2</sub>    |

<sup>\*1.</sup> The constant value is output due to the regulating based on the set output voltage value.

<sup>\*2.</sup> The VOUT pin voltage is pulled down to  $V_{SS}$  due to combined resistance ( $R_{LOW}$  = 1.2 k $\Omega$  typ.) of the discharge shunt circuit and the feedback resistors, and a load.

Figure 38

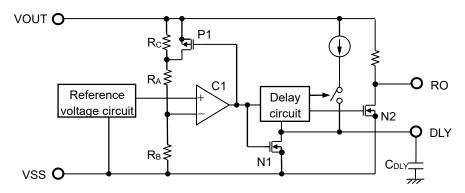

#### 2. Detector block

#### 2. 1 Basic operation

- (1) When the output voltage (V<sub>OUT</sub>) of the regulator is release voltage (+V<sub>DET</sub>) of the detector or higher, the Nch transistor (N1 and N2) are turned off and "H" is output to the RO pin. Since the Pch transistor (P1) is turned on, the input voltage to the comparator (C1) is R<sub>B</sub> V<sub>OUT</sub>/R<sub>A</sub> + R<sub>B</sub>.

- (2) Even if  $V_{OUT}$  decreases to  $+V_{DET}$  or lower, "H" is output to the RO pin when  $V_{OUT}$  is the detection voltage  $(-V_{DET})$  or higher. When  $V_{OUT}$  decreases to  $-V_{DET}$  (point A in **Figure 40**) or lower, N1 which is controlled by C1 is turned on, and  $C_{DLY}$  is discharged. At the same time, N2, which is controlled by the delay circuit, is turned on, and "L" is output to the RO pin. At this time, P1 is turned off, and the input voltage to C1 is  $\frac{R_B \bullet V_{OUT}}{R_A + R_B + R_C}$ .

- (3) If  $V_{OUT}$  further decreases to the IC's minimum operation voltage or lower, the RO pin output becomes uncertain. If the RO pin is pulled up, "H" is output.

- (4) When  $V_{OUT}$  increases to the IC's minimum operation voltage or higher, "L" is output to the RO pin. Moreover, even if  $V_{OUT}$  exceeds  $-V_{DET}$ , the output is "L" when  $V_{OUT}$  is lower than  $+V_{DET}$ .

- (5) When V<sub>OUT</sub> increases to +V<sub>DET</sub> (point B in **Figure 40**) or higher, N1 is turned off and C<sub>DLY</sub> is charged. When V<sub>DLY</sub> increases to the threshold voltage (1.25 V typ.), N2, which is controlled by a delay circuit, is turned off and "H" is output to the RO pin.

Figure 39 Operation of Detector Block

Figure 40 Timing Chart of Detector Block

#### 2. 2 Delay circuit

When the output voltage  $(V_{OUT})$  of the regulator rises under the status that "L" is output to the RO pin, the reset release signal is output to the RO pin later than when  $V_{OUT}$  becomes  $+V_{DET}$ . The release delay time  $(t_{rd})$  changes according to  $C_{DLY}$ . Refer to "2. Release delay time and monitoring time adjustment capacitor  $(C_{DLY})$ " in "Selection of External Parts" for details.

In addition, if the time from when  $V_{OUT}$  decreases to  $-V_{DET}$  or lower to when  $V_{OUT}$  increases to  $+V_{DET}$  or higher is significantly shorter compared to the length of the reset reaction time ( $t_{rr}$ ), "H" output may remain in the RO pin.

Caution Since t<sub>rd</sub> depends on the charge time of C<sub>DLY</sub>, t<sub>rd</sub> may be shorter than the set value if the charge operation is initiated under the condition that a residual electric charge is left in C<sub>DLY</sub>.

### 2. 3 Output circuit

Since the RO pin has a built-in resistor to pull up to the VOUT pin internally, the RO pin can output a signal without an external pull-up resistor

Do not connect to the pin other than VOUT pin when connecting an external pull-up resistor.

In the S-19519A Series, the reset output pin and the watchdog output pin are prepared as the WO / RO pin.

The output level of the WO / RO pin is applied by the AND logic of the reset output pin and the watchdog output pin.

Example: When the WO pin is "L" and the RO pin is "H", the WO / RO pin is "L".

Caution Define the external pull-up resistance by sufficient evaluation including the temperature characteristics under the actual usage conditions.

### 3. Watchdog timer block

#### 3. 1 S-19519A Series (TO-252-9S package product, HSOP-8A package product)

#### 3. 1. 1 Basic operation

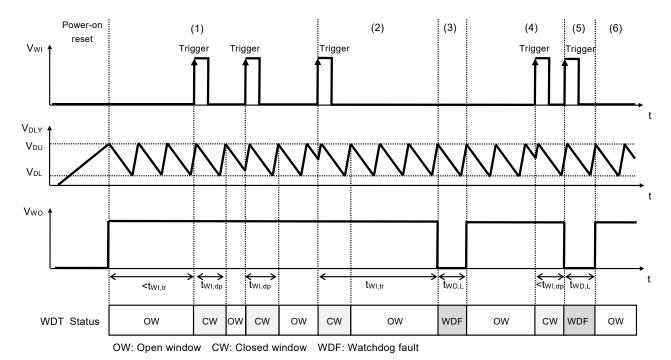

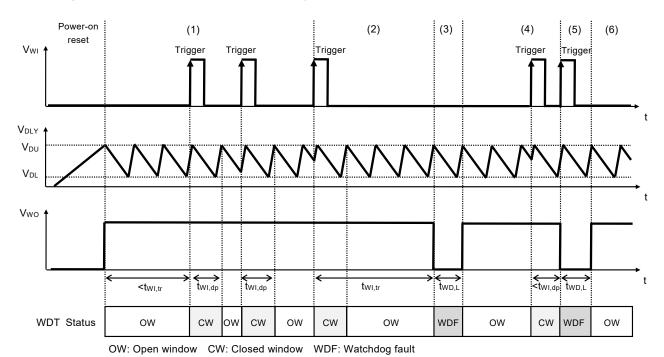

The watchdog timer operates as follows during monitoring operation.

- (1) When the watchdog timer starts monitoring operation, it enters the Open window status, and C<sub>DLY</sub> charge-discharge operation is carried out by an internal constant current source. If a rising edge is input to the WI pin in the Open window status, the watchdog timer detects a trigger, and switches to the Closed window status. If a trigger is not detected in the Closed window status, the C<sub>DLY</sub> charge-discharge operation is carried out and if the watchdog double-pulse detection time (t<sub>WI,dp</sub>) is exceeded, the watchdog timer switches to the Open window status. If the watchdog timer again detects a trigger in the Open window status, it switches to the Closed window status. During this time, the WO pin outputs "H". In order to verify the normal operation of the object being monitored, input a rising edge to the WI pin in the Open window status, and do not input a rising edge in the Closed window status.

- (2) While no triggers are detected in the Open window status, the C<sub>DLY</sub> charge-discharge operation is repeated, and once the watchdog trigger time (t<sub>Wl,tr</sub>) elapses after monitoring has started or after the last trigger was detected, the watchdog timer switches to the Watchdog fault status, and the WO pin outputs "L". This operation is called a "time-out detection". If the watchdog timer is deactivated while the WO pin is outputting "H", the number of charges and discharges and t<sub>Wl,tr</sub> elapsed time are reset.

- (3) After a time-out detection, C<sub>DLY</sub> charge-discharge operation is carried out while the WO pin outputs "L" in the Watchdog fault status. After the watchdog output "L" time (t<sub>WD,L</sub>) has elapsed, the watchdog timer switches to the Open window status and the WO pin outputs "H". Even if the watchdog timer is deactivated while the WO pin is outputting "L", the WO pin continues to output "L" until the t<sub>WD,L</sub> has elapsed.

- (4) If the watchdog timer detects a trigger in the Open window status, switching to the Closed window status, a trigger is detected again before the twi,dp elapses, the watchdog timer switches to the Watchdog fault status, and the WO pin outputs "L". This operation is called a "double-pulse detection".

- (5) After a double-pulse detection, CDLY charge-discharge operation is carried out while the WO pin outputs "L" in the Watchdog fault status. As with the case of (3), when twp,L elapses, the watchdog timer switches to the Open window status and the WO pin outputs "H".

- (6) After the watchdog timer reverts back to the Open window status from the Watchdog fault status, operation (1), (2), or (4) is continually carried out depending on input.

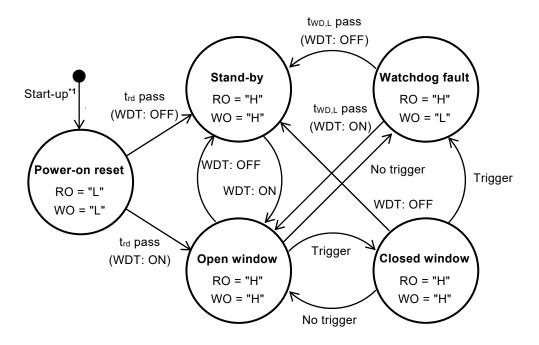

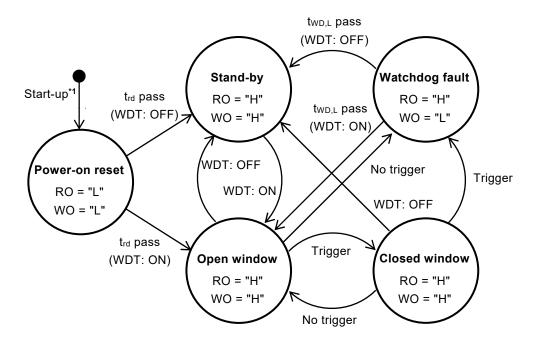

Refer to Figure 41 for the status transition of watchdog timer block.

Figure 41 Timing Chart of Watchdog Timer Block

Figure 42 Status Transition of Watchdog Timer Block

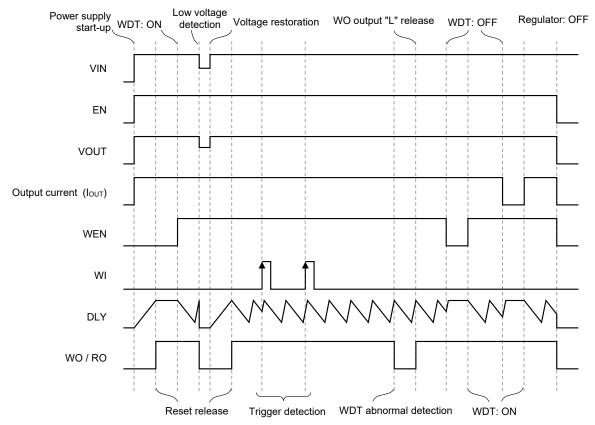

\*1. If the detector block detects low voltage as a result of  $V_{OUT}$  dropping below the detection voltage ( $-V_{DET}$ ), the watchdog timer resets to the initial status. If  $V_{OUT}$  is restored and exceeds the release voltage ( $+V_{DET}$ ), the watchdog timer is activated and switches to the Power-on reset status.

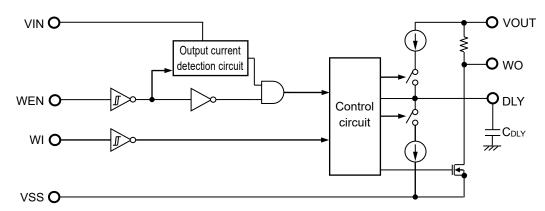

Figure 43 Operation of Watchdog Timer Block

### 3. 1. 2 Autonomous watchdog operation function (Output current detection circuit)

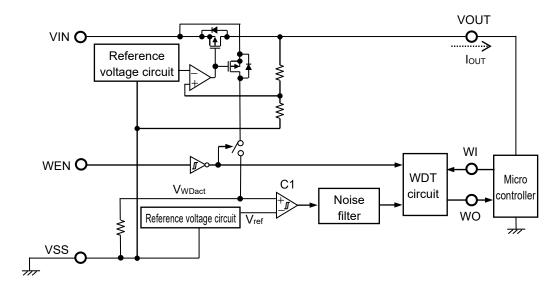

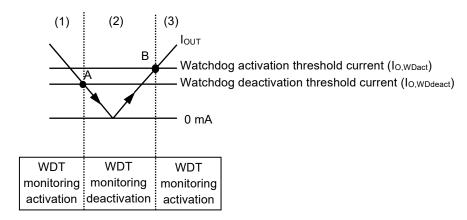

Since the S-19519A Series has a built-in output current detection circuit, the watchdog timer operates autonomously. The current flows in the load is detected by the output current of the regulator, the watchdog timer initiates the activation when the output current is the watchdog activation threshold current (Io,WDact) or more, the watchdog timer is deactivated when the output current is the watchdog deactivation threshold current (Io,WDdeact) or less.

Figure 44 shows a block diagram which includes an output current detection circuit. If the regulator is connected to a microcontroller, the microcontroller operation current can be detected using the regulator output current. For example, if the microcontroller sleep operation current is lower than the watchdog deactivation threshold current (Io,wDdeact), the watchdog timer autonomously deactivates monitoring operation when the microcontroller sleeps. If the VIN pin voltage drops below the output current detection circuit minimum operation voltage, the output current detection circuit stops the operation. Refer to "■ Recommended Operation Conditions" for VIN pin voltage range.

In addition, in the S-19519A Series, if the watchdog timer is disabled using the WEN pin, the watchdog timer is deactivated regardless of the output current.

Figure 44 Operation of Output Current Detection Circuit

Caution Microcontroller is not built-in in the S-19519A Series. In addition, the above connection diagram will not guarantee successful operation. Perform thorough evaluation using the actual application to determine connections.

Since the S-19519A Series has the autonomous watchdog operation function, the watchdog timer monitoring activation is as follows.

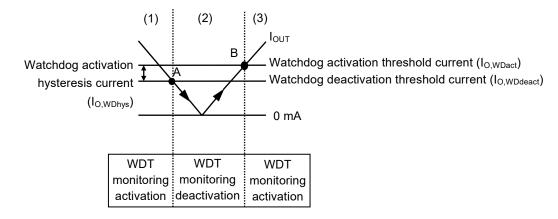

- (1) When I<sub>OUT</sub> of the regulator is the watchdog activation threshold current (I<sub>O,WDact</sub>) or more, the input voltage (V<sub>WDact</sub>) of comparator (C1) is higher than the reference voltage (V<sub>ref</sub>), and the output of C1 is "H". At this time, the watchdog timer activated.

- (2) When I<sub>OUT</sub> decreases to the watchdog deactivation threshold current (I<sub>O,WDdeact</sub>) (point A in **Figure 45**) or less, V<sub>WDact</sub> decreases to V<sub>ref</sub> or less and the output of C1 is "L". At this time, the watchdog timer deactivates the monitoring. Even if I<sub>OUT</sub> increases, the watchdog timer continues the monitoring deactivation when I<sub>OUT</sub> is within less than I<sub>O,WDact</sub>

- (3) If I<sub>OUT</sub> further increases to I<sub>O,WDact</sub> (point B in **Figure 45**) or more, V<sub>WDact</sub> increases to V<sub>ref</sub> or higher and the output of C1 is "H". And then, the watchdog timer initiates the monitoring activation.

Figure 45 Autonomous Watchdog Operation Function

Caution If the output current of regulator transiently changes, the monitoring activation of watchdog timer may become unstable, resulting in switching between activation and deactivation. Regarding the activation at that time, perform thorough evaluation using an actual application.

#### 3. 1. 3 Watchdog enable circuit

When inputting "L" to the WEN pin, the watchdog timer becomes Disable and stops the output current detection operation and monitoring activation. When inputting "H" to the WEN pin, the watchdog timer becomes Enable. The WEN pin is pulled down internally by the constant current source. For this reason, the WEN pin is set to "L" when using the WEN pin in the floating status, and the watchdog timer becomes Disable. However, in order that the watchdog timer becomes Disable certainly, connect the WEN pin to GND so that "L" is input to the WEN pin certainly, since the impedance of the WEN pin becomes high when using the WEN pin in the floating status. In order to fix the watchdog timer to Enable, connect the WEN pin to the VOUT pin so that "H" is input to the WEN pin.

Table 19 shows the relation between each pin status and the watchdog timer monitoring operation.

|            |                  | Table 19           |                          |

|------------|------------------|--------------------|--------------------------|

| WEN Pin    | Output Current*1 | VOUT Pin Voltage   | WDT Monitoring Operation |

| "H"        | "H"              | ≥+V <sub>DET</sub> | ON                       |

| "H"        | "L"              | ≥+V <sub>DET</sub> | OFF                      |

| "L"        | Don't care       | ≥+V <sub>DET</sub> | OFF                      |

| Don't care | Don't care       | ≤-V <sub>DET</sub> | OFF                      |

<sup>\*1. &</sup>quot;H": IOUT > IO,WDact, "L": IOUT < IO,WDdeact

#### 3. 2 S-19519B Series (HTSSOP-16 package product)

#### 3. 2. 1 Basic operation

The watchdog timer operates as follows during monitoring operation.

- (1) When the watchdog timer starts monitoring operation, it enters the Open window status, and C<sub>DLY</sub> charge-discharge operation is carried out by an internal constant current source. If a rising edge is input to the WI pin in the Open window status, the watchdog timer detects a trigger, and switches to the Closed window status. If a trigger is not detected in the Closed window status, the C<sub>DLY</sub> charge-discharge operation is carried out and if the watchdog double-pulse detection time (t<sub>WI,dp</sub>) is exceeded, the watchdog timer switches to the Open window status. If the watchdog timer again detects a trigger in the Open window status, it switches to the Closed window status. During this time, the WO pin outputs "H". In order to verify the normal operation of the object being monitored, input a rising edge to the WI pin in the Open window status, and do not input a rising edge in the Closed window status.

- (2) While no triggers are detected in the Open window status, the C<sub>DLY</sub> charge-discharge operation is repeated, and once the watchdog trigger time (twi,tr) elapses after monitoring has started or after the last trigger was detected, the watchdog timer switches to the Watchdog fault status, and the WO pin outputs "L". This operation is called a "time-out detection". If the watchdog timer is deactivated while the WO pin is outputting "H", the number of charges and discharges and twi,tr elapsed time are reset.

- (3) After a time-out detection, C<sub>DLY</sub> charge-discharge operation is carried out while the WO pin outputs "L" in the Watchdog fault status. After the watchdog output "L" time (t<sub>WD,L</sub>) has elapsed, the watchdog timer switches to the Open window status and the WO pin outputs "H". Even if the watchdog timer is deactivated while the WO pin is outputting "L", the WO pin continues to output "L" until the t<sub>WD,L</sub> has elapsed.

- (4) If the watchdog timer detects a trigger in the Open window status, switching to the Closed window status, a trigger is detected again before the t<sub>WI,dp</sub> elapses, the watchdog timer switches to the Watchdog fault status, and the WO pin outputs "L". This operation is called a "double-pulse detection".

- (5) After a double-pulse detection, CDLY charge-discharge operation is carried out while the WO pin outputs "L" in the Watchdog fault status. As with the case of (3), when two,L elapses, the watchdog timer switches to the Open window status and the WO pin outputs "H".

- (6) After the watchdog timer reverts back to the Open window status from the Watchdog fault status, operation (1), (2), or (4) is continually carried out depending on input.

Refer to Figure 46 for the status transition of watchdog timer block.

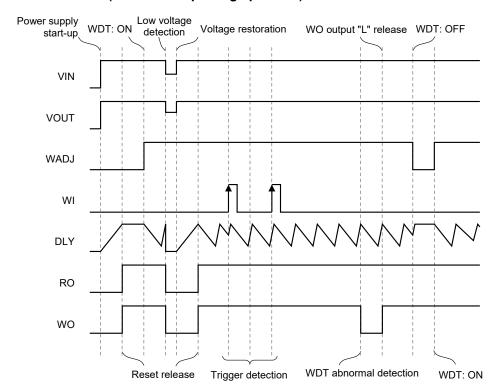

Figure 46 Timing Chart of Watchdog Timer Block

Figure 47 Status Transition of Watchdog Timer Block

\*1. If the detector block detects low voltage as a result of  $V_{OUT}$  dropping below the detection voltage ( $-V_{DET}$ ), the watchdog timer resets to the initial status. If  $V_{OUT}$  is restored and exceeds the release voltage ( $+V_{DET}$ ), the watchdog timer is activated and switches to the Power-on reset status.

Figure 48 Operation of Watchdog Timer Block

#### 3. 2. 2 Autonomous watchdog operation function (Output current detection circuit)

Since the S-19519B Series has a built-in output current detection circuit, the watchdog timer operates autonomously. When using the autonomous watchdog operation function, the current flows in the load is detected by the output current of the regulator, the watchdog timer initiates the activation when the output current is the watchdog activation threshold current (Io,wDact) or more, the watchdog timer is deactivated when the output current is the watchdog deactivation threshold current (Io,wDdeact) or less.

Table 20 shows the connection of WADJ pin depending on the usage of the watchdog timer.

| Table 20 |

|----------|

|----------|

| Usage of Watchdog Timer                                                                                             | Connection of WADJ Pin                                    | Status of WADJ Pin                                                                          |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Watchdog timer is not in use                                                                                        | Connect to the VSS pin                                    | "L"                                                                                         |

| Watchdog timer is always activated                                                                                  | Connect to the VOUT pin                                   | "H"                                                                                         |

| Watchdog timer turns on and off autonomously depending on the load current (Autonomous watchdog operation function) | Open or connect to the VSS pin via an external resistor*1 | "H": I <sub>OUT</sub> > I <sub>O,WDact</sub> "L": I <sub>OUT</sub> < I <sub>O,WDdeact</sub> |

\*1. Refer to "3. Watchdog activation threshold current adjustment resistor (Rwaddl,ext)" in "■ Selection of External Parts" for details.

**Figure 49** shows a block diagram which includes an output current detection circuit. It shows the connection of each pin when using the autonomous watchdog operation function. If the regulator is connected to a microcontroller, the microcontroller operation current can be detected using the regulator output current. For example, if a constant of the watchdog activation threshold current adjustment resistor (Rwaddlest) is selected so that the microcontroller sleep operation current is lower than the watchdog deactivation threshold current (Io,wdeact), when the microcontroller sleeps, the watchdog timer autonomously deactivates monitoring operation. If a device other than a microcontroller is connected to the VOUT pin, take the connected device's current consumption into account when selecting Rwaddlest.

If the VIN pin voltage drops below the output current detection circuit minimum operation voltage, the output current detection circuit stops the operation. Refer to **TERCOMMENDED** Recommended Operation Conditions for VIN pin voltage range.

Figure 49 Operation of Output current Detection Circuit

Caution Rwaddl,ext and microcontroller are not built-in in the S-19519B Series. In addition, the above connection diagram will not guarantee successful operation. Perform thorough evaluation using the actual application to determine connections.

In the S-19519B Series, when using the autonomous watchdog operation function, the watchdog timer monitoring activation is as follows.